10

15

20

25

Изобретение относится к электросвязи и может быть использовано при передаче дискретной информации для циклового фазирования многоканальной аппаратуры, в которой используется временное разделение каналов и последовательный поиск синхрокомбинации.

Цель изобретения - повьшение точности синхронизации путем контроля установления синхронизма при приеме контрольной информации без увеличения времени вхождения в синхронизм.

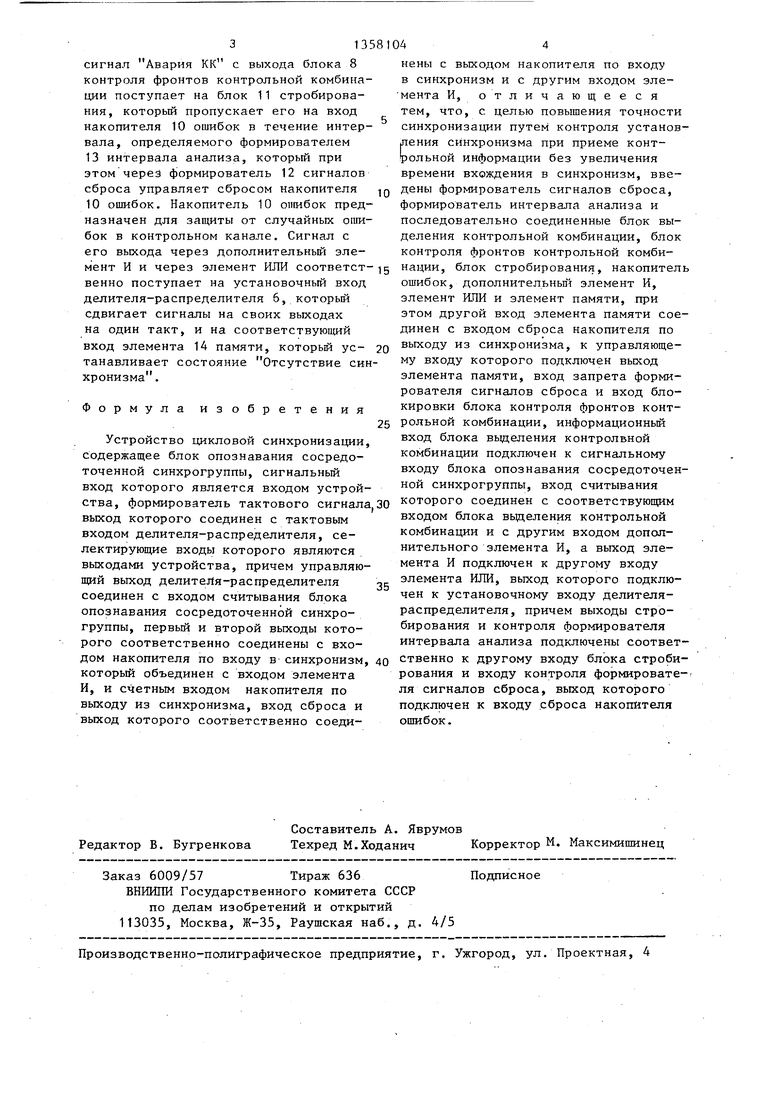

На чертеже представлена структурная функциональная схема устройства цикловой синхронизации.

Устройство цикловой синхронизации содержит блок 1 опознавания сосредоточенной синхрогруппы, накопитель 2 по выходу из синхронизма, накопитель 3 по входу в синхронизм, элемент И 4, элемент ИЛИ 5, делитель-распределитель 6, блок 7 выделения контрольной комбинации, блок 8 контроля фронтов контрольной комбинации, дополнительный элемент И 9, накопитель 10 ошибок, блок 11 стробирования, формирователь 12 сигналов сброса, формирователь 13 интервала анализа, элемент 14 памяти и формирователь 15 тактового сигнала

Устройство цикловой синхронизации работает следующим образом.

Дискретная информация в виде двоичных сигналов поступает на сигнальный вход блока 1 опознавания сосредоточенной синхрогруппы, KOTOpbrii по каждому сигналу с управляющего выхода делителя-распределителя 6 анализирует наличие на соответствующей позиции цикла синхрогруппы. Если на анализи- 40 руемой позиции цикла синхрогруппа обнаружена, то с соответствующего выхода блока 1 опознавания сосредоточенной синхрогруппы логическая 1 записывается в накопитель 3 по входу в синхронизм, в противном случае логическая 1 записывается в накопитель 2 по выходу из синхронизма, по заполнении которого сигнал через элемент И 4 и элемент ИЛИ 5 поступает На установочный вход делителя-распределителя 6, который сдвигает сигналы на управляющем и селектирующих выходах на один такт, и на соответст30

35

45

50

хода блока 1 опознавания сосредоточенной синхрогруппы сигнал соответственно поступает на вход накопителя 3 по входу в синхронизм, которьй обнуляет свое значение, и на другой . вход элемента И 4, которьм пропускает сигнал с выхода накопителя 2 по выходу из синхронизма, по которому делитель-распределитель 6 каждый раз сдвигает сигналы на своих выходах на один такт. Если же синхрогруппа обнаруживается блоком 1 опознавания сосредоточенной синхрогруппы на одной и той же позиции цикла, то накопитель 3 по входу в синхронизм по соответствующим сигналам заполняет свое значение и сигнал с его выхода соответственно поступает на вход сброса накопителя 2 по выходу из синхронизма, который обнуляет свое значение, и другой вход элемента 14 памяти, который устанавливает состояние Синхронизм. При этом делитель-распределитель 6 фиксирует временное положение сигналов на своих выходах, которые он формирует из импульсов которые поступают с выхода формирователя 15 тактового сигнала.

В состоянии Отсутствие синхронизма элемент 14 памяти формирует сигнал, по которому накопитель 2 по выходу из синхронизма уменьшает свою емкость, а блок 8 контроля фронтов контрольной комбинации и накопитель 10 ошибок через формирователь 12 сигналов сброса прекращают работу на все

время поиска синхронизма. I

В состоянии Синхронизм элемент 14 памяти формирует сигнал, по которому разрешается анализировать информацию, передаваемую по контрольному каналу, наличие которого предусматривается при делении передаваемой дис- ;кретной информации и которому выделя- ется определенная позиция в цикле, отстоящая на известное число, обычно на половину позиций в цикле, от пози- иди, где находится синхрогруппа. Эта особенность учитывается при анализе информации контрольного канала с целью подтверждения истинности состояния Синхронизм, так как при ложном

вующий вход элемента 14 памяти, кото-gg состоянии Синхронизм блок 7 вьще- рьй уст анавливает состояние Отсутст- ления контрольной комбинации выделяет

вие синхронизма . Если на анализируемой позиции цикла синхрогруппа не обнаружена, то с соответствующего вы0

5

0

5

0

0

5

5

0

хода блока 1 опознавания сосредоточенной синхрогруппы сигнал соответственно поступает на вход накопителя 3 по входу в синхронизм, которьй обнуляет свое значение, и на другой . вход элемента И 4, которьм пропускает сигнал с выхода накопителя 2 по выходу из синхронизма, по которому делитель-распределитель 6 каждый раз сдвигает сигналы на своих выходах на один такт. Если же синхрогруппа обнаруживается блоком 1 опознавания сосредоточенной синхрогруппы на одной и той же позиции цикла, то накопитель 3 по входу в синхронизм по соответствующим сигналам заполняет свое значение и сигнал с его выхода соответственно поступает на вход сброса накопителя 2 по выходу из синхронизма, который обнуляет свое значение, и другой вход элемента 14 памяти, который устанавливает состояние Синхронизм. При этом делитель-распределитель 6 фиксирует временное положение сигналов на своих выходах, которые он формирует из импульсов которые поступают с выхода формирователя 15 тактового сигнала.

В состоянии Отсутствие синхронизма элемент 14 памяти формирует сигнал, по которому накопитель 2 по выходу из синхронизма уменьшает свою емкость, а блок 8 контроля фронтов контрольной комбинации и накопитель 10 ошибок через формирователь 12 сигналов сброса прекращают работу на все

время поиска синхронизма. I

В состоянии Синхронизм элемент 14 памяти формирует сигнал, по которому разрешается анализировать информацию, передаваемую по контрольному каналу, наличие которого предусматривается при делении передаваемой дис- ;кретной информации и которому выделя- ется определенная позиция в цикле, отстоящая на известное число, обычно на половину позиций в цикле, от пози- иди, где находится синхрогруппа. Эта особенность учитывается при анализе информации контрольного канала с целью подтверждения истинности состояния Синхронизм, так как при ложном

позиции в цикле, не соответствующие тем, на которых передается информация контрольного канала. В этом случае

313

сигнал Авария КК с выхода блока 8 контроля фронтов контрольной комбинации поступает на блок 11 стробирова- ния, который пропускает его на вход накопителя 10 ошибок в течение интервала, определяемого формирователем 13 интервала анализа, который при этом через формирователь 12 сигналов сброса управляет сбросом накопителя 10 ошибок. Накопитель 10 онмбок предназначен для защиты от случайных ошибок в контрольном канале. Сигнал с его выхода через дополнительный эле

мент И и через элемент ИЛИ соответст- д нации, блок стробирования, накопитель

венно поступает на установочный вход делителя-распределителя 5, который сдвигает сигналы на своих выходах на один такт, и на соответствующий вход элемента 14 памяти, который устанавливает состояние Отсутствие синхронизма.

Формула изобретения

ошибок, дополнительньш элемент И, элемент ИЛИ и элемент памяти, при этом другой вход элемента памяти сое динен с входом сброса накопителя по выходу из синхронизма, к управляющему входу которого подключен выход элемента памяти, вход запрета формирователя сигналов сброса и вход блокировки блока контроля фронтов конт- 25 рольной комбинации, информационный вход блока вьщеления коитролвной комбинации подключен к сигнальному входу блока опознавания сосредоточен ной синхрогруппы, вход считывания

Устройство цикловой синхронизации, содержащее блок опознавания сосредоточенной синхрогруппы, сигнальньй вход которого является входом устройства, формирователь тактового сигнала 30 которого соединен с соответствующим

входом блока вьделения контрольной

выход которого соединен с тактовым входом делителя-распределителя, селектирующие входы которого являются выходами устройства, причем управляющий выход делителя-распределителя соединен с входом считывания блока опознавания сосредоточенной синхрогруппы, первый и второй выходы которого соответственно соединены с входом накопителя по входу в синхронизм, который объединен с входом элемента И, и счетным входом накопителя по выходу из синхронизма, вход сброса и выход которого соответственно соеди35

комбинации и с другим входом дополнительного элемента И, а выход элемента И подключен к другому входу элемента ИЛИ, выход которого подключен к установочному входу делителя- распределителя, причем выходы стробирования и контроля формирователя интервала анализа подключены соответ 40 ственно к другому входу блока строби рования и входу контроля формировате ля сигналов сброса, выход которого подключен к входу сброса накопителя ошибок.

Составитель А. Яврумов Редактор В. Бугренкова Техред М.Ходанич Корректор М. Максимишинец

Заказ 6009/57 Тираж 636

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

нены с выходом накопителя по входу в синхронизм и с другим входом элемента И, отличающееся тем, что, с целью повышения точности синхронизации путем контроля установления синхронизма при приеме контрольной информации без увеличения времени вхождения в синхронизм, введены формирователь сигналов сброса, формирователь интервала анализа и последовательно соединенные блок выделения контрольной комбинации, блок контроля фронтов контрольной комби

ошибок, дополнительньш элемент И, элемент ИЛИ и элемент памяти, при этом другой вход элемента памяти соединен с входом сброса накопителя по выходу из синхронизма, к управляющему входу которого подключен выход элемента памяти, вход запрета формирователя сигналов сброса и вход блокировки блока контроля фронтов конт- рольной комбинации, информационный вход блока вьщеления коитролвной комбинации подключен к сигнальному входу блока опознавания сосредоточенной синхрогруппы, вход считывания

которого соединен с соответствующим

комбинации и с другим входом дополнительного элемента И, а выход элемента И подключен к другому входу элемента ИЛИ, выход которого подключен к установочному входу делителя- распределителя, причем выходы стробирования и контроля формирователя интервала анализа подключены соответ- ственно к другому входу блока стробирования и входу контроля формировате- ля сигналов сброса, выход которого подключен к входу сброса накопителя ошибок.

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ДВУСТОРОННИМ СОГЛАСОВАНИЕМ СКОРОСТИ | 1991 |

|

RU2022476C1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| Устройство для синхронизации по циклам | 1988 |

|

SU1690209A1 |

| Устройство синхронизации по циклам | 1990 |

|

SU1809543A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| Устройство синхронизации по циклам | 1980 |

|

SU944135A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Устройство синхронизации по циклам | 1980 |

|

SU886289A1 |

Изобретение относится к электросвязи и обеспечивает повышение точности синхронизации путем контроля установления синхронизма при приеме контрольной информации без увеличения времени вхождения в синхронизмГ Устр-во содержит блок 1 опознавания сосредоточенной синхрогруппы, нако- . питель 2 по выходу из синхронизма, накопитель 3 по входу в синхронизм, ,элементы И 4,9, ИЛИ 5, делитель-распределитель (ДР) 6, блок 7 вьщеления контрольной комбинации. (КК), блок 8 контроля фронтов КК, накопитель 10 ошибок, блок 11 стробирования, формирователь 12 сигналов сброса, формирователь 13 интервала анализа, эле- . мент памяти (ЭП) 14 и формирователь 15 тактового сигнала. Если блок 1 обнаруживает синхрогруппу, логическая 1 с его выхода заносится в накопитель 3, а если не обнаруживает - в накопитель 2. При заполнении накопителя 2 сигнал с его выхода поступает на установочньй вход ДР 6 и на ЭП 14, устанавливая его в состояние Отсутствие синхронизма. При этом ДР 6 сдвигает сигналы на своих выходах на один такт. Если синхрогруппа обнаруживается, то по сигналу заполнения накопителя 3 ДР 6 фиксирует временное положение сигналов на своих выходах, ЭП 14 устанавливается в состояние Синхронизм, разрешая анализ информации, передаваемой по контрольному каналу (блоки 7-13). Это обеспечивает подтверждение истинности синхронизма. 1 ил. i (Л со СП 00

| 0 |

|

SU403105A1 | |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Колтунов М.Н | |||

| и др | |||

| Синхронизация по циклам в цифровых системах связи.-М.: Связь, 1980, с.115.. | |||

Авторы

Даты

1987-12-07—Публикация

1985-07-02—Подача