Изобретение относится к электросвязи и может быть использовано в --устройствах предназначенных для передачи данных.

Известно синхронизирующее устройство, содержащее J/каналов, каждый из которых состоит из декодера и переключателя, при этом выходы Всех декодеров подключены к входам управляющего блока, выходы которого, объединенные с соответствующими выходами переключателей, подключены к входам элемента ИЛИ, а также блок задержки с Отводами 1.

Однако известное устройство имеет недостаточную помехозащищенность и скорость синхронизации.

Целью изобретения является повыщение помехозащищенности и увеличение скорости синхронизации.

Для этого в синхронизирующем устройстве, содержащем // каналов, каждый из которых состоит из декодера и переключателя, при этом выходы всех декодеров подключены к входам управляющего блока, выходы которого, объединенные с соответствующими выходами переключателей, подключены к входам элемента ИЛИ, а также блок задержки с отводами, в каждом канале введены объединенные по входу блоки регистрации и накопители, а также дополнительный элемент ИЛИ, причем выход блока регистрации через накопитель подключен к входу переключателя, а другой выход накопителя подключен к входу декодера, при этом выходы всех переключателей подключены к входам дополнительного элемента ИЛИ, а выход элемента ИЛИ через блок задержки с отводами подключен к другому входу каждого блока регистрации.

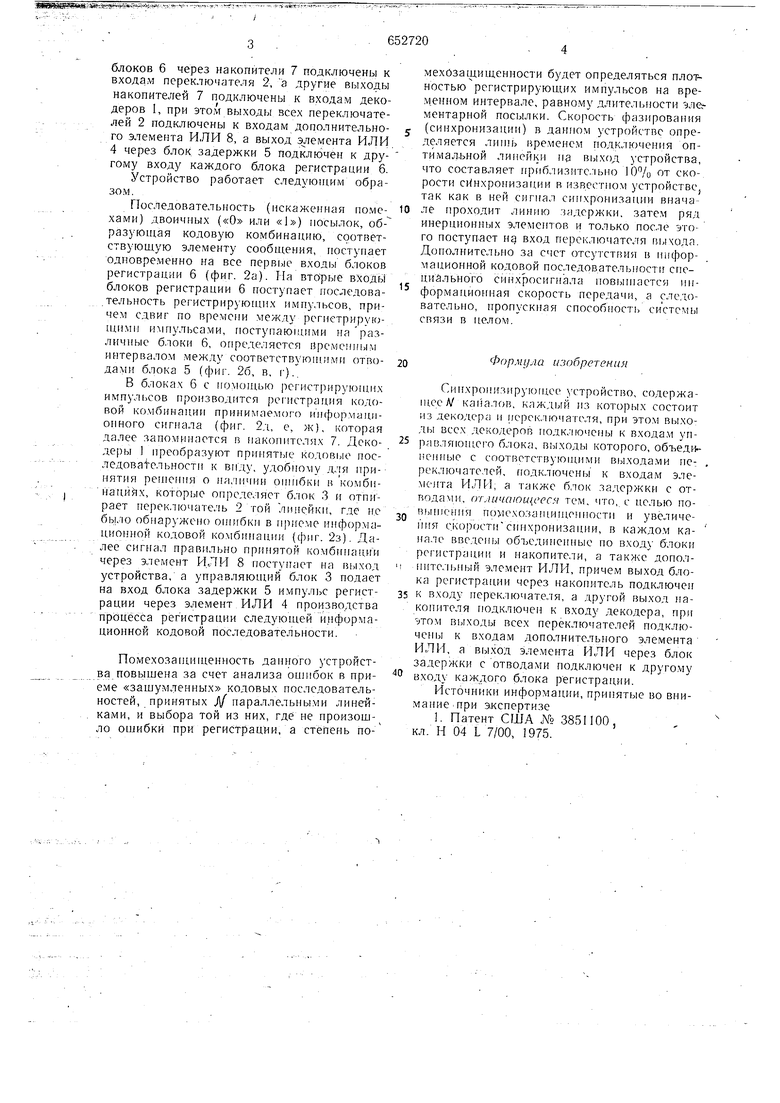

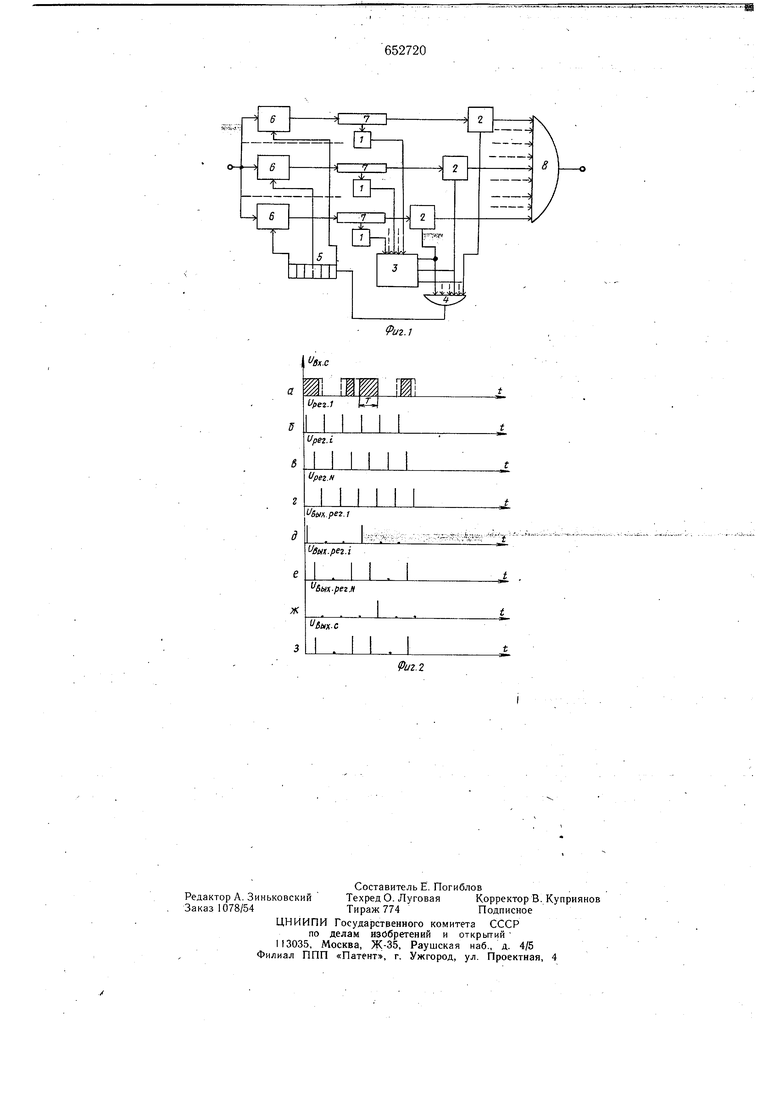

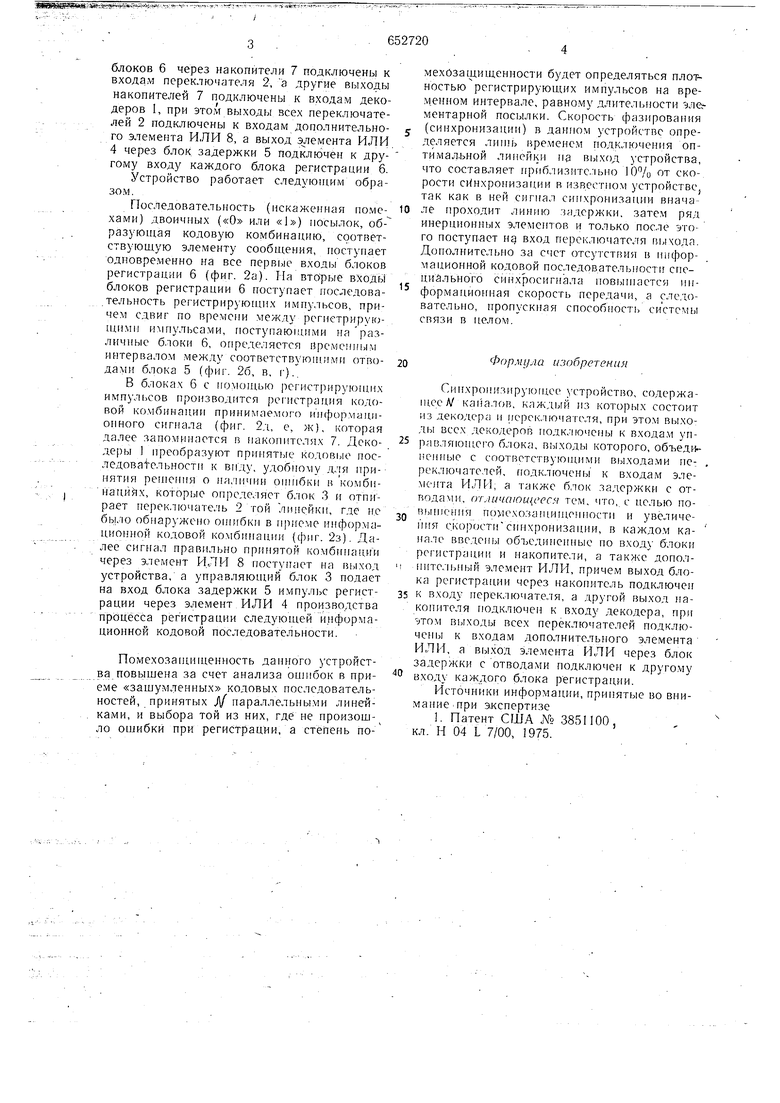

На фиг. 1 приведена структурная электрическая схема устройства; на фиг. 2 - временные диаграммы, поясняющие его работу.

Синхронизирующее устройство содержит JV каналов, каждый из которых состоит из декодера 1 и переключателя 2, при этом выходы всех декодеров 1 подключены к входам управляющего блока 3, выходы которого, объединенные с соответствующими выходами переключателей 2, подключены к входам элемента ИЛИ 4, а также блок задержки 5 с отводами, и в каждом каналов объединенные по входу блоки б, предназначенные для регистрации, и накопители 7, и дополнительный элемент ИЛИ 8, причем выходы

блоков 6 через накопители 7 подключены к входам переключателя 2, а другие выходы накопителей 7 подключены к входам декодеров I, при этом выходы Бсех переключателей 2 подключены к входам дополнительного элемента ИЛИ 8, а выход э лемента ИЛИ 4 через блок задержки 5 подключен к другому входу каждого блока регистрации 6.

Устройство работает следующим образом.

Последовательность (искаженная помехами) двоичных («О или «1) посылок, об- разуюн1ая кодовую комбинацию, соответствующую элементу сообщения, поступает одновременно на все nepnbie входы блоков регистрации 6 (фиг. 2а). На вторые входь блоков регистрации 6 поступает последовательность регистрирующих импульсов, причем сдвиг по времени между регистрирующими импульсами, поступающими наразличные блоки 6, определяется (фемемиым интервалом между соответствующими отводами блока 5 (фиг. 26, в, г)..

В блоках 6 с помощью регистрирующи.х импульсов производится регистрация кодовой комбинации принимаемого информационного сигнала (фиг. 2д, е, ж), которая далее запоминается в накопителях 7. Декодеры 1 преобразуют принятые кодовые последова1ельностп к внду, удобному д.ля принятия решения о наличии они|бки и комбинацмйх, которые определяет блок 3 и отпирает переключате.чь 2 той линейки, где н.е бь1ло обнаружено ошибкн в приеме информационной кодовой комби гации (фиг. 2з). Далее сигнал правильно принятой комбинации через элемент ИоТИ 8 поступает на вы.ход устройства, а управляющий блок 3 подает на вход блока задержки 5 импульс регистрации через элемент ИЛИ 4 производства процесса регистрации следующей информационной кодовой последовательности.

Помехоза1 и1щенность данного устройства повыщена за счет анализа ошибок в приеме «защумдениых кодовых последовательностей, принятых Д/параллельными линейками, и выбора той из них, где не произошло ошибки при регистрации, а степень помехозащищенности будет определяться плотностью регистрирующих импульсов на вре.менном интервале, равному длительности эле..ментарной посылки. Скорость фазирования (синхронизации) в данном устройстве определяется лишь временем подключения оптимал.ьной липейки ид В1)1ход устройства, что составляет приблизмтс.мьпо от скорости синхронизации в известном устройстве так как в ней сигнал синхронизации впача ле проходит линию задержки, зате.м ряд инерционных элементов и только после этого поступает nq вход переключателя гилхода. Дополнительно за счет отсутствия в информационной кодовой последовательност специального синхросигнала иовьииается ин5формационная скорость передачи, а слс.товательно, пропускная способность системы связи в целом.

Формула изобретен ия

Синхронизирующее устройство, содержаniecAi каналов, каждый из которых состоит из декодера и переключателя, при этом вь 1ходы всех декодеров Г1одключер1ы к входам управляюи1.его блока, выходы которого, объединенные с соответствующими выхода.ми не: рек.почателей, ггодключены к входа.м элемента ИЛИ, а также блок задержки с отводами, отличающееся тем, что, с целью повыщещ1Я помехозаищщениости и увеличения скоростисинхронизации, в каждом канале введены объединенные по блоки регистрации и накопители, а также дополпительньнЧ элемент ИЛИ, причем выход блока регистрации через наконитель подключен к входу переключателя, а другой выход накопителя подключен к входу декодера, при этом выходы веех переключателей подключены к входа.м дополнительного элемента ИЛИ, а выход элемента ИЛИ через блок задержки с отводами подключен к другому входу каждого блока регистрации.

Источники информации, принятые во вниманиеПри экспертизе

1. Патент США Л« 3851100, кл. Н 04 L 7/00, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

| Селектор импульсов в асинхронной адресной системе передачи цифровой информации | 1986 |

|

SU1334387A2 |

| Способ синхронизации пространственно разнесенных шкал времени при передаче дополнительной информации и устройство для его осуществления | 1990 |

|

SU1808135A3 |

| Устройство блочной синхронизации для групповых кодов | 1980 |

|

SU932643A1 |

| СПОСОБ ПРИЕМА-ПЕРЕДАЧИ ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ И СИСТЕМА ПРИЕМА-ПЕРЕДАЧИ ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 2003 |

|

RU2255425C1 |

| Декодер кодов Рида-Соломона | 1988 |

|

SU1690202A1 |

| Система телемеханики | 1990 |

|

SU1711216A1 |

| ШИРОКОПОЛОСНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ ФАЗЫ СИГНАЛА | 2017 |

|

RU2646602C1 |

бык. fez л

Авторы

Даты

1979-03-15—Публикация

1977-04-15—Подача