Изобретение относи ся к вычислительной технике и меже быть использовано в системах передачи мнфс рмацчи по канепам с Q-ичными сигналами, а такл.е в .очестве внешнего декодера каскадных кодов.

Цель изобретения - повышение помехозащищенности декодера.

На фиг. 1 приведена функциональная схема декодера; на фиг, 2 и 3 - выполнение соответственно блока управления и блока преобразования кодов.

Декодер кодов Ридг-Соломона (PC) содержит регистр 1 принятого кодового слова, регистр 2 выбранных кодовых символов блок 3 преобразования КОДОБ, регистр 4 чадежнс- сти кодовых символов, блок 5 определения индексов максимальных надежносгеР, регистр 6 выбранных индексов, регистр 7 вы- бранных надежности, бюкб поразрядного сравнения, ключ 9, регистр 10 декодирован- ного слова, регистр 11 копии, кодер 12 кода PC, компаратор 13. счетчик 14 числа различий, блок 15 управления, кольцевой сдвиговый регистр 16, блок 17 сравнения с единицей, первый у второй элементы 18 и

19развязки. На фиг 1 обозначены первые и вторые информационные входы 20 и /1 и входы 22 констант, Цеги тактирования и начальной установим ье. показаны. Разрядность соединений обозначена возле косой черты, пересекающей соответствующую линию (фиг. 1),

В основе работы декодера лежит следующий вновь разрабс ганг ый алгоритм быст рого декодирования кода PC (о, к), где п - длина кодового слова, k - число информационных символов. Ил сакг-лз связи на ВХОДУ

20v, 21 декодера поступает 0-ичные символы кодового слоза м значения надежности ГфИНР э) СИМВОЛОВ КОДОВ ЗГС-

слова. По величине1 надежности отбиоаготск k+ д наиболее надечных символов пр№Ј-- того кодового слозэ, Этим символам ставятся з соответствие го -ки проективной плоскости PG 12,q i где q2 + q +1 k+ Q, д q + 1 следующем образом. Запись прямей PG S2,q I представляет собой последовательность О и Г, состоящая из k + J- д элементов, примем нвдевьы: злеуен ам соответствует информационный иаэзр, Циклически сдвига т зт, пссле ователь- HOCTSJ ч б раз относительно списк отобранных симвопо з кодойо о слоза, получаем проективную плоскоегн. прямыми которой являются BCiJ чозмож -ые кодррые слова, получаемые при кзждог i сдвиге последовательности путем преобразований из системы остаточных КЛ-ЧСССЕ в обэЕщен- но-гозиционную с/ -лсну vt мз абобщвиигэпозицмониой системы в позиционную систему f, последующего кодирования кодом PC (n, k) различных информационных наборов, поступающих с выхода блока 3 преобразования кодов.

По определению проективной геометрии через любые две различные точки проходит единственна i . Указанное обстоятельство гарантирует исправление двух ошибок при перебрре k + д прямых и исправление n-k стираний. Перебор 6+1 прямой позволяет исправить одну ошибку.

Таким образом осуществляется полный или частичный перебор, в зависимости от состояния канала связи, максимум за k -f + д циклических сдвигов последовательности, позволяющий исправить одну или две ошибки и n-k стираний.

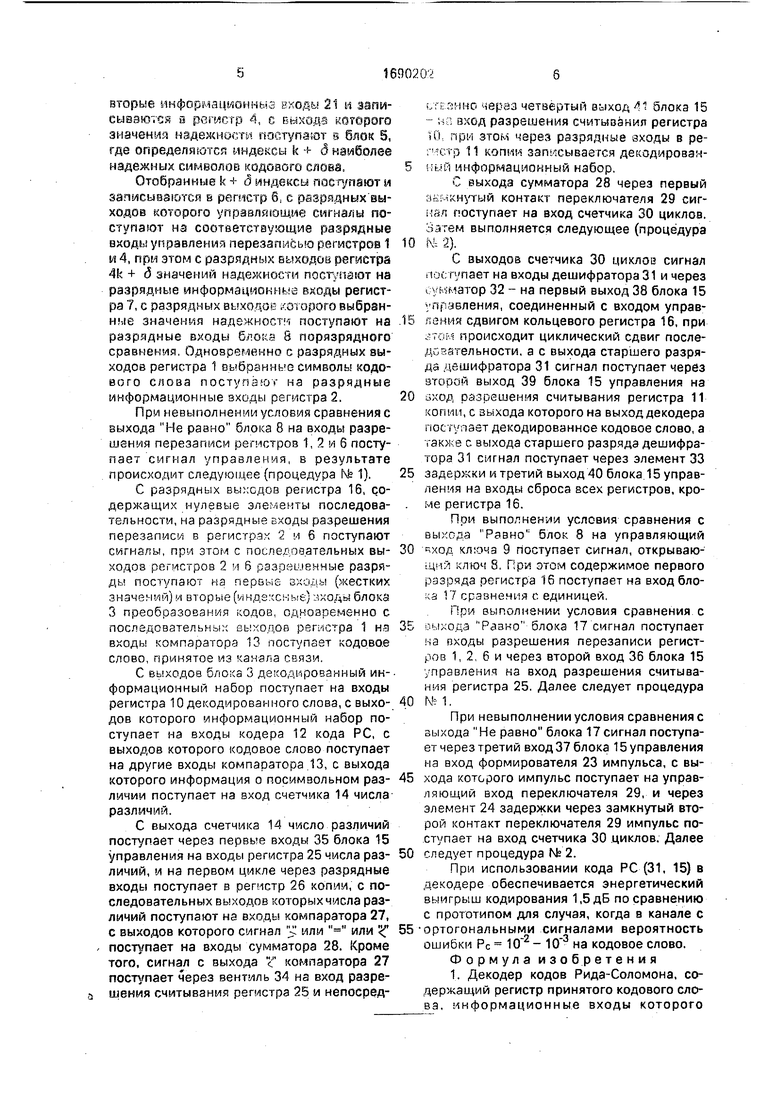

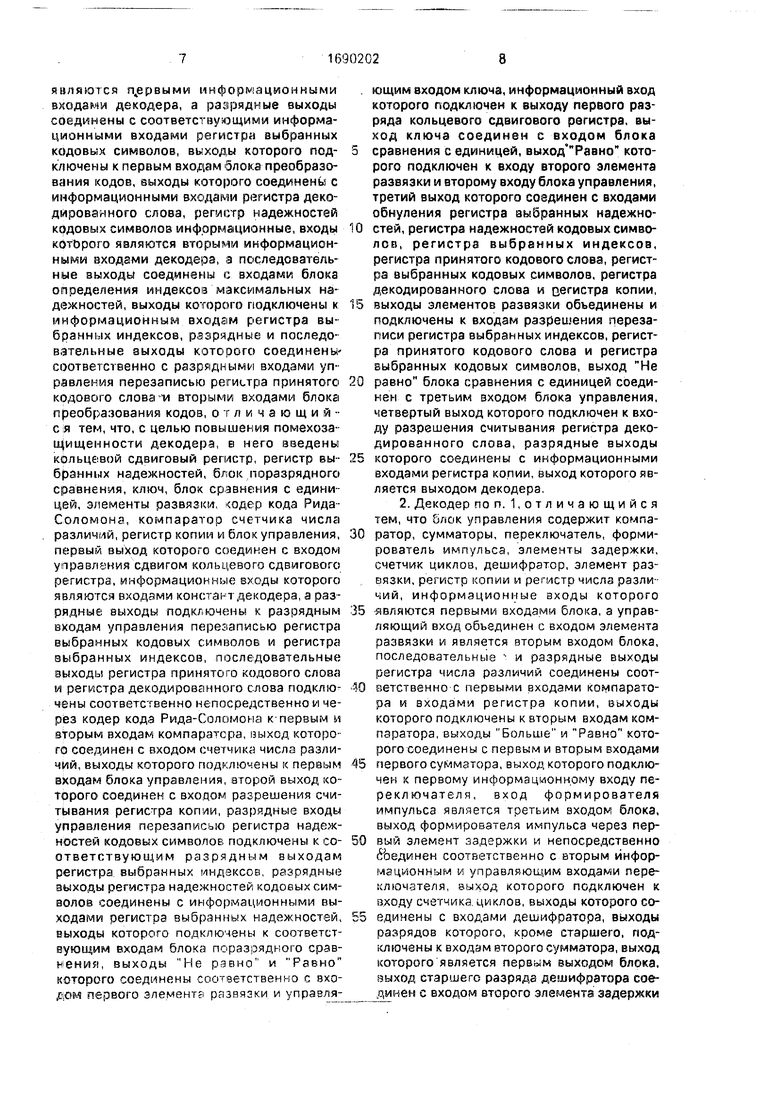

Блок 15 управления (фиг. 2) содержит формирователь 23 импульса, первый элемент 24 задержки, регистр 25 числа различий, регистр 26 копии, компаратор 27, первый сумматор 28, переключатель 29, счетчик 30 циклов, дешифратор 31, второй сумматор 32, второй элемент 33 задержки и элемент 34 развязки, На фиг. 2 обозначейы первые, второй и третий входы 35-37 и пер- вый-четЕ 5;:ть й выходы 38-41.

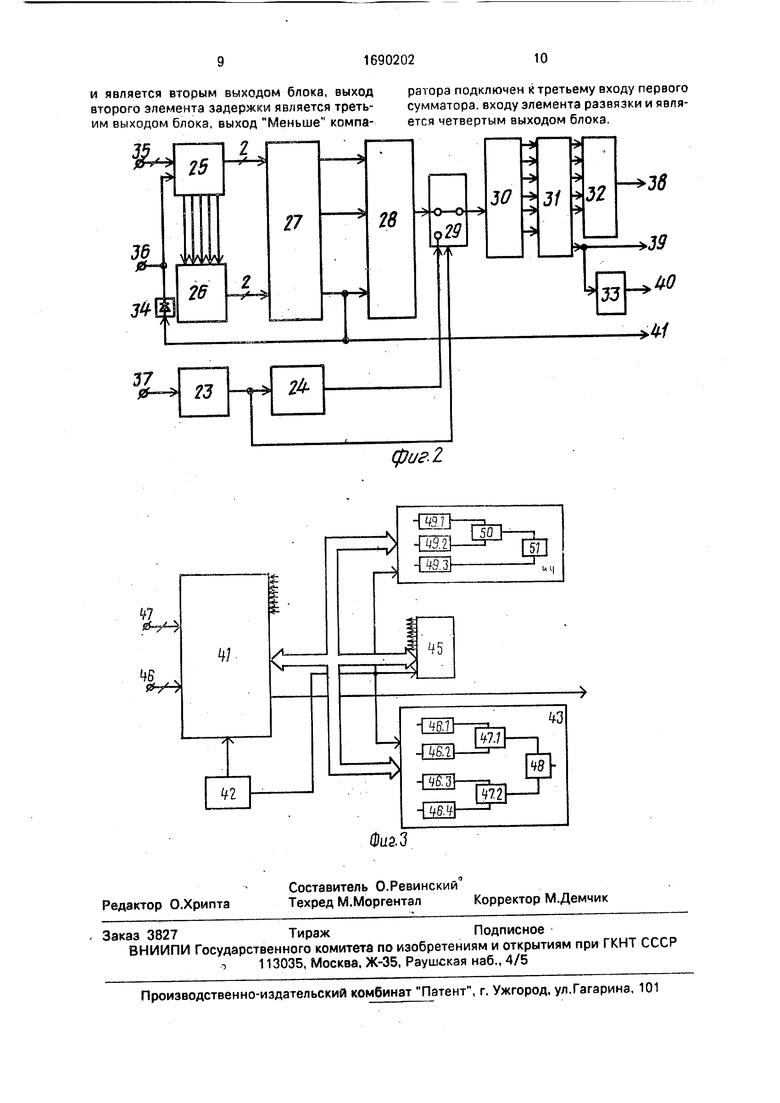

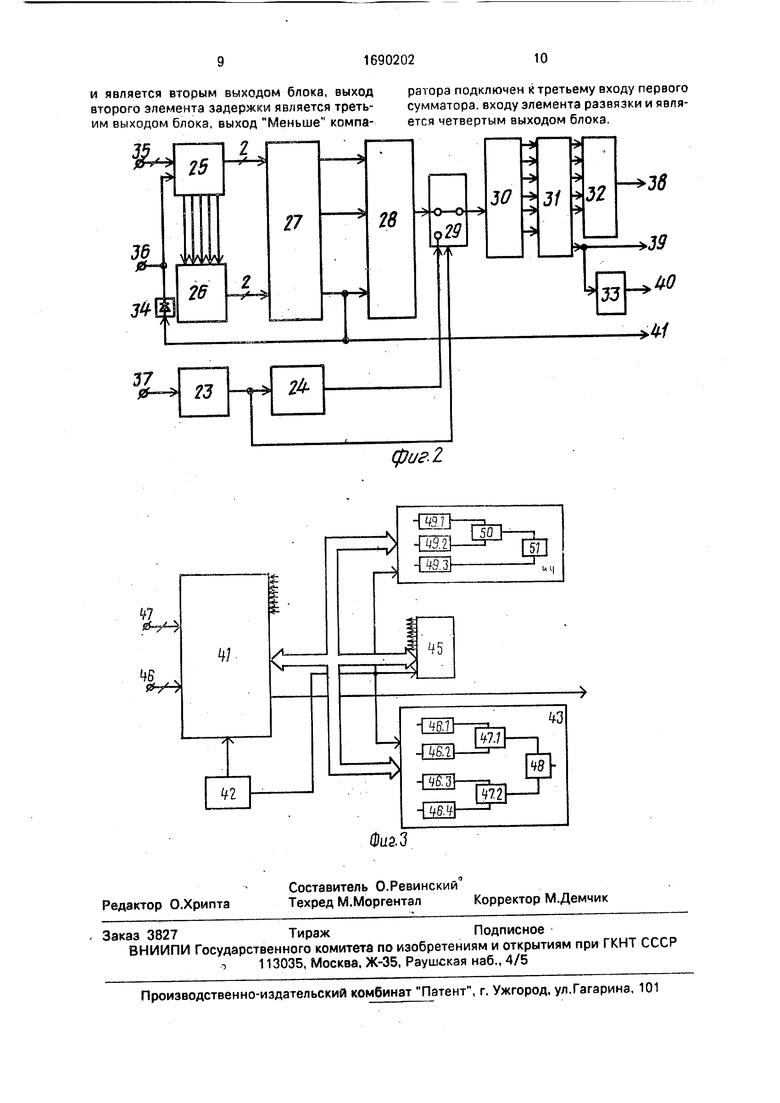

Блок 3 преобразования кодов служит для преобразования из сипемы остаточных классов в сообщенную позиционную систему, а из нее - а позиционную систему. Блок 3 содержит (фиг. 3) блок 41 оперативной памяти, тактовый генератор 42, первый я второй арифметико-логические блоки (АЛБ) 43 и 44 и блок 45 микрокомандного управления, выполненный ьа ПЗУ. Первый АЛБ 43 содерхит группу регистров 46, сумматоры &1 в поле GF(Q) и делитель 48 s поле GF(Q). Второй АЛБ 44 содержат регистров 49, умножитель 50 в поле GFfQ) и сумматор 51 в поле GF(Q).

Блок 5 определения индексов максимальных надежное ей может быть выполнен нз ПЗУ. Кодер 12 кода PC выполняется по любому возможному варианту. Формирователь 23 импульса представляет собой ждущий мультивибратор.

Декодер ходов PC функционирует следующим , б разом.

Двоичная последовательность, содер- жащал к д элементов, поступает на вход 22 ко.:стзнт и записывается s кольцевой сдвиговый регистр 16.

Жесткие значения символов кодового глава поступают на первые информационные входы 20 и записываются в регистр 1, одновременно значения надежности симво- лов принятого кодового слова поступают на

вторые информационнее- еходы 21 и записываются в регмегр 4, с выхода которого значения надежности поступает з блок 5, где определяются индексы k + д наиболее надежных символов кодового слова.

Отобранные k + д индексы поступают и записываются в регистр 6. с разрядных выходов которого управляющие сигналы поступают на соответствующие разрядные входы управления перезаписью регистров 1 и 4, при этом с разрядных выходов регистра 4k + д значений надежности поступают на разрядные информационные входы регистра 7, с разрядных виходос /спорого выбранные значения надежности поступают на разрядные входы блока 8 порязрядного сравнения. Одновременно с разрядных выходов регистра 1 выбраннь е символы кодового слова поступаю на разрядные информационные входы регистра 2.

При невыполнении условия сравнения с выхода Не равно блока 8 на входы разрешения перезаписи регистров 1, 2 и б поступает сигнал управления, в результате происходит следующее (процедура № 1).

С разрядных выходов регистра 16, содержащих нулевые элементы последовательности, на разрядные входы разрешения перезаписи в регистрах 2 и 6 поступают сигналы, при этом с поспегоаательных выходов регистров 2 м 6 разрешенные разряды поступают на первые зхсшы (жестких значений) и вторые (инде сс:-:ь-е) зходы блока 3 преобразования кодов, одновременно с последовательных оыхоп,ое регистра 1 на входы компаратора 13 поступает кодовое слово, принятое из чанала связи.

С выходов блока 3 декодированный ин-- формационный набор поступает на входы регистра 10 декодированного слова, с выходов которого информационный набор поступает на входы кодера 12 кода PC, с выходов которого кодовое слово поступает на другие входы компаратора 13, с выхода которого информация о посимвольном различии поступает на вход счетчика 14 числа различий.

С выхода счетчика 14 число различий поступает через первые входы 35 блока 15 управления на входы регистра 25 числа различий, м на первом цикле через разрядные входы поступает в регистр 26 копии, с последовательных выходов которых числа различий поступают на входы компаратора 27, с выходов которого сигнал ™ или или f поступает на входы сумматора 28. Кроме того, сигнал с выхода Т компаратора 27 поступает через вентиль 34 на вход разре- шения считывания регистра 25 и непосредf. очно через четвертый выход 1 блока 15 - о : вход разрешения считывания регистра Ui при этом через разрядные зходы в ре- .- чгр 11 копии записывается декодирован- s tjfi информационный набор.

С выхода сумматора 28 через первый г :- хнутый контакт переключателя 29 сиг- iiif, поступает на вход счетчика 30 циклов. Затем выполняется следующее (процедура

0 2).

С выходов счетчика 30 циклов сигнал ft о с, п/пает на входы дешифратора 31 и через i умматор 32 - на первый выход 38 блока 15 управления, соединенный с входом управ5 пения сдвигом кольцевого регистра 16, при -.том происходит циклический сдвиг последовательности, а с выхода старшего разряда дешифратора 31 сигнал поступает через ВТОРОЙ выход 39 блока 15 управления на

0 зход разрешения считывания регистра 11 копии, с выхода которого на выход декодера гюс гул зет декодированное кодовое слово, а гакже с выхода старшего разряда дешифратора 31 сигнал поступает через элемент 33

5 задержки и третий выход 40 блока 15 управления на входы сброса всех регистров, кроме регистра 16.

При выполнении условия сравнения с выхода Равно 1 блок 8 на управляющий

0 чход ключа 9 поступает сигнал, открывающий ключ S. При этом содержимое первого разряда регистра 16 поступает на вход бло- .в 17 сравнения с единицей.

Пси выполнении условия сравнения с

5 :. Равно блока 17 сигнал поступает на входы разрешения перезаписи регистров 1, 2, 6 и через второй вход 36 блока 15 управления на вход разрешения считывания регистра 25. Далее следует процедура

0 № 1.

При невыполнении условия сравнения с выхода Не равно блока 17 сигнал поступает через третий вход 37 блока 15 управления на вход формирователя 23 импульса, с вы5 хода которого импульс поступает на управляющий вход переключателя 29, и через элемент 24 задержки через замкнутый второй контакт переключателя 29 импульс поступает на вход счетчика 30 циклов. Далее

0 следует процедура Ns 2.

При использовании кода PC (31, 15) в декодере обеспечивается энергетический выигрыш кодирования 1,5 дБ по сравнению с прототипом для случая, когда в канале с

5-ортогональными сигналами вероятность ошибки Рс - на кодовое слово. Формула изобретения 1. Декодер кодов Рида-Соломона, содержащий регистр принятого кодового слова, информационные входы которого

являются первыми информационными входами декодера, а разрядные выходы соединены с соответствующими информационными входами регистра выбранных кодовых символов, выходы которого подключены к первым входам блока преобразования кодов, выходы которого соединены с информационными входами регистра декодированного слова, регистр иадежностей кодовых символов информационные, входы которого являются вторыми информационными входами декодера, а последовательные выходы соединены с входами блока определения индексов максимальных надежностей, выходы которого подключены к информационным входам регистра выбранных индексов, разрядные и последовательные выходы которого соединены соответственно с разрядными входами управления перезаписью регистра принятого кодового слова ч вторыми входами блока преобразования кодов, отличающий- с я тем, что, с целью повышения помехозащищенности декодера, в него введены кольцевой сдвиговый регистр, регистр выбранных надежностей, блок поразрядного сравнения, ключ, блок сравнения с единицей, элементы развязки, одер кода Рида- Соломона, компаратор счетчика числа различий, регистр копии и блок управления, первый выход которого соединен с входом управления сдвигом кольцевого сдвигового регистра, информационные входы которого являются входами констант декодера, а разрядные выходы подключены к разрядным входам управления перезаписью регистра выбранных кодовых символов и регистра выбранных индексов, последовательные выходы регистра принятого кодового слова и регистра декодированного слова подключены соответственно непосредственно и через кодер кода Рида-Соломона к-первым и вторым входам компаратора, выход которого соединен с входом счетчика числа различий, выходы которого подключены к первым входам блока управления, второй выход которого соединен с входом разрешения считывания регистра копии, разрядные входы управления перезаписью регистра надежностей кодовых символов подключены к соответствующим разрядным выходам регистра выбранных индексов, разрядные выходы регистра надежностей кодовых символов соединены с информационными выходами регистра выбранных надежностей, выходы которого подключены к соответствующим входам блока поразрядного сравнения, выходы Не равно и Равно которого соединены соответственно с входом первого элемента развязки и управля. ющим входом ключа, информационный вход которого подключен к выходу первого разряда кольцевого сдвигового регистра, выход ключа соединен с входом блока

сравнения с единицей, выход Равно которого подключен к входу второго элемента развязки и второму входу блоха управления, третий выход которого соединен с входами обнуления регистра выбранных надежно0 стей, регистра надежностей кодовых симво- лов, регистра выбранных индексов, регистра принятого кодового слова, регистра выбранных кодовых символов, регистра декодированного слова и оегистра копии,

5 выходы элементов развязки объединены и подключены к входам разрешения перезаписи регистра выбранных индексов, регистра принятого кодового слова и регистра выбранных кодовых символов, выход Не

0 равно блока сравнения с единицей соединен с третьим входом блока управления, четвертый выход которого подключен к входу разрешения считывания регистра декодированного слова, разрядные выходы

5 которого соединены с информационными входами регистра копии, выход которого является выходом декодера.

2. Декодер по п. 1,отличающийся тем, что Ьлок управления содержит компа0 ратор, сумматоры, переключатель, формирователь импульса, элементы задержки, счетчик циклов, дешифратор, элемент развязки, регистр копии и регистр числа различий, информационные входы которого

5 -являются первыми входами блока, а управляющий вход объединен с входом элемента развязки и является вторым входом блока, последовательные - и разрядные выходы регистра числа различий соединены соот0 ветственно с первыми входами компаратора и входами регистра копии, выходы которого подключены к вторым входам компаратора, выходы Больше и Равно которого соединены с первым и вторым входами

5 первого сумматора, выход которого подключен к первому информационному входу переключателя, вход формирователя импульса является третьим входом блока, выход формирователя импульса через пер0 вый элемент задержки и непосредственно сЪединен соответственно с вторым информационным и управляющим входами переключателя, выход которого подключен к входу счетчика циклов, выходы которого со5 единены с входами дешифратора, выходы разрядов которого, кроме старшего, подключены к входам второго сумматора, выход которого является первым выходом блока, выход старшего разряда дешифратора соединен с входом второго элемента задержки

и является вторым выходом блока, выход второго элемента задержки является третьим выходом блока, выход Меньше компаратора подключен «третьему входу первого сумматора, входу элемента развязки и является четвертым выходом блока,

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодер кодов Рида-Соломона | 1989 |

|

SU1777244A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ С ЖЕСТКИМИ И МЯГКИМИ РЕШЕНИЯМИ ДЛЯ ДВУХСТУПЕНЧАТОГО КАСКАДНОГО КОДА И МОДУЛЯЦИИ ПО ТИПУ СТЫКА С1-ФЛ | 2024 |

|

RU2834891C1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Декодер линейного систематического кода | 1987 |

|

SU1534756A1 |

| Кодек каскадного мажоритарного кода | 1984 |

|

SU1185613A1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

| Вероятностный мажоритарный декодер | 1986 |

|

SU1396282A1 |

Изобретение относится к вычислительной технике. Использование его в системах передачи информации по каналам с 0-ичны- ми сигналами позволяет повысить помехо22 liba-гч защищенность декодера, содержащего регистр 1 принятого кодового слова, регистр 2 выбранных кодовых символов, блок 3 преобразования кодов, регистр 4 надежностей кодовых символов, блок 5 определения индексов максимальных надежностей, регистр 6 выбранных индексов и регистр 10 декодированного слова. Благодаря введению регистра 7 выбранных надежностей, блока 8 поразрядного сравнения, ключа 9, регистра 11 копии, кодера 12 кода Рида-Соломона (п, к), компаратора 13, счетчика 14 нисла различий, блока 15 управления, кольцевого сдвигового регистра 16, блока 17 сравнения с единицей и элементов 18 и 19 развязки в декодере обеспечивается исправление одной или двух ошибок и n-k стираний. 1 з.п. ф-лы, 3 ил. (Л С Os о о ю о ю

W

фиг. i

}

45

$

| Устройство для исправления и обнаружения ошибок | 1980 |

|

SU921106A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналоговый декодер кода с ортогональными проверками | 1986 |

|

SU1401614A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Вопросы радиоэлектроники, Сер | |||

| ТПС, 1975 №11 с | |||

| Нефтяной конвертер | 1922 |

|

SU64A1 |

Авторы

Даты

1991-11-07—Публикация

1988-01-25—Подача