(54) УСТРОЙСТВО БЛОЧНОЙ СИНХРОНИЗАЦИИ

ДЛЯ ГРУППОВЫХ кодов

I

Изобретение относится к системам «связи и может использоваться для

блочной синхронизации систем передачи информации, применяющих смежно-групповые коды.

Известно устройство цикловой синхронизации, содержащее последовательно соединенные блок определения синдромов, опознаватель синдромов синхросигнала, элемент задержки, элемент совпадения, элемент объединения, накопитель ошибок, генератор цикловых импульсов и элемент запрета, выход которого подключен к второму входу накопителя ошибок, к второму входу элемента запрета подключены второй вход элемента совпадения и вход элеMeHta задержки, а также опознаватель синдромов исправляемых ошибок, включенный между входом опозна ателя синдромов синхросигнала и вторым входом элемента объединения Ct .

Недостатком данного устройства является сохранение высокой вероятности ложной синхронизации.

Известно устройство блочной синхронизации для групповых кодов, содержащее последовательно соединенные входной регистр, сумматор и декодер, последовательно соединенные генератор тактовых импульсов и делитель частоты, а также генератор кода, выход которого подсоединен к второму входу сумматора, дешифратор, вход которого подключен к выходу входного регистра и элемент И 2.

Недостаток этого устройства состоит в том, что переход в смежные классы групповых (п, К)-кодов при высокой скорости кода обеспечивает защиту от ложной синхронизации лишь на малом числе несинхронных позиций кодовых блоков.

Цель изобретения - повышение точности синхронизации.

Указанная цель достигается тем, что в устройство блочной синхронизации для групповых кодов, содержащее последовательно соединенные входной регистр, сумматор и декодер, последовательно соединенные генератор тактовых импульсов и делитель частоты, а также генератор кода, выход которого подсоединен к второму входу сумматора, дешифратор, вход ко торого подключен к выходу входного регистра, а также элемент И, введены последовательно соединенные дополнительный дешифратор и элемент ИЛИ, а также дискриминатор временного рассогласования, выход которого через элемент ИЛИ подсоединен к второму входу делителя частоты, выход которого подсоединен к объединенным первым входам входного регистра, элемента И и дискриминатора временного рассогласования, второй вход которого объединен с вторым входом элемента И и подключен к выходу дешифра тора, при этом выход элемента И подсоединен к входу генератора кода.

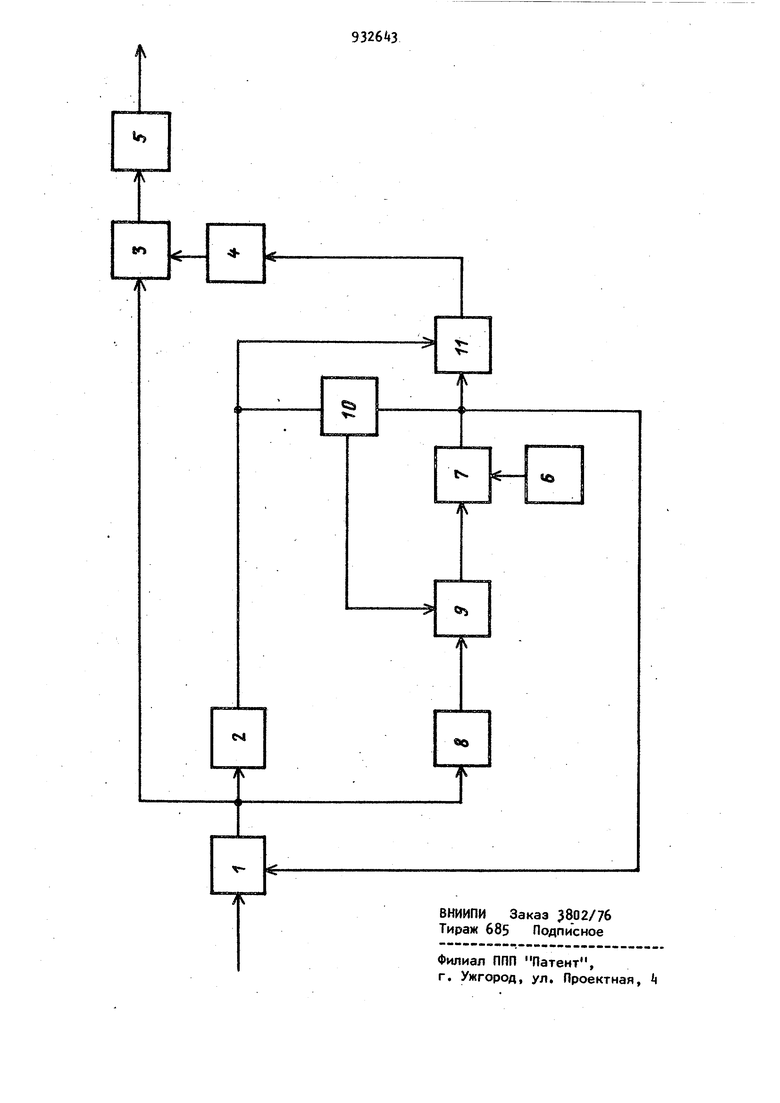

На чертеже изображена структурноэлектрическая схема устройства.

Устройство содержит входной регистр 1, дешифратор 2, сумматор 3. генератор k кода, декодер 5. генератор 6 тактовых импульсов, делитель 7 частоты, дополнительный дешифратор8 элемент ИЛИ 9, дискриминатор 10 временного рассогласования и элемент , И 11 .

Устройство работает следующим образом.

При передаче информации используются кодовые блоки, принадлежащие .двум смежно-групповым кодам: (п ,K-f )-K i

КОДУ С НИЗКОЙ скоростью кода R

-1 и

и (п,К23-коду с высокой скоростью

R. . При

кода

соответствую 2. и -2.

щем выборе кодов вероятность случайного удовлетворения некоторой комбинацией из символов, образованной на стыке двух блоков, принадлежащих одному коду, закону построения другого кода равна нулю.

В начале каждого цикла передачи информации передаются кодовые блоки, принадлежащие некоторому сменному классу циклического (п ,К)-кода с низкой скоростью кода, для которых вероятность случайного удовлетворения несинхронных фазовых сдвигов закону построения кода равна

нулю (т.е. равна нулю вероятность ложной синхронизации). Дешифратор 8 с каждым сдвигом информации, накопленной во входном п-разрядном регистре, выдает результаты проверки различных фазовых положений. В синхронном положении на выходе дешифратора 8 появляется единичный сигнал, который фазирует делитель 7 частоты, управляемый генератором 6 тактовых импульсов. При. этом сигнал с выхода делителя 7 частоты кратности Г:п начинает поступать на управляющий вход входного регистра 1, обнуляя его каждые п тактов (по окончании кодового- блока) .

После передачи одного или нескольких блоков низкоскоростного кода начинается пере/ ача информации кодовыми блоками, принадлежащими некоторому смежному классу циклического (п,Kg)-кода с высокой скоростью кбда длякоторых вероятность ложной синхронизации равна нулю лишь для нескол ких несинхронных фазовых сдвигов, принадлежащих синхронному положению Этим достигается повышение скорости передачи информации, поскольку при постоянстве полосы частот канала связи, за ту же длительность п-символьного блока передается большее число информационных символов.

Дешифратор 2 выдает единичные сигналы (в синхронном режиме), которые поступают на первый вход элемента И 1 на второй вход которого поступают сигналы с делителя 7 частоты.

При отсутствии сбоя синхронизации на выходе элемента И 11 появляется сигнал, фазирующий генератор 4 кода.

Выходная информации при этом синхpO ii;o суммируется с главным элементом смежного класса в сумматоре 3 и декодируется в декодере 5При случайном сбое синхронизации на выходе дешифратора 2 единичный сигнал пропадает, если комбинация п символов на стыке кодовых блоков не удовлетворяет закону построения кода. При этом пропадают фазирующие сигналы на входе делителя 7 частоты и выходе элемента И 11 и прекращается обнуление входного регистра 1 и снятие информации с декодера 5- Дешифратор 2 начинает выдавать результаты проверок различных фазовых положений с каждым сдвигом информации, накопленной, во входном регистре 1. При появлении на выходе дешифратора 2 единичного сигнала, свидетельствующего об удовлетворении кодовой комбинации закону постороения кода, си1- нал на выходе элемента И 11 появится лишь при одновременном приходе на ее второй вход сигнала с делителя 7 час тоты. Этот случай соответствует правильной синхронизации. Единичные сигналы с выхода дешифратора 2 одновременно поступают на второй вход дискриминатора 10 временного рассогласования, на первый вход которого поступают сигналы с делителя 7 частоты. В дискриминаторе 10 временного рассогласования осуществляётся анализ временного положения выходного сигнала дешифратора 2 относительно последнего сигнала, поступившего с делителя 7 частоты. Если это рассогласование составляет At mn Тс ± i Те , где Vf,- длительность символа, m - про извольное целое число, -максималь ное число фазовых сдвигов, при которых вероятность ложной синхронизации равна нулю, то выходной сигнал дискриминатора 10 временного рассогласова ния перефазирует делитель 7 частоты в соответствии с временным положением выходного единичного сигнала дешифратора 2 и на выходе элемента И 11 появ ляется сигнал, разрешающий снятие информации. Если же временное рассогласование превышает число сдвигов, при которых вероятность ложной синхронизации равна нулю, то это означает ложное определение синхронного положения. При этом сигнал на выходе дискриминатора 10 временного рассогласования отсутствует, перефазирования делителя 7 частоты не пр-ои сходит и поиск синхронного положения продолжается. Таким образом, предлагаемое устройство, использующее свойства смеж-но групповых кодов, позволяет существенно снизить вероятность приема :ложной информации за счет уменьшения вероятности ложной синхронизации как в начале сеанса связи, так и при восстановлении синхронизма при возможных сбоях, при 1бохранении высокой скорости передачи информации, т.е. 1повысить точность синхронизации. Формула изобретения Устройство блочной синхронизации для групповых кодов, содержащее последовательно соединенные входной регистр, сумматор и декодер, последовательно соединенные генератор тактовых импульсов и делитель частоты, а также генератор кода, выход которого подсоединен к второму входу сум матора, дешифратор, вход которого подключен к выходу входного регистра, а также элемент И, о т л и ч аю щ е е с я тем, что, с целью повышения трчности синхронизации, в него введены последовательно соединенные дополнительный дешифратор и элемент ИЛИ, а также дискриминатор временного рассогласования, выход которого через элемент ИЛИ подсоединен к второму входу делителя частоты, выход которого подсоединен к объединенным первым входам входного регистра, элемента И и дискриминатора временного рассогласования, второй вход которого объединен с вторым входом элемента И и подключен к выходу дешифратора, при этом выход эле мента И подсоединен к входу генерато ра кода. Источники информации, принятые §о внимание при экспертизе 1.Авторское свидетельство СССР № 569039, кл. Н 0 L 7/08 , 1976. 2.Авторское свидетельство СССР № 98751, кл. Н Oi L 7/08, 1973 (прототип).

Ы

00

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство для цикловой синхронизации корректирующих кодов | 1978 |

|

SU788413A2 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА ПЕРЕДАЧИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 1986 |

|

SU1840556A2 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство задержки импульсов | 1980 |

|

SU917326A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

| Устройство цикловой синхронизации для блочных кодов | 1975 |

|

SU557499A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Устройство цикловой синхронизации для блочных кодов | 1975 |

|

SU565403A1 |

Авторы

Даты

1982-05-30—Публикация

1980-12-24—Подача