Изобретение относится к ядерной электронике и может быть использовано в прецизионных амплитудных спектрометрических трактах, использующих полупроводниковые детекторы.

Известен амплитудный анализатор, в котором улучшение отношения сигнал/шум измерительного тракта производится в аналоговой форме. Он содержит детектор, предусилитель, формирующий усилитель, преобразователь и накопитель 1|.

Основным недостатком анализатора является невысокое быстродействие и стабильность, определяемые формирующим усилителем.

Наиболее близким техническим решением к изобретению является амплитудный анализатор с цифровым фильтром, содержащий последовательно соединенные детектор, усилитель, интегратор, преобразователь, промежуточное запоминающее устройство, арифметическое устройство и накопитель 2.

Однако наличие прецизионного преобразователя в этом анализаторе ограничивает быстродействие всей системы и, в частности, не позволяет эффективно работать в жесткой области спектра, требующей высокой тактовой частоты при обработке информации.

Целью изобретения является повышение точности в жесткой (наиболее часто используемой) области спектра.

Это достигается тем, что в амплитудный анализатор спектра, содержащий последовательно соединенные детектор, усилитель и интегратор, первый преобразователь, подключенный к входу арифметического блока через постоянное запоминающее устройство, накопитель, сумматоры и блок управления, выход которого подключен к управляющим входам интегратора, первого преобразователя, постоянного запоминающего устройства, арифметического блока и накопителя, а вход соединен с выходом усилителя, введены аналоговое запоминающее устройство и второй преобразователь, связанные между собой через первый сумматор, второй вход которого подключен к другому аналогового запоминающего устройства и одновременно к первому входу второго сумматора, второй вход которого подключен к выходу интегратора и к первому выходу аналогового запоминающего устройства. Выход второго сумматора связан со входом

первого преобразователя. Причем выход блока управления подключен к управляющим входам аналогового запоминающего устройства и второго преобразователя, выход которого соединен с первым входом третьего сумматора, своим вторь м входом подключенного к выходу арифметического блока, а выходом - к входу накопителя.

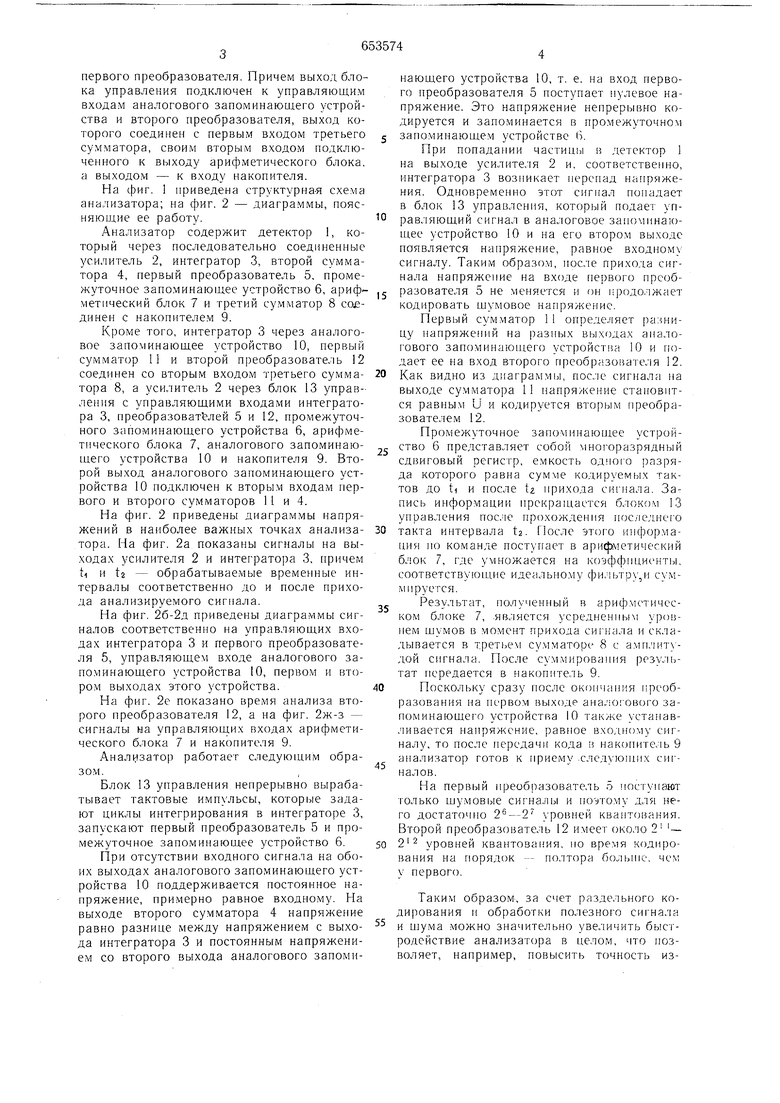

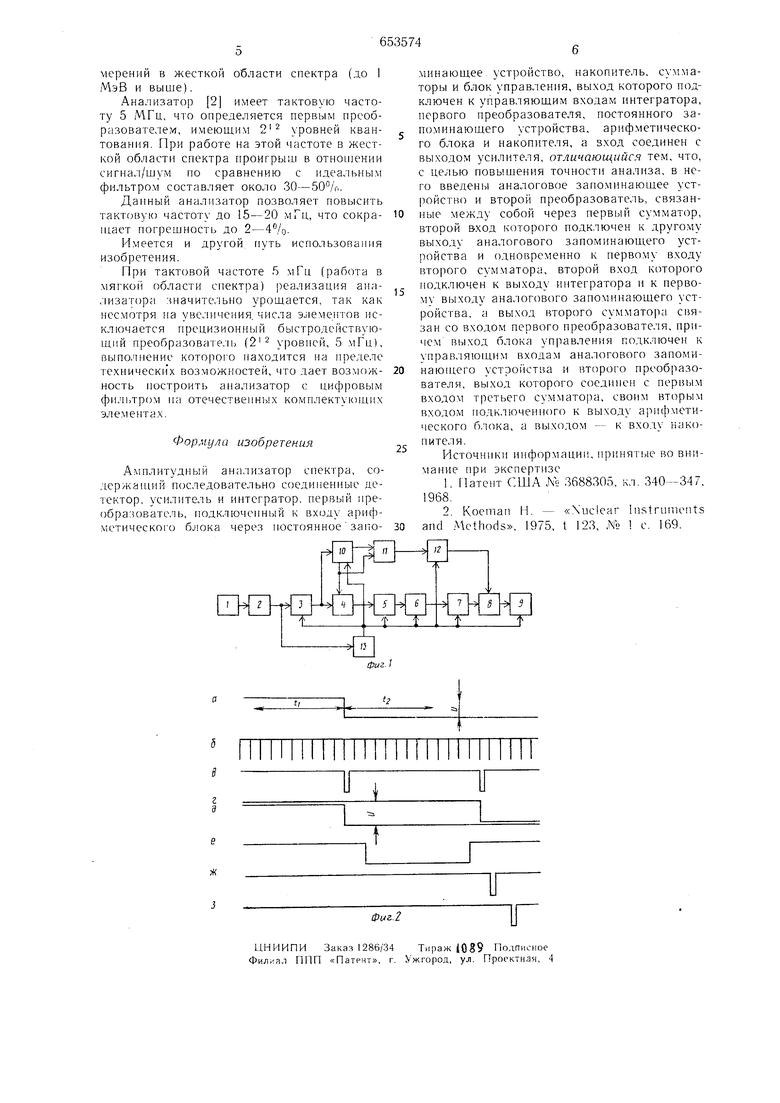

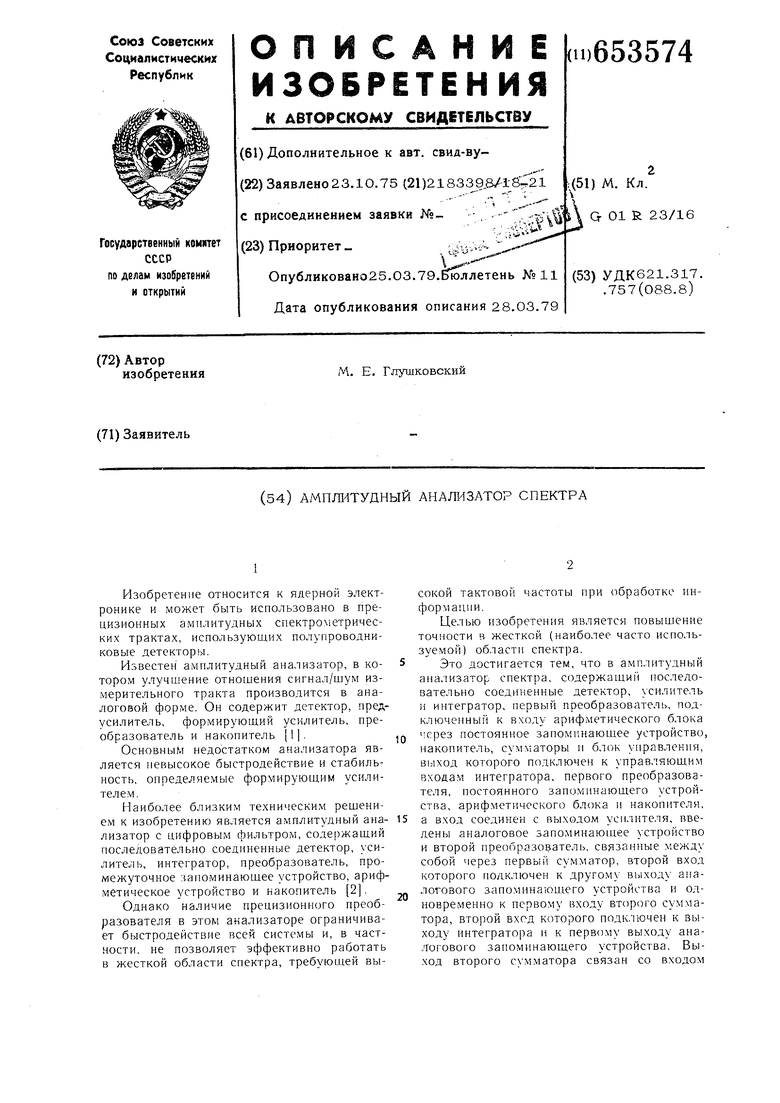

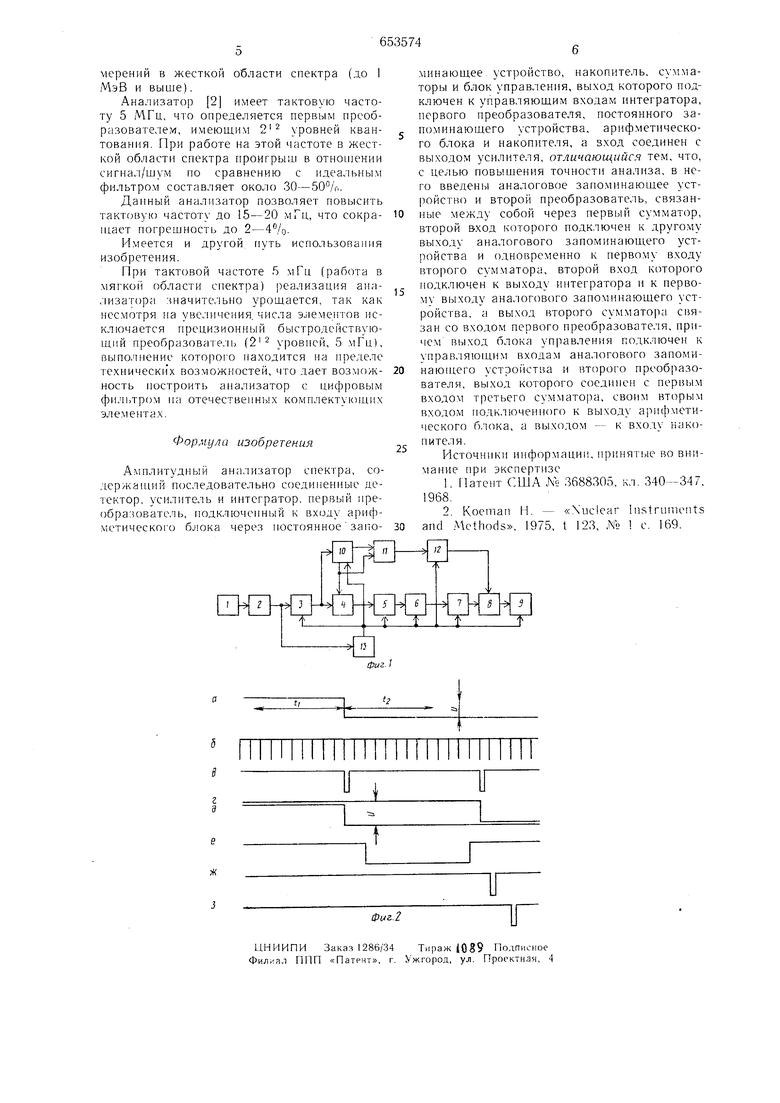

На фиг. 1 приведена структурна-я схема анализатора; на фиг. 2 - диаграммы, поясняющие ее работу.

Анализатор содержит детектор 1, который через последовательно соединенные усилитель 2, интегратор 3, второй сумматора 4, первый преобразователь 5. промежуточное запо.минающее устройство 6, арифметический блок 7 н третий сумматор 8 соединен с накопителем 9.

Кроме того, интегратор 3 через аналоговое запоминающее устройство 10, первый сумматор 11 и второй преобразователь 12 соединен со вторым входом третьего сумматора 8, а усилитель 2 через блок 13 управления с управляющими входами интегратора 3, преобразователей 5 и 12, промежуточного запоминающего устройства 6, арифметического блока 7, аналогового запоминающего устройства 10 и накопителя 9. Второй выход аналогового запоминающего устройства 10 подключен к вторым входам первого и второго сумматоров 11 и 4.

На фиг. 2 приведены диаграммы напряжений в наиболее важных точках анализатора. На фиг. 2а показаны сигналы на выходах усилителя 2 и интегратора 3, причем ti и 1г - обрабатываемые временные интервалы соответственно до и после прихода анализируемого сигнала.

На фиг. 2б-2д приведены диаграммы сигналов соответственно на управляющих входах интегратора 3 и первого преобразователя 5, управляющем входе аналогового запоминающего устройства 10, первом и втором выходах этого устройства.

На фиг. 2е показано время анализа второго преобразователя 12, а на фиг. 2ж-з - сигналы на управляюндих входах арифметического блока 7 и накопителя 9.

Анализатор работает следующим образом.

Блок 13 управления непрерывно вырабатывает тактовые импульсы, которые задают циклы интегрирования в интеграторе 3, запускают первый преобразователь 5 и промежуточное запоминаюидее устройство 6.

При отсутствии входного сигнала на обоих выходах аналогового запоминающего устройства 10 поддерживается постоянное напряжение, примерно равное входному. На выходе второго сумматора 4 напряжение равно разнице между напряжением с выхода интегратора 3 и постоянным напряжением со второго выхода аналогового запоминающего устройства 10, т. е. на вход первого преобразователя 5 поступает нулевое напряжение. Это напряжение непрерывно кодируется и запоминается в промежуточном 5 запоминающем устройстве (х

Нри попадании частицы в детектор 1 на выходе усилителя 2 и. соответственно, интегратора 3 возникает перепад напряжения. Одновременно этот сигнал попадает в блок 13 управления, который подает управ.ляющий сигнал в аналоговое запоминающее устройство 10 и на его втором выходе появляется напряжение, равное входному сигналу. Таким образом, после прихода сигнала напряжение на входе первого преобразователя 5 не меняется и он продолжает кодировать щумовое напряжение.

Первый сумматор 1 1 опреде..1яет разницу напряжений на раз1По1х выходах аналогового заноминаюняего устройства 10 и подает ее на вход второго преобразовате;1я 12.

0 Как видно из диаграммы, после сигнала на выходе сумматора 11 напряжение становится равным и и кодируется вторым преобразователем 12.

Промежуточное запоминающее устройство 6 представляет собой многоразрядный сдвиговый регистр, емкость одно1о разряда которого равна сумме кодируемых тактов до ti и после ii прихода сигнала. Запись информации нрекращается блоком 13 управления noc.ie прохождения последнего

0 такта интервала t2. После этого ин()орма 1ия ио команде постугшет в арифметический блок 7, ivie умножается на коэффициенты, соответствующие идеальному фи,чьтру,и суммируется.

Результат, полученный в арифметическом блоке 7, .является усредненным уровнем щумов в момент прихода сигнала и складывается в третьем сумматоре 8 с амп,читудой сигнала. После суммирования результат иередается в накопитель 9,

Поскольку сразу после окончания преобразования на нервом выходе ана,логового запоминающего устройства 10 также устанавливается напряжение, равное входному сигналу, то после передачи кода в накопитель 9 анализатор готов к приему следуюншх cniналов.

На первый преобразователь 5 поступают только шу. сигналы и поэтому для него достаточно 2®-2 уровней квантования. Второй преобразователь 12 имеет около 2 -

0 22 уровней квантования, по время кодирования на порядок -- полтора больше, чем у первого.

Таким образом, за счет раздельного кодирования и обработки полезного сигнала и шума можно значительно увеличить быстродействие анализатора в целом, что позволяет, например, новысить точность измереннй в жестко11 области спектра (до 1 МэВ и выше). Анализатор 2 имеет тактовую частоту 5 МГц, что определяется первым преобразователем, имеюпдим 2 уровней квантованпя. При работе на этой частоте в жесткой области спектра проигрьпи в отнои ении сигнал/шум по сравнению с идеальным фильтром составляет около 30-50/о. Данный анализатор позволяет повысить тактовую частоту до 15-20 мГц, что сократает погрешность до 2-4%. Имеется и другой путь использования изобретения. При тактовой частоте 5 мГц (работа в мягкой области спектра) реализация ана;|изатора значите.мьно урошается, так как несмотря на увеличения, числа элементов исключается нрецизионный быстродействующий преобразователь (2 уровней, 5 мГц), выполнение которого находится на нределе технических возможностей, что дает возможность построить анализатор с цифровым фильтром на отечественных комплектующих элеме1ггах. Форму/га изобретения Амплитудный анализатор спектра, содержащий п()следовательно соединенные детектор, усилитель и интегратор, первый преобразователь, подключенный к входу арифметического блока через постоянноезапоминающее устройство, накопитель, сумматоры и блок управления, выход которого подключен к управляющим входам интегратора, первого преобразователя, постоянного запоминающего устройства, арифметического блока и накопителя, а вход соединен с выходом усилителя, отличающийся тем, что, с целью повышения точности анализа, в него введены аналоговое запоминающее устройство и второй преобразователь, связанпые между собой через первый сумматор, второй ВХОД которого подключен к другому выходу аналогового запоминающего устройства и одновременно к первому входу второго сумматора, второй вход которого подключен к выходу интегратора и к первому выходу аналогового запоминающего устройства, а выход второго сумматора связан со входом первого преобразователя, причем выход блока управления подключен к управляющим входам аналогового запоминающего устройства и второго преобразователя, выход которого соединен с первым входом третьего сумматора, своим вторым входом подключенного к выходу арифметического блока, а выходом - к входу накопителя. Источники информации, принят1 1е во впимание при экспертизе 1.Патент США № 3688305, кл. 340-347, 1968. 2.Коетап Н. - «Nuclear Instruments and Methods, 1975, t 123, ,Nl 1 c. 169.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ ЛАЗЕРНЫЙ ДОПЛЕРОВСКИЙ ЛОКАТОР | 1990 |

|

RU2012013C1 |

| ПРИЕМОИНДИКАТОР СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1993 |

|

RU2067771C1 |

| Устройство для поиска шумоподобного сигнала | 1984 |

|

SU1277415A1 |

| СПОСОБ ИНДЕНТИФИКАЦИИ ТОНАЛЬНЫХ СИГНАЛОВ В СЕТЯХ СВЯЗИ И ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2004 |

|

RU2291405C2 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| Анализатор спектра | 1985 |

|

SU1287033A1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА МОДУЛИРОВАННЫХ ПО ФАЗЕ И ЧАСТОТЕ СИГНАЛОВ | 2005 |

|

RU2288539C1 |

| РАДИОВЫСОТОМЕР | 2001 |

|

RU2212684C1 |

| МНОГОКАНАЛЬНЫЙ ПРИЕМОИНДИКАТОР СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2001 |

|

RU2205417C2 |

e

ж

Авторы

Даты

1979-03-25—Публикация

1975-10-23—Подача