(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь компенсационного интегрирования | 1974 |

|

SU764126A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU660238A1 |

| НИЗКОЧАСТОТНЫЙ ИЗМЕРИТЕЛЬ ФАЗОВОГО СДВИГА | 1992 |

|

RU2024028C1 |

| Интегрирующий аналого-цифровой преобразователь | 1985 |

|

SU1279069A1 |

| Интегрирующий аналого-цифровой преобразователь | 1986 |

|

SU1314458A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1560987A1 |

| Интегрирующий аналого-цифровой преобразователь | 1986 |

|

SU1410274A1 |

| Устройство для определения логарифма отношения двух напряжений | 1982 |

|

SU1103249A1 |

| Коррелятор | 1980 |

|

SU875403A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

Изобретение относится к вычислительной технике.

Известен аналого-цифровой преобразователь, содержащий интегратор, счетчик, генератор импульсов и устройство сравнения l.

Однако такое устройство имеет значительную погреишость преобразования.

Известен также аналого-цифровой преобразователь (АЦП), содержащий блок управления, первый и второй выходы которого через первый и второй триггеры соедушены с управляющими входами первого и второго ключей, которые через элемент ИЛИ соединены с управляющим входом третьего ключа, выход которого через конденсатор соединен со входом операционного усилителя, который через резистор соединен с выходами первого и второго ключей, выход операционного усилителя соединен с входом третьего ключа и через нуль-орган соедк 1ен с первым входом третьего . триггера, третий выход блока ут1рав; ения соединен со входом генератора импульсов, первый выход которого соединен с первым входом второго элемента ИЛИ, второй выход соединен с первым входом элемента И,

выход которого соединен со вторым входом второго элемента ИЛИ, выход которого соединен со входом счетчика, выход которого соединен с первым входом блока управления, второй элемента И соедш1ен с управляющим входом второго триггера, выход третьего трщтера соединен со вторым входом блока управления 2.

Недостатком этого устройства является низкая топюсть преобразования.

Целью изобретения является повышение точности преобразования и уменьшение времени восстановления.

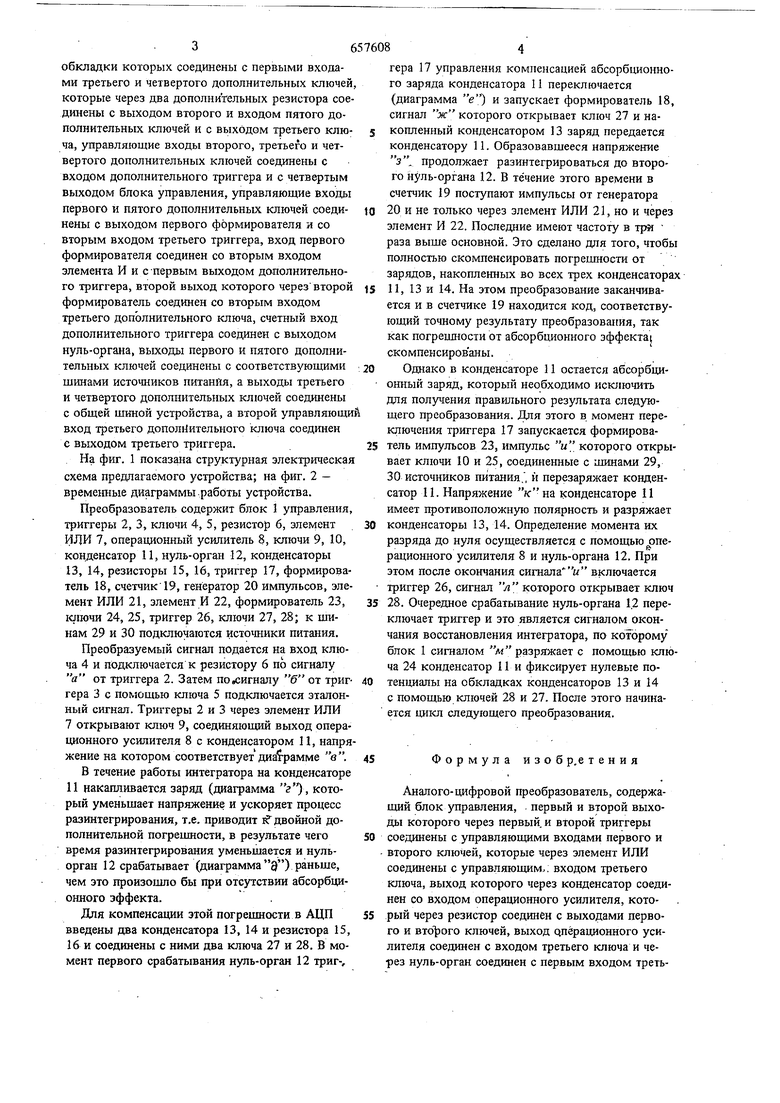

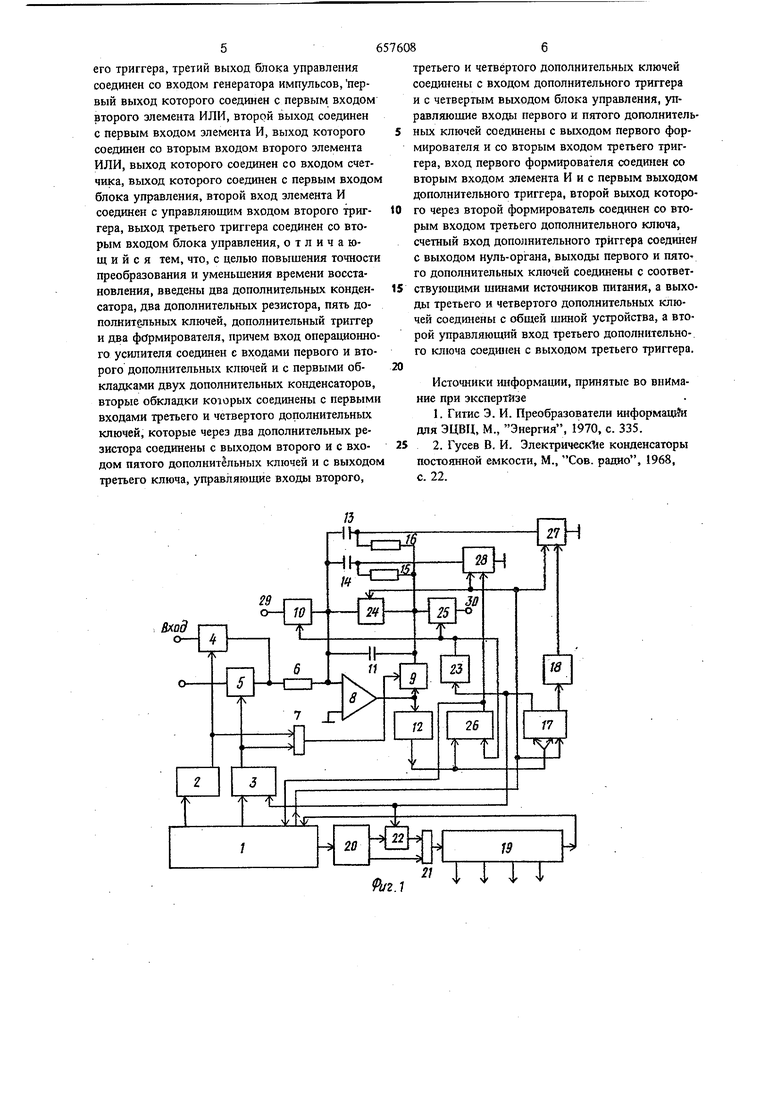

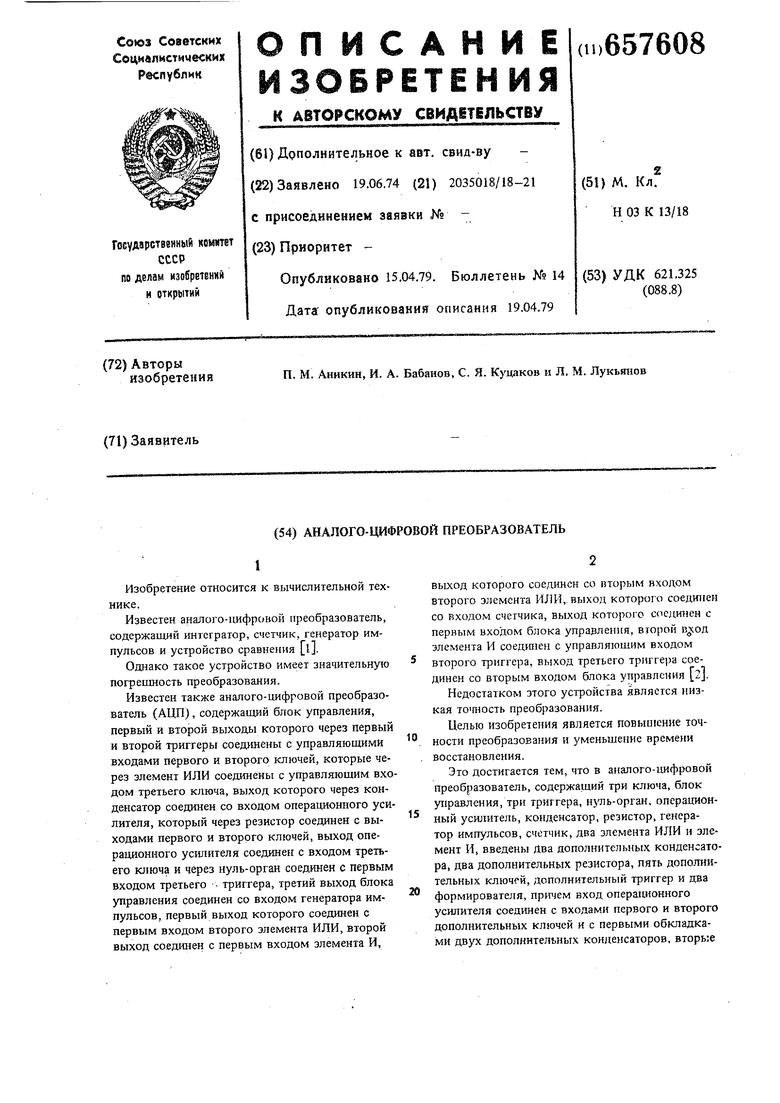

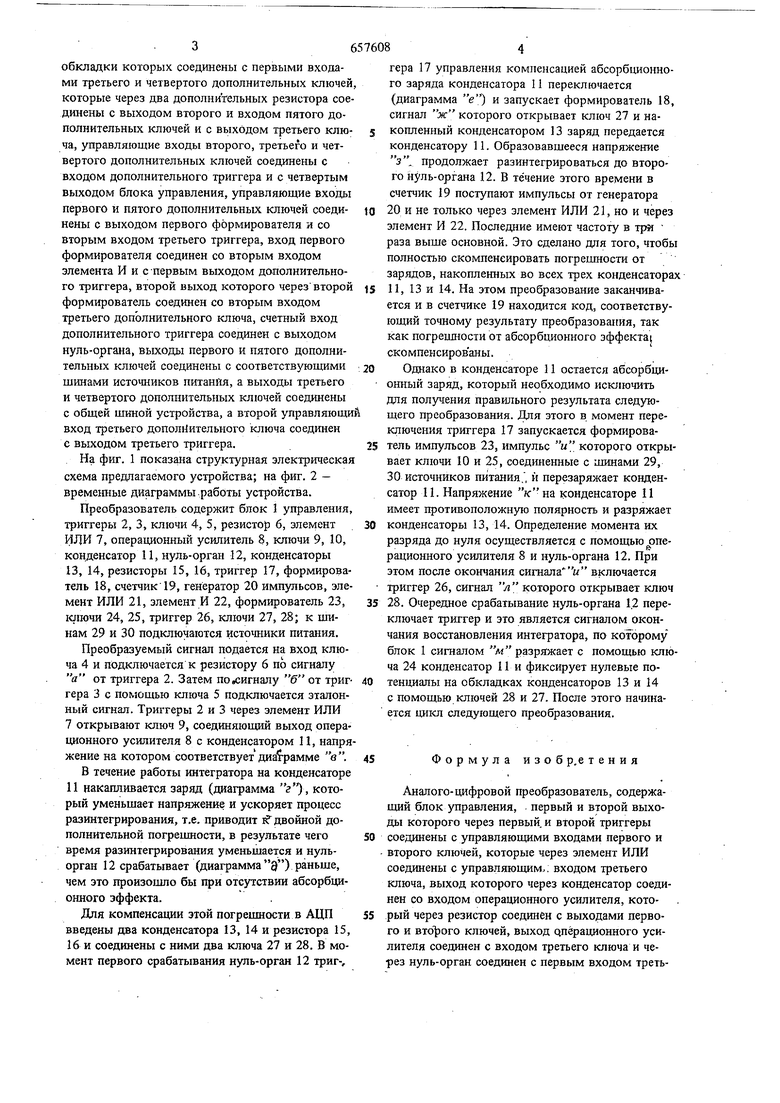

Это достигается тем, что в аналого-цифровой преобразователь, содержащий три ключа, блок управления, три триггера, нуль-орган, операционный усилитель, конденсатор, резистор, генератор импульсов, счетчик, два элемента ИЛИ и элемент И, введены Два допо;итительных конденсатора, два дополнительных резистора, пять дополнительных ключей, дополнительный триггер и два формирователя, причем вход операционного усилителя соед1шен с входами первого и второго дополнительных ключей и с первыми обкладками двух дополннтелы ых конденсаторов, вторь:е 3 обкладки которых соединены с первыми входами третьего и четвертого дополнительных ключей которые через два дополнительных резистора сое динены с выходом второго и входом пятого дополнительных ключей и с выходом третьего ключа, управляющие входы второго, третьего и четвертого дополнительных ключей соединены с входом дополнительного триггера и с четвертым выходом блока управления, управляющие входы первого и пятого дополнительных ключей соединены с выходом первого формирователя и со вторым входом третьего триггера, вход первого формирователя соединен со вторым входом элемента И и с первым выходом дополнительного триггера, второй выход которого черезвторой формирователь соединен со вторым входом третьего дополнительного ключа, счетный вход дополнительного триггера соединен с выходом нудь-органа, выходы первого и пятого дополнительных ключей соединены с соответствующими шинами источников питания, а выходы третьего и четвертого дополнительных ключей соединены с общей шиной устройства, а второй управляющи вход третьего дополнительного ключа соединен с выходом третьего триггера. На фиг. 1 показана структурная электрическая схема предлагаемого устройства; на фиг. 2 време1шые диаграммы работы устройства. Преобразователь содержит блок 1 управления триггеры 2, 3, ключи 4, 5, резистор 6, элемент ИЛИ 7, операдионный усилитель 8, ключи 9, 10, конденсатор 11, нуль-орган 12, конденсаторы 13, 14, резисторы 15, 16, триггер 17, формирователь 18, счетчик 19, генератор 20 импульсов, эле мент ИЛИ 21, элемент И 22, формирователь 23, Ю1ЮЧИ 24, 25, триггер 26, ключи 27, 28; к шинам 29 и 30 подключаются истовдики питания. Преобразуемый сигнал подается на вход ключа 4 и подключается к резистору 6 по сигналу а от триггера 2. Затем поасигнапу 6 от триг гера 3 с помощью ключа 5 подключается эталонный сигнал. Триггеры 2 и 3 через элемент ИЛИ 7 открывают ключ 9, соединяющий выход опера ционного усилителя 8 с конденсатором И, напря жение на котором соответствуетдиа рамме в. В течение работы интегратора на конденсаторе 11 накапливается заряд (диаграмма г), который уменьшает напряжение и ускоряет процесс разинтегрирования, т.е. приводит if двойной дополнительной погрешности, в результате чего время разинтегрирования уменьшается и нульорган 12 срабатывает (диаграмма 9) раньше, чем это произошло бы при отсутствии абсорбционного эффекта. Для компенсации этой погрешности в АЦП введены два конденсатора 13, 14 и резистора 15 16 и соединены с ними два ключа 27 и 28. В момент первого срабатывания нуль-орган 12 триг-. гера 17 управления компенсацией абсорбционного заряда конденсатора 11 переключается (диаграмма е) и запускает формирователь 18, сигнал ж которого открывает ключ 27 и накопленный конденсатором 13 заряд передается конденсатору 11. Образовавшееся напряжение з, продолжает разинтегрироваться до второго нуль-органа 12. В течение этого времени в счетчик 19 поступают импульсы от генератора 20 и не только через элемент ИЛИ 21, но и через элемент И 22. Последние имеют частоту в три раза выше основной. Это сделано для того, чтобы полностью скомпенсировать погрешности от зарядов, накопленных во всех трех конденсаторах 11, 13 и 14. На этом преобразование заканчивается и в счетчике 19 находится код, соответствующий точному результату преобразовшшя, так как погрешности от абсорбционного эффекта ско мпенсированы. Однако в конденсаторе 11 остается абсорбционный заряд, который необходимо исю1ючить для получения правильного результата следующего преобразования. Д1ля этого в момент переключения триггера 17 запускается формирователь импульсов 23, импульс м которого открывает ключи 10 и 25, соединенные с шинами 29, 30 источников питания,, и перезаряжает конденсатор И. Напряжение конденсаторе 11 имеет противоположную полярность и разряжает конденсаторы 13, 14. Определение момента их разряда до нуля осуществляется с помощью операционного усилителя 8 и нуль-органа 12. При этом после окончания cHrHana включается триггер 26, сигнал л которого открывает ключ 28. Очередное срабатывание нуль-органа 12 переключает триггер и это является сигналом окончания восстановления интегратора, по которому блок 1 сигналом « разряжает с помощью ключа 24 конденсатор 11 и фиксирует нулевые потенциалы на обкладках конденсаторов 13 и 14 с помощью ключей 28 и 27. После этого начинается цикл следующего преобразования. Формула изоб р,е тения Аналого-цифровой преобразователь, содержащий блок управления, первый и второй выходы которого через первый, и второй триггеры соединены с управляющими входами первого и второго ключей, которые через элемент ИЛИ соединены с управляющим.: входом третьего ключа, выход которого через конденсатор соединен со входом операционного усилителя, который через резистор соединен с выходами первого и второго ключей, выход рпёрационного усилителя соединен с входом третьего ключа и через нуль-орган соединен с первым входом третьего триггера, третий выход блока управления соединен со входом генератора импульсов, первый выход которого соединен с первым входом второго элемента ИЛИ, второй выход соединен с первым входом элемента И, выход которого соединен со вторым входом второго элемента ИЛИ, выход которого соединен со входом счетчика, выход которого соединен с первым входом блока управления, второй вход элемента И соединен с управляющим входом второго триггера, выход третьего триггера соединен со вторым входом блока управления, отличающийся тем, что, с целью повыщения точности преобразования и уменьшения времени восстановления, введены два дополнительных конденсатора, два дополнительных реэистора, пять дополнительных ключей, дополнительный триггер и два формирователя, причем вход операщюнно го усилителя соединен с входами первого и второго дополнительных ключей и с первыми обкладками двух дополнительных конденсаторов, вторые обкладки которых соединены с первыми входами третьего и четвертого дополнительных ключей, которые череэ два дополнительных резистора соединены с выходом второго и с входом пятого дополнительных ключей и с выходом третьего ключа, управляющие входы второго.

i i IT

J%2J 86 третьего и четвёртого дополнительных ключей соединены с входом дополнительного триггера и с четвертым выходом блока управления, управляющие входы первого и пятого дополнительных ключей соединены с выходом первого формирователя и со вторым входом третьего триггера, вход первого формирователя соединен со вторым входом элемента И и с первым выходом дополнительного триггера, второй выход которого череэ второй формирователь соединен со вторым входом третьего дополнительного ключа, счетный вход дополнительного триггера соединеи с выходом нуль-органа, выходы первого и пято го дополнительных ключей соединены с соответствующими щинами источников питания, а выходы третьего и четвертого дополнительных ключей соединены с общей щиной устройства, а второй управляющий вход третьего дополнительно-. го ключа соедш1ен с выходом третьего триггера. Источники информации, принятые во внимание при экспертизе 1.Гитис Э. И. Преобразователи информации для ЭЦВЦ, М., Энергия, 1970, с. 335. 2.Гусев В. И. Электрическ11е конденсаторы постоянной емкости, М., Сов. радио, 1968, с. 22.

-t

Фиг.2

Авторы

Даты

1979-04-15—Публикация

1974-06-19—Подача