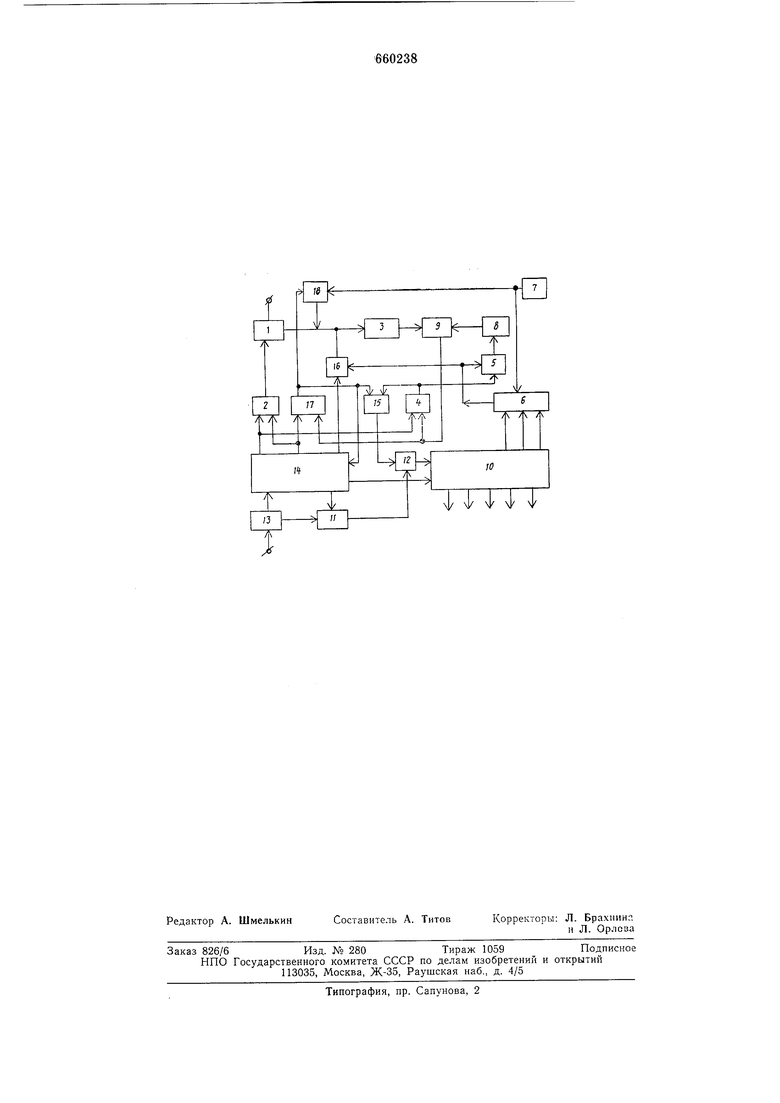

входом нуль-органа. Второй вход второго ключа соединен с пятым выходом блока управления, а выход соединен с входом интегратора, первый вход дополнительного триггера соединен с выходом нуль-органа, а второй вход соединен с первым входом второго триггера. Структурная электрическая схема устройства приведена на чертеже. Устройство содержит переключатель 1, триггер 2, интегратор 3, триггер 4, ключ 5, цифро-аналоговый преобразователь 6, источник 7 эталонного сигнала, квадратор 8, нуль-орган 9, счетчик 10, генератор И импульсов, элемент И 12, блок 13 выделения периода помехи, блок 14 управления, элемент ИЛИ 15, ключ 16, триггер 17 и переключатель 18. Входной сигнал с помощью переключателя 1, управляемого триггером 2, подключается к интегратору 3, интегрирование выполняется в течение времени, равного периоду помехи. С момента начала интегрирования включается триггер 4, выходной сигнал которого открывает ключ 5. Через ключ 5 сигнал с выхода цифро-аналогового преобразователя 6, полученный в результате деления сигнала от источника 7, поступает на квадратор 8, а с выхода последнего на вход нуль-органа 9. Цифро-аналоговый преобразователь 6 соединен со старшими разрядами счетчика 10, начиная с га-го разряда, он имеет л - т разрядов, где п - число разрядов счетчика 10. Сигнал на выходе цифро-аналогового преобразователя 6 изменяется ступенчато через интервал где 2и - период новторения импульсов генератора И. Ири этом блок 13 обеспечивает выполнение условия „ 2-2 -/240 где tn - период помехи. Выходные напряжения квадратора 8 и интегратора 3 сравниваются на нуль-органе 9. После срабатывания нуль-органа переключается триггер 4, который выключает через ключ 5 квадратор 8 и через элемент ИЛИ 15 и элемент И 12 счетчик 10, сохраняя накопленное в старших разрядах значение кода. По достижении интервала времени, равного блок 14 открывает ключ 16 на время окончания интегрирования. В течение этого времени происходит интегрирование входного сигнала и сигнала с выхода цифро-аналогового преобразователя 6. После этого сигналы отключаются от интегратора 3 и по сигналу триггера 17 открывается переключатель 18, подключаюш,ий сигналы от источника 7 на вход интегратора 3. По этому же сигналу открывается элемент И 12, разрешая счет в счетчике 10. Процесс разинтегрирования заканчивается по сигналу нуль-органа 9. К этому моменту в счетчике 10 хранится код точного результата преобразования, процесс интегрирования и разинтегрирования продолжается в течение почти одинаковых интервалов времени, что уменьшает погрешность из-за нелинейности интегратора 3. Формула изобретения Аналого-цифровой преобразователь, содержащий первый переключатель, выход которого соединен с выходом второго переключателя и с входом интегратора, выход которого соединен с первым входом нульоргана, выход которого соединен с первым входом первого триггера, второй вход которого соединен с первым выходом блока управления, первый вход которого через последовательно соединенные блок выделения периода помехи и генератор импульсов соединен с первым входом элемента И, второй вход которого соединен с выходом элемента ИЛИ, а выход соединен с управляющим входом счетчика, информационные выходы которого соединены с информационными входами цифро-аналогового преобразователя, управляющий вход которого соединен с выходом источника эталонного сигнала и с первым входом второго переключателя, второй вход которого соединен с выходом первого триггера и с первым входом элемента ИЛИ, первый вход второго триггера соединен с вторым выходом блока управления, второй вход второго триггера соединен с первым выходом блока управления, а выход соединен с входом первого переключателя, второй в-ход блока управления соединен с первым входом элемента ИЛИ, третий выход блока управления соединен с входом счетчика, а четвертый выход соединен с унравляющим входом генератора импульсов, отличающийся тем, что, с целью повышения точности и быстродействия, в него дополнительно введены квадратор, два ключа и дополнительный триггер, выход цифро-аналогового преобразователя соединен с первыми входами двух ключей, второй вход первого ключа соединен с выходом дополнительного триггера и с вторым входом элемента ИЛИ, а выход первого ключа через квадратор соединен с вторым входом нуль-органа, второй вход второго ключа соединен с пятым выходом блока управления, а выход соединен с входом интегратора, первый вход дополнительного триггера соединен с выходом нуль-органа, а второй вход соединен с первым входом второго триггера. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР Л 312279, кл. G 06Y 3/00, 10.06.70. 2.Авторское свидетельство СССР № 347909, кл. Н ОЗК 13/20, 09.08.68.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь компенсационного интегрирования | 1974 |

|

SU764126A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU657608A1 |

| Цифровой измеритель коэффициента мощности | 1977 |

|

SU746314A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1124346A1 |

| Цифровой измеритель активных сопротивлений | 1985 |

|

SU1308936A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| Аналого-цифровое интегрирующее устройство | 1980 |

|

SU868784A1 |

| Квадратирующий аналого-цифровой преобразователь | 1982 |

|

SU1051548A1 |

| Множительно-делительное устройство | 1977 |

|

SU696444A1 |

Авторы

Даты

1979-04-30—Публикация

1974-06-10—Подача