Изобретение относится к технике цифровых систем передачи сигналов телевидения и может быть использовано в системах связи с импульсно-кодовой модуляцией.

Известен способ передачи двоичных сигналов по меньшей мере двух каналов, в состав устройства, реализующего который, входят мультиплексор, скремблер, схема блочного кодирования, генератор кода признака на передаче и дешифратор, детектор кода признака, дескpемблер, демультиплексор.

Данное устройство отличается тем, что длина блока схем блочного кодирования и декодирования, длительность цикла мультиплексора и демультиплексора, а также период ПСП-скремблера и дескремблера находятся в постоянном целочисленном соотношении.

Однако в таком устройстве для различения двух каналов требуется передача специальной синхроинформации, что снимает помехоустойчивость передачи и эффективность использования канала связи, а для скремблирования (дескpемблирования) используется генератор ПСП, что усложняет устройство и также требует передачи сигналов синхронизации.

Известна система связи со скремблированием сигнала, в состав которой входят блок памяти и генератор псевдослучайной последовательности на передаче и приеме.

В системе скремблирование осуществляется перемешиванием по квазислучайному закону двоичных кодовых комбинаций исходного информационного сигнала, тем самым достигается перемешивание без использования специального скремблера, приводящего к размножению ошибок, возникающих в канале. Однако требуется передача специальных сигналов синхронизации и не решается вопрос скремблирования, передачи и разделения на приеме сигналов нескольких каналов. Кроме того, применительно к цифровому телевизионному сигналу можно упростить алгоритм размешивания за счет использования статистических свойств цифрового ТВ-сигна- ла.

Прототипом является система передачи и приема сигналов изображения, содержащая на передающей стороне аналого-цифровой преобразователь, вход которого соединен с шиной входного сигнала, а выходы через коммутатор и преобразователь параллельного кода - в последовательный со входом канала связи. Выход генератора псевдослучайной последовательности подключен к управляющему входу коммутатора. На приемной стороне имеется преобразователь последовательного кода в параллельный, вход которого соединен с выходом канала связи, а выходы через второй коммутатор и цифроаналоговый преобразователь соединены с шиной выходного сигнала, выход второго генератора псевдослучайной последовательности соединен с управляющим входом второго коммутатора, выходы которого соединены соответственно с первыми входами сумматоров по модулю два и входами элементов задержки, выходы которых подключены к вторым входам сумматоров по модулю два, выходы которых через соответствующие интеграторы соединены с входами компараторов, выходы которых подключены к входам элемента И, выход которого соединен с управляющим входом второго генератора псевдослучайной последовательности. Кроме того, имеются последовательно соединенные дополнительные сумматор по модулю два, интегратор и компаратор, причем входы дополнительного сумматора по модулю два соединены с первым и последним выходами преобразователя последовательного кода в параллельный, а выход дополнительного компаратора соединен с соответствующим входом преобразователя последовательного кода в параллельный.

Таким образом, повышается помехоустойчивость системы и точности передачи изображения, поскольку исключается необходимость передачи специальных служебных посылок для целей обеспечения цикловой синхронизации приемной части системы: как в части преобразователя последовательного кода в параллельный, так и коммутатора, реализующего вместе с генератором псевдослучайной последовательности функцию дескремблера цифрового сигнала изображения. Кроме того, скремблирование осуществляется путем изменения позиций разрядов в пределах кодовой группы по псевдослучайному закону или путем циклической перестановки разрядов, поэтому исключается размножение ошибок при передаче по каналу связи как это происходит, например, при использовании самосинхронизирующегося скремблера (дескремблера).

Однако при кодировании и передаче в составе единого группового цифрового потока нескольких, например, двух телевизионных программ, не решена задача эффективного скремблирования и выделения обеих ТВ-программ без использования дополнительных сигналов цикловой синхронизации и генераторов ПСП, что снижает эффективность и помехоустойчивость предложенных решений, а также не решена задача передачи дополнительной цифровой информации с сохранением свойств сбалансированности цифрового сигнала.

Целью изобретения является повышение помехоустойчивости при одновременном расширении функциональных возможностей системы при цифровой передаче и приеме нескольких, например двух, телевизионных программ в одном групповом цифровом потоке. Достигается это тем, что в систему передачи и приема телевизионных сигналов, содержащую на передающей стороне - первый n-разрядный аналого-цифровой преобразователь (АЦП), вход которого является входом первого телевизионного сигнала, а выход первого разряда соединен через первый вход первого коммутатора с первым входом преобразователя параллельного кода и последовательный, выход которого является выходом передающей стороны, а на приемной стороне - преобразователь последовательного кода в параллельный, сигнальный вход которого является входом приемной стороны, а выход соединен через первый вход первого коммутатора с первым входом первого цифроаналогового преобразователя (ЦАП), выход которого является выходом первого телевизионного сигнала, первый элемент И, последовательно соединенные первый сумматор по модулю два, первый интегратор и первый компаратор, второй сумматор по модулю два и последовательно соединенные третий сумматор по модулю два, второй интегратор и второй компаратор, отличающаяся тем, что, с целью повышения помехоустойчивости и расширения функциональных возможностей, введены на передающей стороне - второй n-разрядный АЦП, вход которого является входом второго телевизионного сигнала, (2n-1) коммутаторов, (n+2) элементов НЕ, задающий генератор, счетный триггер и сумматор по модулю два, первый выход первого АЦП соединен с вторым входом второго коммутатора, каждый выход первого АЦП, начиная со второго, соединен с первым входом соответствующего нечетного и вторым входом соответствующего четного коммутаторов, а каждый выход второго АЦП, начиная с n-го в обратном порядке соединен с вторым входом соответствующего нечетного и первым входом соответствующего четного коммутаторов, управляющие входы котоpых соединены с соответствующим входом сумматора по модулю два и выходов счетного триггера, вход которого соединен с тактовыми входами первого и второго АЦП и выходом задающего генератора, второй выход которого соединен с тактовым входом преобразователя параллельного кода в последовательный, n-первых сигнальных входов которого соединены с n-первыми сигнальными входами сумматора по модулю два и выходами соответствующих нечетных коммутаторов, и выходы четных коммутаторов соединены с входами первых n-элементов НЕ, выходы которых соединены с вторыми сигнальными n-входами преобразователя параллельного кода в последовательный, первый и второй управляющие входы которого соединены соответственно с выходом сумматора по модулю два непосредственно и через (n+1)-й элемент НЕ, третий управляющий вход является входом цифрового сигнала и соединен с (n+2)-м элементом НЕ, выход которого соединен с четвертым управляющим входом преобразователя параллельного кода в последовательный код, а на приемной стороне введены второй n-разрядный ЦАП, (2n-1) коммутаторов, n элементов НЕ, четвертый сумматор по модулю два, первый и второй входы которого соединены с выходами первого и второго компараторов, селектор тактовой частоты, вход которого соединен с первым входом преобразователя последовательного кода в параллельный, первый, второй и третий счетчики, делитель частоты, вход которого соединен с первым входом первого счетчика и первым выходом селектора тактовой частоты, счетный триггер, выход которого соединен с первым управляющим входом второго сумматора по модулю два и управляющими входами каждого коммутатора, D-триггер, вход которого соединен с первым входом счетного триггера и выходом третьего счетчика, а выход является выходом сигнала технической исправности канала, второй и третий элементы И, выходы которых соединены соответственно со вторым и третьим входами первого счетчика, и элемент ИЛИ, первый и второй входы которого соединены с соответствующими входами четвертого сумматора по модулю два, а выход - соединен с четвертым входом первого счетчика, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с вторым выходом селектора тактовой частоты, второй вход преобразователя последовательного кода в параллельный соединен с выходом первого элемента И, а третий вход - соединен со вторым входом счетного триггера, входами второго и третьего счетчиков, тактовыми входами первого и второго n-разрядных ЦАП и выходом делителя частоты, первый выход преобразователя последовательного кода в параллельный соединен с вторым входом второго коммутатора, первый вход которого соединен с вторым входом первого коммутатора и выходом первого элемента НЕ, каждый нечетный выход преобразователя последовательного кода в параллельный, начиная с третьего до (2n-1)-го, соединен с первым входом соответствующего четного и вторым входом соответствующего нечетного коммутаторов, начиная с третьего, каждый четный выход преобразователя последовательного кода в параллельный соединен с входом каждого элемента НЕ, при этом выход каждого элемента НЕ, начиная со второго, соединен с вторым входом соответствующего нечетного и первым входом соответствующего четного коммутатора, (2n+1) выход преобразователя последовательного кода в параллельный соединен соответственно с первым входом первого сумматора по модулю два и вторым входом второго сумматора по модулю два, (2n+2)-ой выход соединен с вторым входом первого сумматора по модулю два, (2n+3)-й выход - с первым входом третьего сумматора по модулю два и является выходом цифрового сигнала, (2n+4)-й выход соединен с вторым входом третьего сумматора по модулю два, первый и второй входы второго элемента И соединены соответственно с первым входом и выходом четвертого сумматора по модулю два, который также соединен с первым входом третьего элемента И, второй вход которого соединен с вторым входом четвертого сумматора по модулю два, выход каждого нечетного коммутатора, начиная с третьего, соединен с (n-1)-ми сигнальными входами первого n-разрядного ЦАП и n-первыми сигнальными входами второго сумматора по модулю два, n-вторых сигнальных входов которого соединены с n-входами второго n-разрядного ЦАП и выходами соответственно каждого четного коммутатора, начиная с (n-1)-го, выход второго сумматора по модулю два соединен с вторым входом третьего счетчика, третий вход которого соединен с выходом второго счетчика, а выход второго n-разрядного ЦАП является выходом второго телевизионного сигнала.

Сущность изобретения заключается в том, что при цифровой передаче нескольких, например двух телевизионных программ в одном групповом цифровом потоке, скремблирование цифрового сигнала производится путем перемежения и инверсии по определенному правилу статистически независимых разрядных последовательностей, получаемых с выходов АЦП и относящихся к различным ТВ-программ. При этом отпадает необходимость использовать генераторы псевдослучайных последовательностей на передаче и приеме. Синхронизация приемного преобразователя из последовательного кода в параллельный и коммутаторов разрядных последовательностей осуществляется за счет выявления и анализа на приеме цифровых сигналов контроля четности и цифрового сигнала звукового сопровождения, представленных каждый в прямом и инверсном виде и размещенных на определенных позициях группового цифрового потока. Тем самым повышается помехоустойчивость, сокращается время вхождения в синхронизм и расширяются функциональные возможности устройства.

Других известных технических решений с признаками, сходными с признаками, отличающими заявляемое техническое решение от прототипа, при поиске не обнаружено, следовательно, заявляемое техническое решение обладает существенными отличиями.

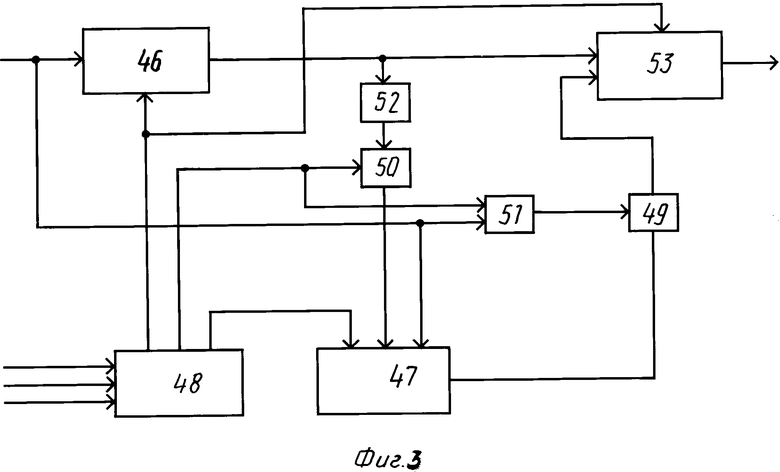

На фиг. 1 представлена структурная схема передающей части системы цифровой передачи и приема телевизионных сигналов; на фиг. 2 - структурная схема приемной части системы цифровой передачи и приема телевизионных сигналов; на фиг. 3 - структурная схема счетчика 42.

Система цифровой передачи и приема телевизионных сигналов содержит на передаче шины 1 и 2 входных телевизионных сигналов, первый 3 и второй 4 аналого-цифровые преобразователи (АЦП), генератор 5 задающий, счетный триггер 6, n нечетных коммутаторов 7, n четных коммутаторов 8, n элементов НЕ 9, сумматор 10 по модулю 2, (n+1)-й элемент НЕ 11, (n+2)-ой элемент НЕ 12, преобразователь параллельного кода в последовательный 13, шина 14 входного цифрового сигнала, шина 15 входа линии связи, шина 16 выхода линии связи, преобразователь 17 последовательного кода в параллельный, n элементов НЕ 18, n нечетных коммутаторов 19, n четных коммутаторов 20, первый 21 и второй 22 цифроаналоговый преобразователь, шины 23 и 24 выходных ТВ-сигналов, селектор 25 тактовой частоты, первый элемент И 26, делитель частоты 27, счетный триггер 28, второй сумматор 29 по модулю два, третий счетчик 30, второй счетчик 31, первый сумматор 32 по модулю два, третий сумматор 33 по модулю два, первый интегратор 34, второй интегратор 35, первый компаратор 36, второй компаратор 37, четвертый сумматор 38 по модулю два, элемент ИЛИ 39, второй элемент И 40, третий элемент И 41, первый счетчик 42, шина 43 сигнала технической исправности канала (СТИК), шина 44 выходного цифрового сигнала, D-триггер 45. В состав счетчика 42 входят первый 46 и второй 47 делители частоты дешифратор 48, два элемента ИЛИ 49 и 50, элемент И 51 и элемент НЕ 52.

R-S-триггер 53. Шина 1 входного телевизионного сигнала соединена с входом первого n-разрядного аналого-цифрового преобразователя (АЦП) 3, а шина 2 - второго (n-разрядного аналого-цифрового преобразователя 4. Выход каждого разряда первого АЦП 3, начиная с первого в прямом порядке, соединен с первым входом соответствующего коммутатора 7 и вторым входом следующего коммутатора 8. Выход каждого разряда второго АЦП 4, начиная с последнего, n-го, в обратном порядке соединен с вторым входом соответствующего коммутатора 7 и первым входом следующего коммутатора 8. Выходы всех нечетных коммутаторов 7 подключены к первым n-входам сумматора 10 по модулю два и нечетным входам (2n+4) разрядного преобразователя 13 из параллельного кода в последовательный. Выходы всех четных коммутаторов 8 подключены через соответствующие элементы НЕ 9 к вторым n входам сумматора 10 по модулю два и четным входам (2n+4) разрядного преобразователя 13 из параллельного кода в последовательный. При этом входы (n-1), n, (2n+3), (2n+4) преобразователя 13 пропускаются. Выход генератора 5 задающего соединен с управляющими входами первого 3 и второго 4 АЦП и через счетный триггер 6 с управляющими входами всех коммутаторов 7 и 8 и (2n+1)-м входом сумматора 10 по модулю два, выход которого соединен с (n-1)-м входом преобразователя 13 непосредственно, а с n-ым входом - через (n-1)-й элемент НЕ 11. Шина 14 входного цифрового сигнала соединена с (2n+3)-входом преобразователя 13 непосредственно, а с (2n+4)-м - через (n+2)-й элемент НЕ 12. Выход преобразователя 13 соединен с шиной 15 входа канала связи, а управляющий вход - с вторым выходом генератора 5 задающего. Шина 16 выхода канала связи соединена с входом преобразователя 17 из последовательного кода в параллельный и через выделитель 25 тактовой частоты и первый элемент И 26 - с первым управляющим входом преобразователя 17, второй управляющий вход которого соединен через делитель 27 частоты с вторым выходом селектора 25 тактовой частоты и входом первого счетчика 42, а непосредственно - с входом счетного триггера 28, второго счетчика 31 и управляющими входами первого 21 и второго 22 цифроаналогового преобразователя, выходы которых подключены к соответствующим шинам 23 и 24 выходного ТВ-сигнала. Выход счетного триггера соединен с управляющими входами всех компараторов 19 и 20 и через второй сумматор 29 по модулю два и третий счетчик 30, второй вход которого соединен с выходом второго счетчика 31, соединен с вторым входом счетного триггера 28 и шиной 43 сигнала технической исправности канала, 2 n выходов (2n+4)-х разрядного преобразователя 17 за исключением n, (n-1), (2n+3) и (2n+4) выходов соединены с входами соответствующих коммутаторов 19 и 20, причем нечетные выходы - с первым входом соответствующего коммутатора 19 и вторым входом следующего коммутатора 20, а четные выходы - через соответствующий элемент НЕ 18 со вторым входом соответствующего коммутатора 19 и первым входом следующего коммутатора 20. Выходы нечетных коммутаторов 19 подключены в прямом порядке к n входам первого цифроаналогового преобразователя 21, выход которого соединен с шиной 23 выходного сигнала, и к первым n входам второго сумматора 29 по модулю два. Выходы четных коммутаторов 20 подключены в обратном порядке к входам второго цифроаналогового преобразователя 22, выход которого соединен с шиной 24 выходного сигнала и к вторым n входам второго сумматора 29 по модулю два. Выход (n-1) преобразователя 17 соединен с входом (2n+2) второго сумматора 29 по модулю два и первым входом первого сумматора 32 по модулю два, второй вход которого соединен с n-ым выходом преобразователя 17, (2n+3) и (2n+4)-й выходы которого через третий сумматор 33 по модулю два, второй интегратор 35, второй компаратор 37 соединены с вторым входом четвертого сумматора 38 по модулю два, первый вход которого через первый компаратор 36, первый интегратор 34 соединен с выходом первого сумматора 32 по модулю два. Выход четвертого сумматора 38 по модулю два через второй 40 и третий 41 элементы И с вторым и третьим соответственно входами первого счетчика 42, четвертый вход которого через элемент ИЛИ 39 соединен соответственно с вторыми входами второго 40 и третьего 41 элементов И и первым и вторым входами четвертого сумматора 38 по модулю два, а (2n+3)-й выход преобразователя 17 соединен с шиной 44 выходного цифрового сигнала.

Устройство работает следующим образом.

На шину 1 входного сигнала подается первый телевизионный сигнал, а на шину 2 входного сигнала - второй ТВ-сигнал. Эти ТВ-сигналы в первом АЦП 3 и втором АЦП 4 подвергаются аналого-цифровому преобразованию в цифровой n-разрядный код, например n-8. Далее сигнал с выхода 1-го разряда первого АЦП 3 подается на первый вход первого из нечетных компараторов 7 и второй вход первого из четных коммутаторов 8, а сигнал с выхода n-го (например, 8-го) разряда второго АЦП 4 подается на второй вход первого из нечетных коммутаторов 7 и первый вход первого из четных коммутаторов 8. Сигнал с выхода 2-го разряда первого АЦП 3 подается на первый вход второго из нечетных коммутаторов 7 и второй вход второго из четных коммутаторов 8, а сигнал с выхода (n-1)-го (например, 7-го) разряда второго АЦП 4 подается на второй вход второго из нечетных коммутаторов 7 и первый вход второго из четных коммутаторов 8 и т. д. Наконец сигнал с выхода n-го (например, 8-го) разряда первого АЦП 3 подается на первый вход n-го (например, 8-го) из нечетных коммутаторов 7 и второй вход n-го (например, 8-го) из четных коммутаторов 8, сигнал с выхода 1-го разряда второго АЦП 4 подается на второй вход последнего n-го из нечетных коммутаторов 7 и первый вход последнего n-го из четных коммутаторов 8.

Сигнал тактовой частоты от генератора 5 задающего поступает на управляющие входы АЦП 3 и 4, определяя частоту временной дискретизации ТВ-сигнала и, следовательно, частоту формирования параллельного кода на выходах обeих АЦП. Сигнал с выхода генератора 5 через счетный триггер 6 с частотой, поделенной на два, поступает на управляющие входы всех нечетных 7 и четных 8 компараторов. Таким образом, каждый, например четный такт на выход нечетных коммутаторов 7, проходит разряды первого АЦП 3 с первого по n-ый, а на выход четных коммутаторов 8 разряды второго АЦП 4 с n-го по первый, а каждый нечетный коммутатор 7 разряды второго АЦП 4 с n-го по первый, на выход четных коммутаторов 8 разряды первого АЦП 3 с первого по n-ый. Эти сигналы поступают на нечетные входы преобразователя 13 из параллельного кода в последовательный с выходов нечетных коммутаторов 7 непосредственно, а на четные входы - с выходов четных коммутаторов 8 через соответствующие элементы НЕ 9. При этом входы (n-1), n (2n+3), (2n+4) преобразователя 13 пропускаются. Порядок подключения разрядов АЦП 3 (а1÷ аn) и АЦП 4 (b1÷ bn) показан для n-8 в таблице 1, знак а1 означает инверсию разряда.

Таким образом, при преобразовании в последовательный код старшие, наиболее коррелированные разряды (например, а1, а2), одного АЦП будут перемежаться с младшими наименее коррелированными разрядами (например, b8, b7) другого АЦП, что с учетом статистической независимости разрядных последовательностей на выходах разных АЦП дает эффект скремблирования группового цифрового потока. Инверсия разрядов и изменение порядка следования от такта к такту (см. табл. 1) позволяет подавить эффект от сильных межэлементных корреляционных связей в сигнале изображения и избежать возникновения длинных последовательностей единиц или нулей в групповом цифровом потоке при отсутствии ТВ-сигнала на входах АЦП 3 и 4.

Цифровые сигналы со всех входов преобразователя 13, указанных в табл. 1, подаются на 2n-входов сумматора 10 по модулю два для формирования сигнала контроля чeтности. Кроме того, на (2n+1) вход сумматора 10 подан сигнал с выхода счетного триггера 6 с целью последующего извлечения его из сигнала контроля четности на приеме для синхронизации работы коммутаторов 7, 8 на передаче и 19, 20 на приеме.

Сигнал контроля четности с выхода сумматора 10 подается в прямом виде на (n-1)-вход, а в инверсном через элемент НЕ 11 - на n-й вход преобразователя. Поступающий на входную шину 14 цифровой сигнал например, цифровой сигнал звукового сопровождения, подается в прямом виде на (2n+3)-вход, а в инверсном виде через элемент НЕ 12 - на (2n+4)-вход преобразователя 13. Эти сигналы сохраняют сбалансированность группового цифрового потока, так как вводятся в прямом и инверсном виде, а также обеспечивают эффективную цикловую синхронизацию приемного преобразователя 17 из последовательного кода в параллельный. Групповой цифровой поток ГЦП поступает на шину 15 входа канала связи.

С шины 16 выхода канала связи ГЦП поступает на входы преобразователя 17 из последовательного кода в параллельный и выделителя 25 тактовой частоты ГЦП. С выхода селектора 25 через делитель 27 частоты сигнал поступает на входы преобразователя 17, счетного триггера 28, первого и второго 22 ЦАП и счетчика 31 интервала контроля. Частота сигнала на выходе делителя 27 равна частоте временной дискретизации ТВ сигнала в АЦП 3 и 4 на передающей стороне. Сигнал с выхода счетного триггера 28 с частотой, равной частоте дискретизации, деленной на два, поступает на управляющие входы всех нечетных 19 и четных 20 компараторов. При синхронной работе преобразователей 13 и 17 на выходах преобразователя 17 формируются цифровые сигналы в соответствии с таблицей, т. е. таким же образом как на входах преобразователя 13. Затем сигнал с первого выхода преобразователя 17 подается на первый вход первого из нечетных коммутаторов 19 и второй вход первого из четных коммутаторов 20. Сигнал со второго выхода преобразователя 17 подается через соответствующий элемент НЕ 18 на второй вход первого из нечетных коммутаторов 19 и первый вход первого из четных коммутаторов 20 и т. д. Сигнал с (2n+1) выхода преобразователя 17 подается на первый вход последнего n-го из четных коммутаторов 20, а сигнал с (2n+2)-го выхода преобразователя 17 подается через соответствующий элемент НЕ 18 на второй вход последнего из нечетных коммутаторов 19 и первый вход последнего из четных коммутаторов 20. При синхронной работе счетных триггеров 28 и 6 разрядные последовательности a1÷an подключаются к соответствующим входам первого ЦАП 21, а b1÷bn - второго ЦАП 22. В ЦАП 21 и 22 производится восстановление первого и второго телевизионного сигналов.

Рассмотрим работу цепей синхронизации приемного преобразователя 17 из параллельного кода в последовательный. Сигнал контроля четности при синхронной работе преобразователей 13 и 17 с (n-1)-го и n-го выходов преобразователя 17, представленный соответственно в прямом и инверсном виде, поступает на входы первого сумматора 32 по модулю два, с выхода которого логическая "1" (поскольку на входах сумматора 32 всегда взаимно инверсные посылки) поступает на первый интегратор 34 и далее на компаратор. На выходе интегратора формируется максимальное напряжение Uмакс Uпор, где Uпор - порог срабатывания первого компаратора 36, на выходе которого формируется логическая "1". Аналогично цифровой сигнал звукового сопровождения с (2n+3) и (2n+4) выходов преобразователя 17, представленный соответственно в прямом и инверсном виде, поступает на третий сумматор 33 по модулю два и далее, как и для сигнала контроля частности через второй интегратор 35 - второй компаратор 37, на выходе которого формируется логическая "1". Сигналы с выходов компараторов 36 и 37 через четвертый сумматор 38 по модулю два (на выходе которого - логический "0") поступают на первые входы элементов И 40 и 41, запрещая прохождения логических "1" с выходов компараторов 36 и 37 на соответственно второй и третий управляющие входы первого счетчика 42, на четвертый управляющий вход которого, запрещающий работу счетчика 42, поступает логическая "1" с выхода элемента ИЛИ, входы которого соединены с выходами первого 36 и второго 37 компаратора. Логическая "1" с выхода счетчика 42 поступает на первый вход первого элемента И, разрешая прохождение через него сигнала управления с частотой группового цифрового потока с выхода выделителя 25 тактовой частоты на первый вход преобразователя 17, тем самым обеспечивая продолжение его синхронной работы. Стробирование выходного (2n+4) разрядного параллельного кода осуществляется сигналом управления с выхода делителя 27 частоты.

При несинхронной работе преобразователя 17, кода на n-1, n, 2n+3, 2n+4 его выходах не обнаруживаются парафазные сигнал контроля чeтности и цифровой сигнал звукового сопровождения, на выходах первого 36 и второго 37 компараторов и четвертого сумматоров 38 по модулю два формируются логические "0". В этом случае на второй, третий и четвертый выходы управления счетчика 42 поданы логические "0", что обеспечивает переводы его в режим деления частоты. При этом на выходе счетчика 42 периодически (период определяется коэффициентом деления и связан с постоянной времени интеграторов 34 и 35) формируется импульс длительностью в такт группового потока, запрещающий прохождение очередного импульса с выхода селектора 25 тактовой частоты через элемент И 26 на первый управляющий вход преобразователя 17. Таким образом, осуществляется сдвиг разрядных последовательностей на выходах преобразователя 17. Эта процедура (сдвиг и анализ элементами 32-38) повторяется несколько раз до тех пор, пока по крайней мере на одной из пары выходов: (n-1), n, или (2n+3), (2n+4) не появится парафазный сигнал. Пусть, например, парафазный цифровой сигнал звукового сопровождения обнаружен на выходах (n-1), n-цепью первый сумматор 32, первый интегратор 34, первый компаратор 36; на выходах (2n+3), (2n+4) парафазный сигнал цепью аналогичных элементов 33 35, 37 не обнаруживается. В этом случае на выходе сумматора 38 по модулю два формируется логическая "1" (на выходе компаратора 36-"1", а компаратора 37-"0"), на второй и четвертый входы счетчика 42 поступают логические "1", а на третий - логический "0". Далее счетчик 42 формирует на своем выходе импульс длительностью K тактов группового цифрового потока, запрещая прохождение соответствующего количества импульсов с выхода селектора 25 тактовой частоты через элемент И 26 на преобразователь 17. Таким образом осуществляется сдвиг разрядных последовательностей на выходах преобразователя, вплоть до обнаружения обоих парафазных сигналов на выходах соответственно (2n+3), (2n+4) и (n-1), n, что означает окончание поиска синхронизма. Если, например, парафазный цифровой сигнал контроля четности обнаружен на выходах (2n+3), (2n+4), тогда на выходах (n-1), n парафазный сигнал не обнаруживается. В предыдущем и данном случае это связано с преднамеренно несимметричным расположением разрядов с парафазными сигналами относительно начала и конца (2n+4) разрядной кодовой группы. В последнем случае процедура поиска синхронизма аналогична, однако при поиске логические "1" формируются на третьем и четвертом входах счетчика 42, а на его втором входе - "0". На его выходе формируется импульс длительностью l тактов группового сигнала. В предыдущем случае K, например, равно n+4, а во втором l равно n. Таким образом, осуществляется ускоренный поиск синхронизма преобразователя 17.

Рассмотрим работу цепей синхронизации счетного триггера 28. Сигналы с выходов всех 2n коммутаторов 19 и 20, а также с выхода счетного триггера 28 подаются на входы второго сумматора 29 по модулю два. Кроме того, на (2n+2) вход сумматора 29 поступает сигнал контроля четности, сформированный на передаче сумматором 10 по модулю два. При синхронной работе счетных триггеров 6 и 28 и отсутствии ошибок передачи группового цифрового сигнала на выходе сумматора 29 формируется логический "0". Вход сумматора 29 соединен с входом счетчика накопителя 30, в котором осуществляется накопление ошибок передачи за определенный интервал, определяемый вторым счетчиком 31 интервала контроля, на вход которого подан сигнал с частотой следования параллельного кода на входах ЦАП 22 и 21. Например, накопление 8÷10 импульсов ошибок за 5000 тактовых интервалов параллельного кода будет означать снижение достоверности передачи до значений 10-4 и ниже. При этом имеется ввидy, что наиболее вероятно поражение только одного разряда 20-ти разрядного параллельного кода. При несинхронной работе счетного триггера 28 возникает непрерывный поток ошибок - логическая "1" на выходе сумматора 29 и счетчик 30 быстро заполняется импульсами тактового сигнала, поступающими от делителя 27 частоты. На выходе счетчика 30 формируется логическая "1", которая поступает на вход Д-триггера 45 и на второй управляющий вход счетного триггера 28, обеспечивая его переключение фронтом 0 ->> 1 в противоположное состояние. Далее очередным импульсом по основному первому входу триггер 28 возвращается в то же состояние, какое у него было в начале предыдущего основного такта, и происходит смена фазы работы триггера 28 и вход его в синхронизм с триггером 6 на передаче. При недопустимом снижении достоверности передачи группового цифрового сигнала счетчик-накопитель 30 будет заполняться на каждом интервале контроля и при установке его в нулевое состояние импульсом от счетчика 31 интервала контроля, фронтом 1 ->> 0 будет осуществляться периодическая смена фазы работы счетного триггера 28. Однако этот процесс прекращается как только достоверность передачи станет выше пороговой, например 10-4. В D-триггер 45 импульсом со счетчика 31 осуществляется запись состояния счетчика 30 в конце интервала контроля. Таким образом, на выходе D-триггера 45 формируется сигнал технической исправности канала (СТИК), который подается на выходную шину 43. При недопустимом снижении достоверности передачи цифрового сигнала на этой шине сохраняется логическая "1", вплоть до устранения неисправности.

Счетчик 42 работает следующим образом (фиг. 3).

Сигнал тактовой частоты группового цифрового потока, поступающий на первый вход счетчика 42, поступает в нем на входы его первого 46 и второго 47 делителя частоты и, через элемент И 51, первый элемент ИЛИ 49 - на R-S-триггер 53, второй вход которого соединен с выходом первого делителя 46, а выход является выходом счетчика 42. Второй, третий, четвертый входы счетчика 42 являются соответственно первым, вторым и третьим входами его дешифратора 48, первый выход которого соединен с входом установки "0" первого делителя 46 и R-S - триггера 53, второй выход - с вторым входом элемента И и через второй элемент ИЛИ 50, второй вход которого через элемент НЕ 52 соединен с выходом первого делителя 46 с входом установки "0" делителя 47, вход которого соединен с третьим выходом дешифратора 48, а выход - с вторым входом первого элемента ИЛИ 49. Дешифратор 48 работает в соответствии с табл. 2.

При поступлении на входы дешифратора 48 первой комбинации сигналов (см. Табл. 2) работа счетчика 42 блокируется, поскольку на первом и втором выходах дешифратора 48 формируется логическая "1" и устанавливаются первый 46 и второй 47 делители, а также R-S-триггер 53 в нулевое состояние. Состояние третьего выхода дешифратора 48 может быть любым. При поступлении на входы дешифратора 48 второй комбинации сигналов разрешается работа первого делителя 46 и R-S= триггера 53 (лог. "0" на первом выходе дешифратора) и запрещается работа второго делителя 47 (лог. "1" на втором выходе дешифратора). Состояние третьего выхода дешифратора 48 может быть любым. В этом режиме через определенное количество тактов входного сигнала, определяемое коэффициентом деления первого делителя 46, на его выходе формируется перепад 0 ->> 1, по которому R-S-триггер 53 переключается в состояние "1". Через период входного сигнала, через элемент И 51 и первый элемент ИЛИ 49 перепадом 0 ->> 1 обеспечивается обратное переключение R-S-триггера 53. Таким образом, формируется импульс длительностью в такт группового цифрового потока.

При поступлении на вход дешифратора 48 третьей комбинации сигналов разрешается работа первого 46 и второго 47 делителя, запрещается прохождение входного сигнала через элемент И на вход первого элемента ИЛИ) на первом и втором выходах дешифратора - лог. "0"). Второму делителю 47 устанавливается коэффициент деления K (на третьем выходе дешифратора - лог. "0"). Как и в предыдущем случае по перепаду 0 ->> 1 от первого делителя R-S-триггер 53 переключается в состояние "1". После этого перепада начинает работать второй делитель 47 и обратное переключение R-S-триггера 53 осуществляется через K тактов входного сигнала по перепаду 0 ->> 1 с выхода второго делителя 47 через первый элемент ИЛИ 49. Таким образом, формируется импульс длительностью в K тактов группового потока. При поступлении на вход дешифратора 48 четвертой комбинации сигналов счетчик 42 работает как и в предыдущем случае. Однако, формируется импульс, длительностью в l тактов группового потока, что определяется логической "1" на третьем выходе дешифратора.

Таким образом, в предлагаемом устройстве повышается помехоустойчивость передачи за счет исключения из состава передающей и приемной частей генераторов псевдослучайных последовательностей и специальных цикловых синхропосылок, необходимых для разделения на приеме цифровых сигналов, относящихся к различным ТВ-каналам. При этом эффект скремблирования достигается за счет перемежения и инверсии по определенному правилу статистически независимых разрядных последовательностей, относящихся к различным ТВ-каналам. На соседних позициях в групповом цифровом потоке оказываются биты разрядов различных весов от разных АЦП. При этом учитывается то свойство цифрового сигнала изображения, что чем меньше вес разряда АЦП, тем менее коррелированная цифровая последовательность формируется на его выходе. Синхронизация процесса скремблирования на передаче и дескремблирования на приеме осуществляется за счет использования сигнала контроля четности, передаваемого в прямом и инверсном виде в составе группового цифрового потока. Одновременно этот сигнал, а также цифровой сигнал звукового сопровождения, представленный также в прямом и инверсном виде, используется для синхронизации приемной части системы при преобразования из последовательного кода в параллельный. При этом реализуется алгоритм ускоренного поиска синхронизма за счет размещения этих сигналов на определенных позициях группового цифрового сигнала, причем эти сигналы не нарушают сбалансированности группового цифрового сигнала, достигнутой за счет скремблирования, и обеспечивают расширение функциональных возможностей системы.

Технико-экономический эффект от использования предлагаемой системы по сравнению с базовым объектом связан с возможностью увеличения количества ТВ-каналов при цифровой передаче, например по волоконно-оптическим линейным трактам, группового цифрового потока без использования специальных кодов, необходимых для балансировки (стабилизации постоянной составляющей) цифрового сигнала и приводящих к увеличению скорости группового потока.

Система находится в стадии изготовления конструктивных макетов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ МНОГОФАЗНОГО ПЕРИОДИЧЕСКОГО СИГНАЛА | 1991 |

|

RU2017063C1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ КОРРЕКЦИИ КВАДРАТУРНЫХ ДЕМОДУЛЯТОРОВ | 2000 |

|

RU2187140C2 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ ПРЕДУПРЕЖДЕНИЯ О ВОЗНИКНОВЕНИИ СЕЙСМИЧЕСКИХ ТОЛЧКОВ И ЦУНАМИ | 2008 |

|

RU2363963C1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВИЖЕНИЯ ТРАНСПОРТНЫХ СРЕДСТВ | 1992 |

|

RU2054198C1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| ФОРМИРОВАТЕЛЬ ЭТАЛОННЫХ ОТВЕТОВ ДЛЯ ОБУЧАЮЩИХ УСТРОЙСТВ | 1993 |

|

RU2109024C1 |

| СПОСОБ КОНТРОЛЯ КОНТАКТИРОВАНИЯ КМОП-БИС И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2009518C1 |

| Быстродействующий селективный измеритель амплитуды ВЧ-сигнала | 1990 |

|

SU1780029A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОЙ ФОКУСИРОВКИ ИЗЛУЧЕНИЯ | 1991 |

|

RU2035772C1 |

Использование: в технике цифровых систем передачи сигналов телевидения в системах связи с импульсно-кодовой модуляцией. Сущность изобретения: система цифровой передачи и приема телевизионных сигналов на передающей стороне содержит первую и вторую шины, два аналогоцифровых преобразователя, задающий генератор, счетный триггер, n нечетных коммутаторов, n четных коммутаторов, n+2 элементов НЕ, сумматор по модулю два, преобразователь параллельного кода в последовательный код, шину входного цифрового сигнала, шину выхода линии связи, а на приемной стороне- шину выхода линии связи 16, преобразователь последовательного кода в параллельный 17, n элементов НЕ 18, n нечетных коммутаторов 19n, n четных коммутаторов 20n, два цифроаналоговых преобразователя 21,22, две шины выходных телевизионных сигналов 23,24,селектор тактовой частоты 25, три элемента И 26, 40, 41, делитель частоты 27, счетный триггер 28, четыре сумматора по модулю 29, 32, 33, 38, три счетчика 30, 31, 42, два интегратора 34, 35, два компаратора 36, 37, элемент ИЛИ 38, шину сигнала технической исправности канала 43 и шину выходного цифрового сигнала. Изобретение позволяет повысить помехоустойчивость и расширить функциональные возможности. 3 ил.

СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕВИЗИОННЫХ СИГНАЛОВ, содержащая на передающей стороне первый n-разрядный аналого-цифровой преобразователь (АЦП), вход которого является входом первого телевизионного сигнала, а выход первого разряда соединен через первый вход первого коммутатора с первым входом преобразователя параллельного кода в последовательный, выход которого является выходом передающей стороны, а на приемной стороне содержащая преобразователь последовательного кода в параллельный, сигнальный вход которого является входом приемной стороны, а выход соединен через первый вход первого коммутатора с первым входом первого цифро-аналогового преобразователя (ЦАП), выход которого является выходом первого телевизионного сигнала, первый элемент И, последовательно соединенные первый сумматор по модулю два, первый интегратор и первый компаратор, второй сумматор по модулю два и последовательно соединенные третий сумматор по модулю два, второй интегратор и второй компаратор, отличающаяся тем, что, с целью повышения помехоустойчивости и расширения функциональных возможностей, введены на передающей стороне второй n-разрядный АЦП, вход которого является входом второго телевизионного сигнала, (2n-1) коммутаторов, (n+2) элементов НЕ, задающий генератор, счетный триггер и сумматор по модулю два, первый выход первого АЦП соединен с вторым входом второго коммутатора, каждый выход первого АЦП, начиная с второго, соединен соответственно с первым входом соответствующего нечетного и вторым входом соответствующего четного коммутатора, а каждый выход второго АЦП, начиная с n-го в обратном порядке соединен с вторым входом соответствующего нечетного и первым входом соответствующего четного коммутатора, управляющие входы которых соединены с соответствующим входом сумматора по модулю два и выходом счетного триггера, вход которого соединен с тактовыми входами первого и второго АЦП и выходом задающего генератора, второй выход которого соединен с тактовым входом преобразователя параллельного кода в последовательный, n-первых сигнальных входов которого соединен с n-первыми сигнальными входами сумматора по модулю два и выходами соответствующих нечетных коммутаторов, выходы четных коммутаторов соединены с входами первых n-элементов НЕ, выходы которых соединены с вторыми сигнальными n-входами преобразователя параллельного кода в последовательный, первый и второй управляющие входы которого соединены соответственно с выходом сумматора по модулю два непосредственно и через (n+1)-й элемент НЕ, третий управляющий вход является входом цифрового сигнала и соединен с (n+2)-м элементом НЕ, выход которого соединен с четвертым управляющим входом преобразователя параллельного кода в последовательный код, а на приемной стороне введены второй n-разрядный ЦАП (2n-1) коммутатор, n-элементов НЕ, четвертый сумматор по модулю два, первый и второй входы которого соединены с выходами первого и второго компараторов, селектор тактовой частоты, вход которого соединен с первым входом преобразователя последовательного кода в параллельный код, первый, второй и третий счетчики, делитель частоты, вход которого соединен с первым входом первого счетчика и первым выходом селектора тактовой частоты, счетный триггер, выход которого соединен с первым управляющим входом второго сумматора по модулю два и управляющими входами каждого коммутатора, D-триггер, вход которого соединен с первым входом счетного триггера и выходом третьего счетчика, а выход является выходом сигнала технической исправности канала, второй и третий элементы И, выходы которых соединены соответственно с вторым и третьим входами первого счетчика, и элемент ИЛИ, первый и второй входы которого соединены с соответствующими входами четвертого сумматора по модулю два, а выход соединен с четвертым входом первого счетчика, выход которого соединен с первым входом первого счетчика, выход которого соединен с первым входом первого элемента И, второй вход которого соединен вторым выходом селектора тактовой частоты, второй вход преобразователя последовательного кода в параллельный код соединен с выходом первого элемента И, а третий вход соединен с вторым входом счетного триггера, входами второго и третьего счетчиков, тактовыми входами первого и второго n-разрядных ЦАП и выходом делителя частоты, первый выход преобразователя последовательного кода в параллельный код соединен с вторым входом второго коммутатора, первый вход которого соединен с вторым входом первого коммутатора и выходом первого элемента НЕ, каждый нечетный выход преобразователя последовательного кода в параллельный код, начиная с третьего до (2n-1)-го, соединен с первым входом соответствующего четного и вторым входом нечетного коммутатора, начиная с третьего, каждый четный выход преобразователя последовательного кода в параллельный код соединен с входом каждого элемента НЕ, при этом выход каждого элемента НЕ, начиная с второго, соединен с вторым входом соответствующего нечетного и первым входом соответствующего четного коммутатора, (2n+1)-й выход преобразователя последовательного кода в параллельный код соединен соответственно с первым входом первого сумматора по модулю два и вторым входом второго сумматора по модулю два, (2n+2)-й выход соединен с вторым входом первого сумматора по модулю два, (2n+3)-й выход соединен с первым входом третьего сумматора по модулю два и является выходом цифрового сигнала, (2n+4)-й выход соединен с вторым входом третьего сумматора по модулю два, первый и второй входы второго элемента И соединены соответственно с первым входом и выходом четвертого сумматора по модулю два, который также соединен с первым входом третьего элемента И, второй вход которого соединен с вторым входом четвертого сумматора по модулю два, выход каждого нечетного коммутатора, начиная с третьего, соединен с (n-1)-ми сигнальными входами первого n-разрядного ЦАП и n-первыми сигнальными входами второго сумматора по модулю два, n-вторых сигнальных входов которого соединен с n-входами второго n-разрядного ЦАП и выходами соответственно каждого четного коммутатора, начиная с (n-1), выход второго сумматора по модулю два соединен с вторым входом третьего счетчика, третий вход которого соединен с выходом второго счетчика, а выход второго n-разрядного ЦАП является выходом второго телевизионного сигнала.

Авторы

Даты

1994-06-15—Публикация

1991-04-30—Подача