ляционных узлов, а выход олока сравнения соединен с управляющим входом логического блока выработки управляющих импзльсов и с входом блокировки устройства вычисления полинома Ньютона при интерполяционных узлах, нричем первый выход устройства хранения разделенных разностей и ординат контролируемого процесса соединен с пятым входом устройства вычисления разделенных разностей нолинома Ньютона.

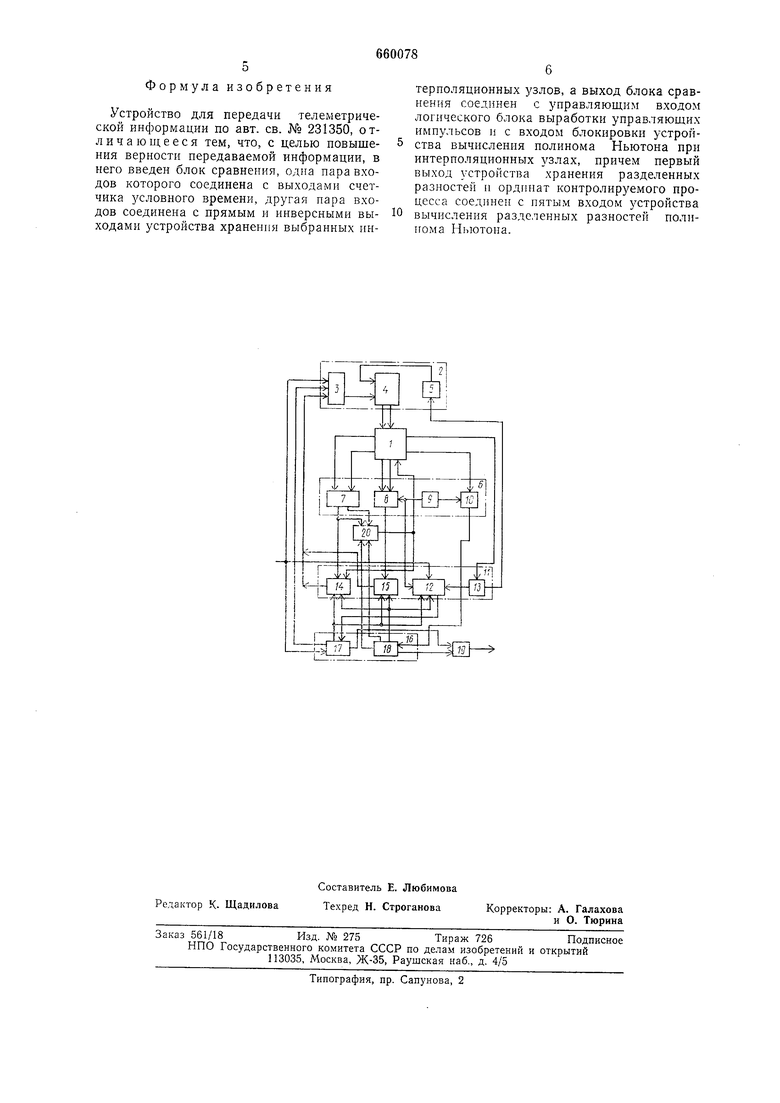

На чертеже представлена структурная электрическая схема предложенного устройства.

Устройство для нередачи телеметрической информации содержит логический блок 1 выработки управляющих импульсов, блок 2 определения ошибки, состоящий из схемы 3 разности, схемы 4 срав)1ения ошибки и схемы 5 вычисления и задания допустимой ощибки, блок 6 времени, состоящий из счетчика 7 условного време1 и, ключа 8, счетчика 9 текущего времени и схемы 10 выборки интерполяционных узлов кривой контролируемого процесса, блок 11 вычислений, состоящий из устройства 12 вычисления разделенных разностей полинома Ньютона, устройства 13 вычисления степени нолинома, устройств 14 и 15 вычисления полипома Ньютона при интерполяционных узлах, блок 16 хранения результатов, состоящий из устройства 17 хранения разделенных разностей и ординат контролируемого процесса и устройства 18 хранения выбранных интерполяционных узлов, ключ 19 выдачи данных и блок 20 сравнения.

Устройство работает следующим образом.

Поступающие на вход отсчеты телеметрируемого процесса f(ti) и значения полинома fh(i} при экстраполяции или f(ts) и Jk(ts) при интерполяции поступают на входы схемы 3, в которой вычисляется модуль разности Т).

Нри этом значения f(4) поступают из устройства 17, значения fh(fs)-из устройства 14, значения fh(ti) -из устройства 15. Значение т с выхода схемы 3 поступает на вход счемы 4, на другой вход которой подается допустимая ощибка &(h), вычисленная в схеме 5.

Если ошибка аппроксимации превышает допустимую ощибку, т. е. , схема 4 вырабатывает сигнал на первом выходе, в противном случае сигнал вырабатывается на втором выходе.

Оба сигнала поступают на логический блок 1.

Если сигнал на первом выходе схемы 4 выработался при выполнении процедуры интерполяции, то логический блок 1 выдает управляющие сигналы на схему 10. Ключ 8 открывается, через него числовые отметки времени ti с выхода счетчика 9 поступают в устройство 15. При этом счетчик 7 сбрасывается и подача числовых отметок времени ts на устройство 14 прекращается. Начинает работать устройстве 15, которое вычисляет значения полинома. Если экстраполяция отсчетов правильна, то в результате сравнения fh(-i) с текущими отсчетами /(/,-) схема 4 вырабатывает сигнаьЧ на втором выходе, что соответствует выполнению условия г) (/;) (/г).

В случае, если схема 4 вырабатывает сигнал па нервом выходе, что соответствует выполнению условия i (/,) к{/г). логический блок 1 выдает сигнал, по которому устройство 13 увеличивает степень полинома К на единицу, сигнал на ключ 8, по которому последний запирается и экстраполяция прекращается, и сигнал на счетный вход счетчика 7, по которому последний запускается.

Из устройства 13 поступает команда, по которой схема 4 вычисляет допустимую ошибку е(+1) при этом в устройство 12 из устройств 17 и 18 вызываются ранее вычисленные разделенные разности и существенные узлы, а со счетчика 9 - узел it. Вновь вычисленная разделенная разность поступает в устройство 17 на хранение.

Нз устройства 17 и 18 выбираются разделенные разности п существенные узлы и

подаются в устройство 14 для интерполяции накопленных отсчетов.

Если при проверке по всем значениям /,, от 0 до /, () схема 4 вырабатывает сигнал на втором выходе, то аппроксимация процесса f(() полиномом K- -l-fi степени оказалась удачной.

В устройстве 12 пересчитывается разделенная разность и вновь вычисленное значение разделенной разности поступает в

устройство 14, где производятся вычисления. Данная процедура выполняется по каждому вновь поступающему отсчету до тех пор, пока схема 4 вырабатывает сигнал на втором выходе, т. е. пока выполняется условие т (ts) е (/e-f-1).

В процессе выполнения нроцедуры интерполяции числовые отметки времени ts поступают с прямого и инверсного выходов

счетчика 7 на одну пару входов блока 20 сравнения, на другую пару входов которого поступают существенные узлы t с прямого и инверсного выходов устройства 17. При выполнении условия /., /,:з па выходе

блока 20 сравнения вырабатывается сигпал, который поступает на управляющий вход логического блока 1 и па вход блокировки вычислений устройства 14. По этому сигналу логический блок 1 увеличивает содержимое счетчика 7 на единицу, а в устройстве 14 блокируется вычисление полинома. Блок 20 сравнения исключает операции, связанные с вычислением полинома iустройстве 14, разности в схеме 3 и операции сравнения в схеме 4 при ts tij.

Формула изобретения

Устройство для передачи телеметрической информации по авт. св. № 231350, отличающееся тем, что, с целью повышения верности передаваемой информации, в него введен блок сравнения, одна пара входов которого соединена с выходами счетчика зсловного времени, другая пара входов соединена с прямым и инверсными выходами устройства хранения выбранных интерполяционных узлов, а выход блока сравнения соединен с управляющим входом логического блока выработки управляющих импульсов и с входом блокировки устройства вычисления полинома Ньютона при интерполяционных , причем первый выход устройства хранения разделенных разностей и ординат контролируемого процесса соединен с пятым входом устройства вычисления разделенных разностей полинома Ньютона.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ТЕЛЕМЕТРИЧЕСКОЙ ИНФОРМАЦИИ | 1968 |

|

SU231350A1 |

| Адаптивное устройство для сокращения избыточности цифровой информации | 1983 |

|

SU1136201A1 |

| Экстраполятор | 1986 |

|

SU1413651A1 |

| Устройство для передачи информации со сжатием данных | 1976 |

|

SU748484A1 |

| Экстраполятор для прогнозатора постепенных отказов | 1980 |

|

SU883916A1 |

| ПОЛИНОМИАЛЬНЫЙ МОДУЛЯРНЫЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ БУЛЕВЫХ ФУНКЦИЙ С ОБНАРУЖЕНИЕМ ОШИБОК | 2015 |

|

RU2586574C1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство для решения линейных дифференциальных уравнений | 1987 |

|

SU1476486A1 |

| Логический вычислитель в системе остаточных классов | 2016 |

|

RU2637488C1 |

| СПОСОБ И УСТРОЙСТВО ФОРМИРОВАНИЯ СИГНАЛОВ ИЗОБРАЖЕНИЯ В СИСТЕМАХ ЦИФРОВОГО ТЕЛЕВИДЕНИЯ СТАНДАРТНОЙ И ВЫСОКОЙ ЧЕТКОСТИ | 2013 |

|

RU2557261C2 |

Авторы

Даты

1979-04-30—Публикация

1977-09-12—Подача