рового преобразования, а выходом к цифровому выходу блока аналого-цифрового преобразования и к цифровому входу цифроаналогового преобразования, соединенного аналоговым входом с аналоговым входом блока аналогоцифрового преобразования, первым выходом - с входом суммирующего усилителя, а вторым выходом - с выходом суммирующего усилителя, аналоговым выходом сигнала рассогласования блока аналого-цифрового преобразования, входом нуль-органа и с первым входом компаратора, подключенного вторым входом к шине порогового напряжения, а выходом - к первому входу первого элемента И-НЕ и к первому входу третьего элемента ИЛИ, соединенного вторым входом с выходом нульоргана и с первым входом второго

5068

элемента И-НЕ, а выходом - с первым входом генератора тактовых импульсов, подключенного вторым входом к входу управления формирователя тактовых импульсов блока аналого-цифрового преобразования, а выходом - к выходу управления формирователя тактовых импульсов блока аналого-цифрового преобразования и к вторым входам первого и второго элементов И-НЕ, третьи входы которых соединены с входом блокировки преобразования блока аналого-цифрового преобразования, а выходы - с первыми входами первого , и второго элементов ИЛИ -соответственно, вторые входы которых подключены к входам прибавления и вычитания единицы младшего разряда блока анаЛОГО-1Ц1ФРОВОГО преобразования соот. ветственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 2006 |

|

RU2308148C1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Многоканальный аналого-цифровой преобразователь | 1982 |

|

SU1040599A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1990 |

|

SU1781625A1 |

| Функциональный преобразователь | 1979 |

|

SU840956A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Гибридный функциональный преобразователь | 1982 |

|

SU1076918A1 |

1. ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ МНОГИХ ПЕРЕМЕННЫХ, содержащий блок синхронизации и группу блоков аналого-цифрового преобразования, подключенных аналоговыми входами к шинам ввода соответствующих переменных, а аналоговыми выходами сигнала рассогл 1сованид - к входам блока формирования интерполирующих функций, выходы которого соединены с аналоговыми входами соответствующих умножающих цифроаналоговых преобразователей группы, подключенных выходами к входу выходного суммирующего усилителя, и запоминающее устройство, отлич ающий с я тем, что, с целью его упрощения путем уменьшения объема памяти и исключения блоков адресации, цифровые выходы блоков аналого-цифрового преобразования группы соединены с адресными входами запоминающего устройства, подключенного выходами к информационным входам введенных регистров труппы, соединенных выходами с цифровыми входами соответствующих цифроаналоговых преобразователей группы, а управляющими входами - с первой группой выходов блока синхронизации, подключенного второй группой выходов к входам прибавления единицы младшего разряда блоков аналого-цифрового преобразования группы, соединенных входами вычитания единицы младшего разряда с третьей группой выходов блока синхронизации, подключенного первым выходом к входам управления формированием тактовьк и myльcoв блоков аналого-цифрового преобразования группы, входы блокировки преобразования которых соединены с вторым выходом блока синхронизации, а входы управления установкой адресных кодов - с третьим (О выходом блока синхронизации, подключенного четвертым и пятым выходами к первому и второму входам управления записью и считыванием запоминающего устройства, первым входом к шине выбора режима запись - считывание, ВТОРЫМ входом - к .шине исполнения режима, а ГРУППОЙ входов - к выходам тактовых импульсов блоков ел аналого-цифрового преобразования о группы. Од 2.. Преобразователь по п. 1, отСХ) личающийся тем, что каждый блок аналого-цифрового преобразования содержит цифроаналоговый преобразователь, суммирующий усилитель, компаратор, нуль-орган, элементы И-НЕ иИЛИ, генератор тактовых импульсов и реверсивный счетчик, подключенный суммирующим и вычитающим входами к выходам первого и второго элементов ИЛИ соответственно, управляющим входом - к входу з равления установкой адресных кодов блока аналого-циф

t

Изобретение относится к автомати.ке и вычислительной технике и может быть использовано, в частности, в аналоговых и аналого-цифровых вычислительных машияах и системах при Моделировании динамических процессов

Известен функциональньй преобразователь многих переменных, содержащий блок анализа амплитуд, сумматоры, блок формирования значений функций в опорных точках и коэффициентрв масштаба, масштабные преобразователи и выходной сумматор С11.

Известен также функциональный преобразователь многих переменных, содержаш;ий блок синхронизации, запоминающее устройство, блоки аналого-цифрового преобразования, формирователи интерполирующих функций, интерполяторы и суммирующие усилители С21.

Недостатком этих функциональных преобразователей является сложность технической реализации, обусловленная необходимостью хранения как узловых значений функций, так и значений приращений на интервалах

Наиболее близким к изобретению является функциональный преобразователь многих переменных, содержащий блок синхронизации и группу блоков

аналого-цифрового преобразования, подключенных аналоговыми входами к шинам ввода соответствующих переменных, цифровыми выходами через блоки адресации - к адресным входам запоминающего устройства, а аналоговыми выходами сигнала рассогласования к входам блока формирования интерполирующих функций, выходы которого соединены с аналоговыми входами соответствуюш№с умножающих цифроаналоговых преобразователей группы, подключенных выходами к входу выходного суммирующего усилителя, а цифровыми входами - к соответствующим выходам запоминакяцего устройства. Блок формирования интерполирующих функций для случая двух переменных содержит формирователи, умножитель и сумматоры. Запоминающее устройство обеспечивает хранение узловых значений ординат воспроизводимой функции и содержит 2 секций, где m - количество независимых переменных. Определение секции, в которую надо записать то или иное узловое значение функции осуществляется по признакам четности номера этого узла при его проекции на оси аргументов 133.

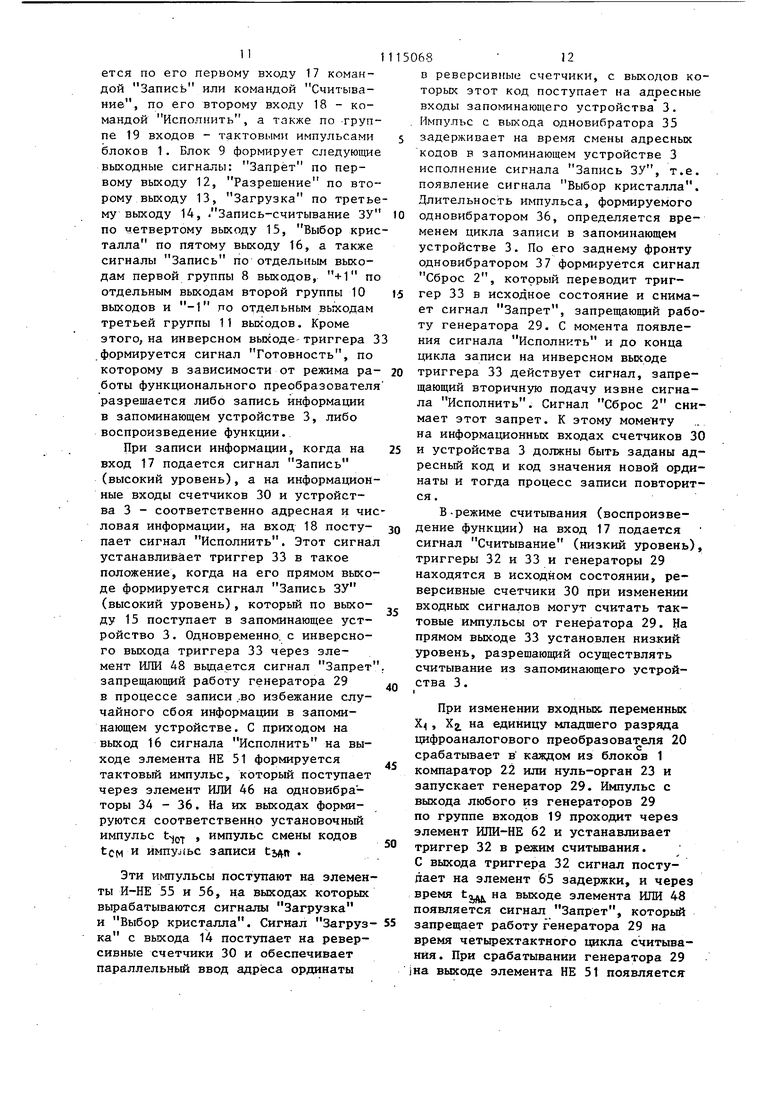

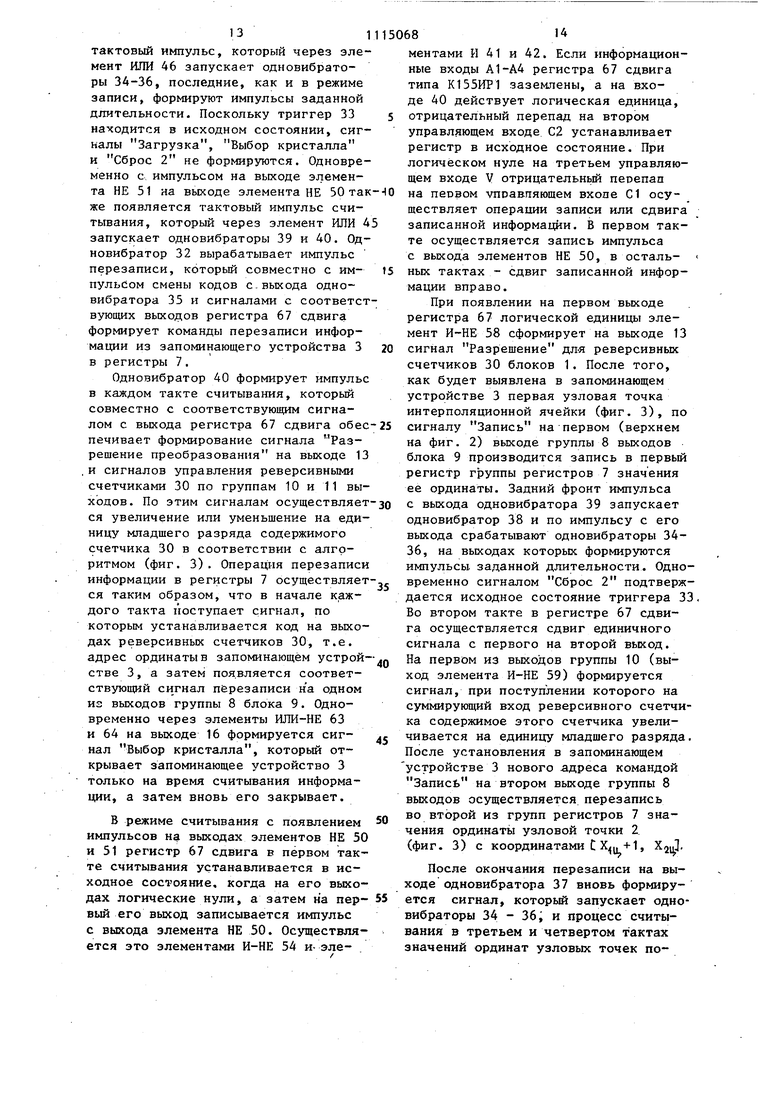

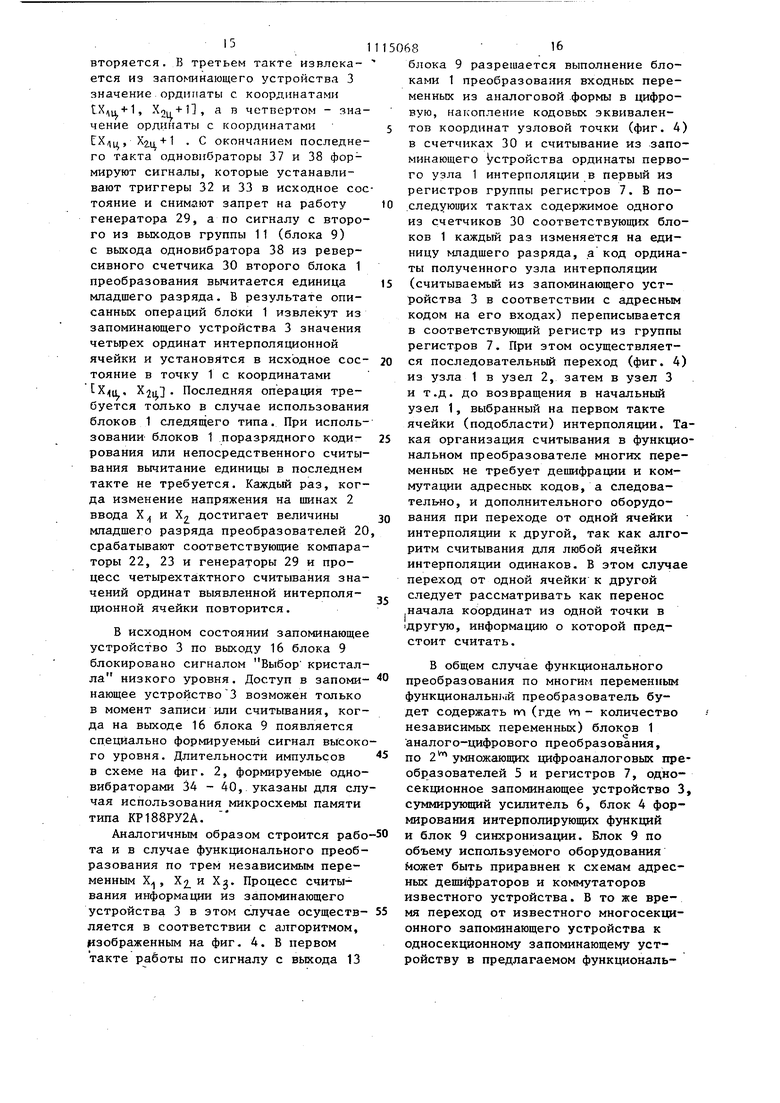

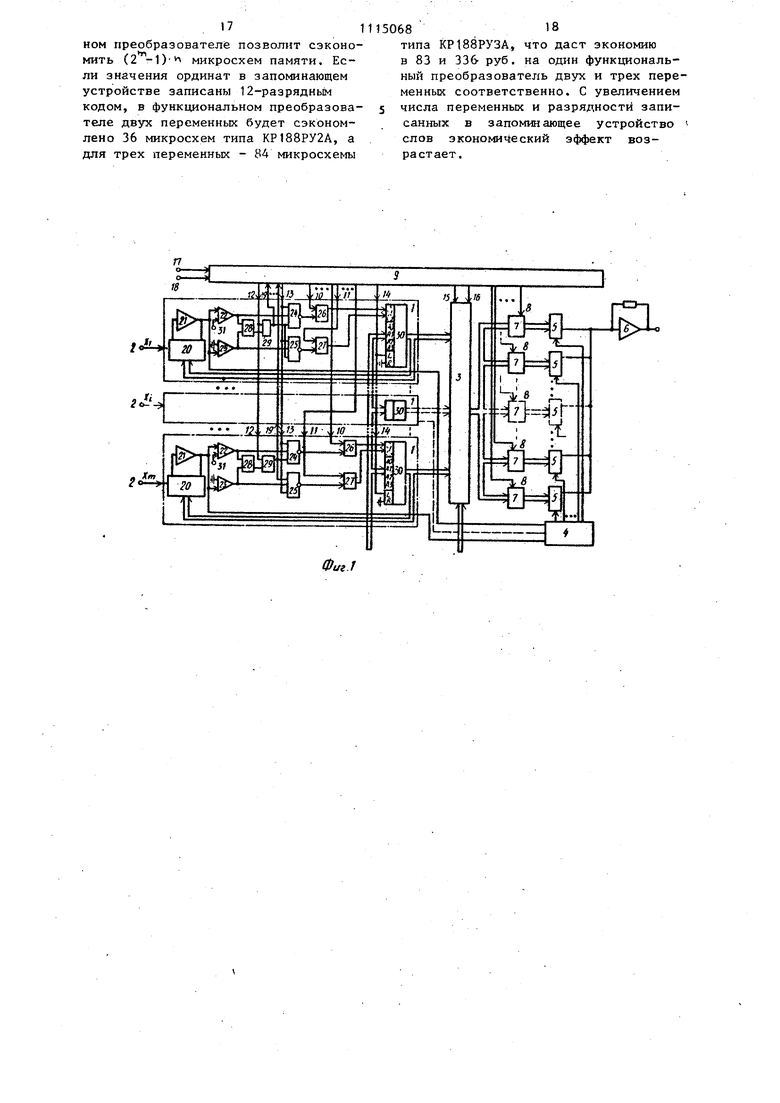

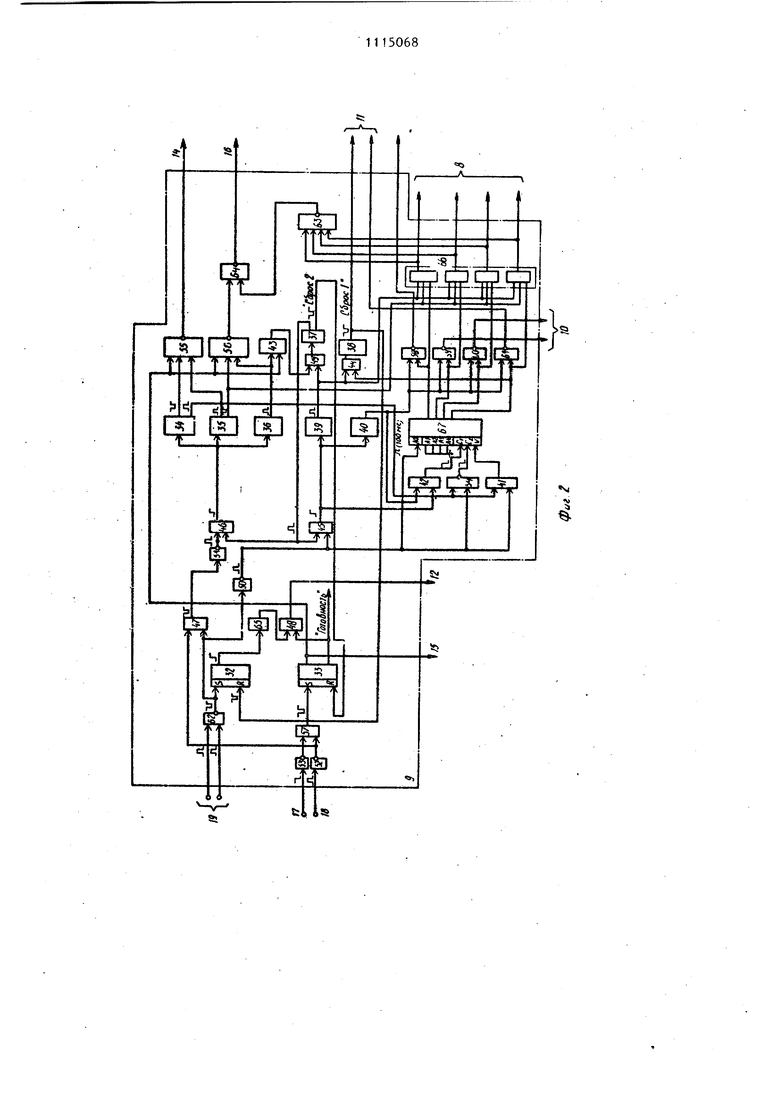

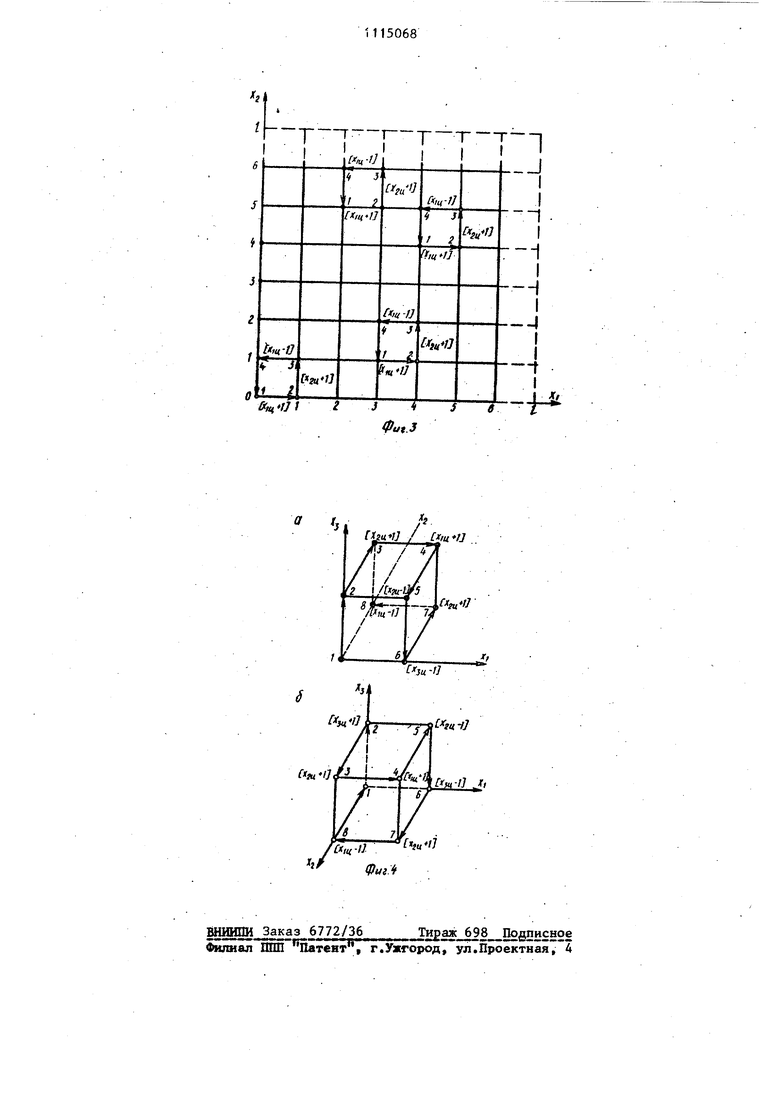

Недостатком известного устройства является техническая сложность реали3зации, обусловленная использованием запоминающего устройства с большим объемом памяти, содержащей 2 секций с общим количеством элементов памяти п 2, где п - количество разрядов умножающих цифроаналоговых преобразователей. Целью изобретения является упрощение функционального преобразователя путем уменьшения объема памяти и исключения блоков адресации. Поставленная цель достигается тем, что в функциональном преобразователе многих переменных, содержащем блок синхронизации и группу блоков аналого-цифрового преобразования, подключенных аналоговыми входами к шинам ввода соответствующих переменных, а аналоговыми выходами сигнала рассогласрвания - к входам блока фор мирования интерполирующих функций, выходы которого соединены с аналоговыми входами соответствующих умножаю щих цифроаналоговых преобразователей группы, подключенных выходами к входу выходного суммирующего усилителя и запоминающее устройство, цифровые выходы блоков аналого-цифрового преобразования группы соединены с адресньми входами запоминающего устройства, подключенного выходами к ин формационным входам введенных регист ров группы, соединенных выходами с цифровыми входами соответствующих цифроаналоговых преобразователей группы, а управляющими входами - с первой группой выходов блока синхронизации, подключенного второй группой выходов к входам прибавления единицы младшего разряда блоков аналого-цифрового преобразования группы, соединенных входами вычитания единицы младшего разряда, с третьей группой вьпсодов блока синхронизации подключенного первьш выходом к входам управления формировавшем тактовых импульсов блоков аналого-цифрово го преобразования группы, входы блокировки преобразования которых соеди нены с вторым выходом блока синхронизации, а входы управления установкой адресных кодов - с третьим выходом блока синхронизации, подключенного четвертым и пятым выходами к первому и второму входам управления записью и считыванием запоминающего устройства, первым входом - к шине выбора режима запись - считы68вание, вторым входом - к шине исполнения режима, а группой входов - к выходам тактовых импульсов блоков аналого-цифрового преобразования группы. При этом каждый блок аналого-цифрового преобразования содержит цифроаналоговьй преобразователь, суммирующий усилитель, компаратор, нуль-орган, элементы И-НЕ и ИЛИ, генератор тактовых импульсов и реверсивный счетчик, подключенньй суммирующим и вычитающим входами к выходам первого и второго элементов ИЛИ соответственно, управляющим входом - к входу управления установкой адресных кодов блока аналого-цифрового преобразования, а выходом - к цифровому выходу блока аналого-цифрового преобразования и к цифровому входу цифроаналогового преобразования, соединенного аналоговым входом с аналоговым входом блока аналогоцифрового преобразования, первым выходом - с входом суммирующего усилителя, а вторым выходом - с выходом суммирующего усилителя, аналоговым выходом сигнала рассогласования блока аналого-цифрового преобразования, входом нуль-органа и с первым входом компаратора, подключенного вторым, входом к шине порогового напряжения, а выходом - к первому входу первого элемента И-НЕ и к первому входу третьего элемента ИЛИ, соединенного вторым входом с выходом нуль-органа и с первым входом второго элемента И-НЕ, а выходом - с первым входом генератора тактовых импульсов, подключенного вторым входом к входу управления формирователя тактовых импульсов блока аналого-цифрового преобразования, а выходом - к выходу управления формирователя тактовых импульсов блока аналого-цифрового преобразования и к вторым входам первого и второго элементов И-НЕ, третьи входы которых соединены с входом блокировки преобразования блока аналого-цифрового преобразования, а выходы - с первыми входами первого и второго элементов ИЛИ соответственно, вторые входы которых подключены к входам прибавления и вычитания единицы младшего разряда блока аналого-цифрового преобразо ния соответственно. На фиг. 1 представлена блок-схема функхщонального преобразователя многих переменных; на фиг. 2 - функциональная схема одного из возможных вариантов блока синхронизации (для случая воспроизведения функций двух переменных) ; на фиг. 3 - графики, характеризующие алгоритм считывания узловых значений выявленной интерполяционной ячейки для двух переменных; на фиг. 4 - то же, для трех переменных.

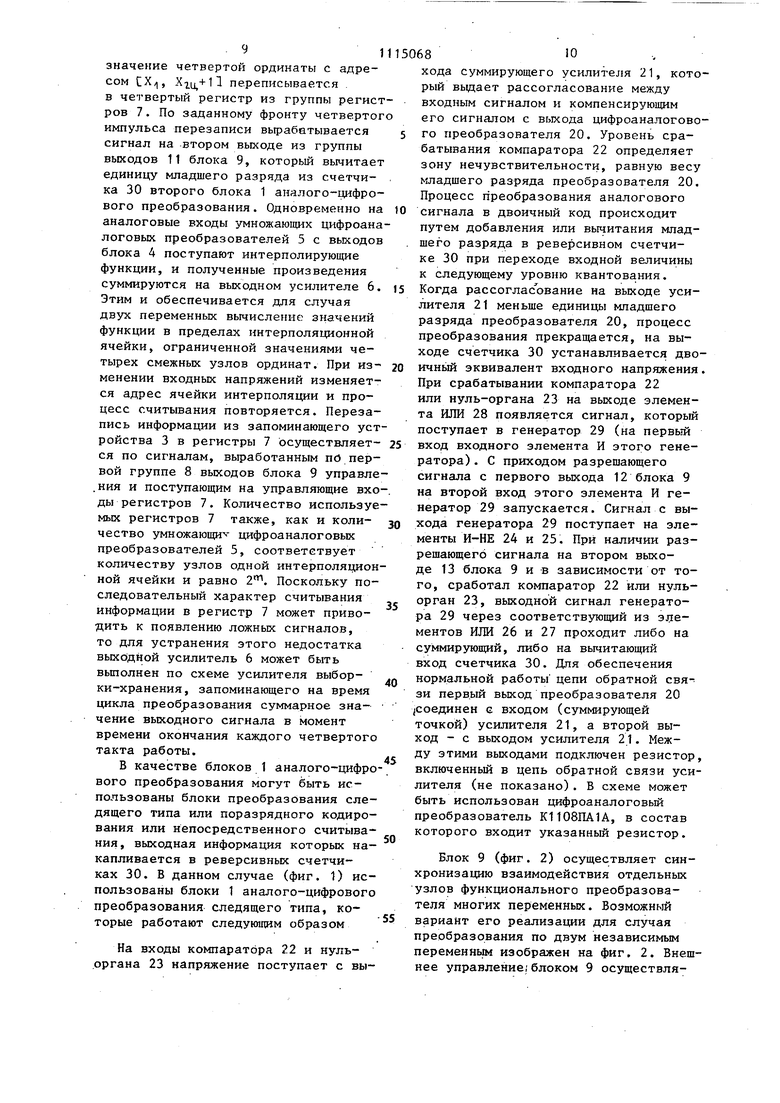

Функциональный преобразователь многих переменных (фиг. 1) содержит группу блоков 1 аналого-цифрового преобразования, подключенных аналоговыми входами к шинам 2 ввода соответствующих переменных, цифровыми выходами - к адресным входам запоминающего устройства 3, а аналоговыми выходами сигнала рассогласования - к входам блока 4 формирования интерполирующих функций. Выходы блока 4 соединены с аналоговыми входами соответствующих умножающих цифроаналоговых преобразователей 5 группы, подключенных выходами к входу выходного суммирующего усилителя 6, а цифровыми входами - к выходам соот- ветствующих регистров 7 группы. Регистры 7 соединены информационными входами с выходом запоминающего устройства 3, а управляющими ыходами с первой группой 8 выходов блока 9 синхронизации. Блок 9 подключен второй группой 10 выходов к входам прибавления единицы мпадшего разряда блоков 1 анёлого-цифрового преобразования, соединенных входами вычитания единицы младшего разряда с третьей группой 11 выходов блока 9. Блок подключен первым выходом 12 к входам управления формированием тактовых импульсов блоков 1, входы блокировки преобразования которых соединены с вторым выходом 13 блока 9, а входы управления установкой адресных кодов - с третьим выходом 14 блока 9. Блок 9 подключен четвертым и пятым выходами 15 и 16 к первому и второму входам управления записью и считыванием запоминающего устройства 3, первым входом 17 - к шине выбора режима запись - считывание, вторым входом 18 - к шине исполнения режима а группой входов 19 - к выходам тактовых импульсов блоков 1 аналогоцифрового преобразования.

I

Каждый блок 1 аналого-цифрового преобразования может быть вьтолнен.

например, содержащим (фиг. 1) цифроаналоговый преобразователь 20, суммирующий усилитель 21, компаратор 22, ртуль-орган 23, элементы И-НЕ 24 и 25, элементы ИЛИ 26-28, генератор 29 тактовых импульсов и реверсивный счетчик 30. Счетчик 30 подключен суммиРУЮ1Щ1М и вычитающим входами к выходам первого и второго элементов ИЛИ 26 и 27 соответственно, управляющим входом - к входу управления установкой адресных кодов блока 1, а выходом к цифровому выходу блока 1 и к цифровому входу цифроаналогового преобразования. Преобразователь 20 соединен аналоговым входом с аналоговым входом блока 1, первым выходом - с входом суммирующего усилителя 21, а вторым выходом - с- выходом суммирующего уси(Лителя 21, аналоговым выходом сигнала рассогласования блока 1, входом нуль-органа 23 и с первым входом .компаратора 22. Компаратор 22 подключен вторым входом к шине 31 порогового напряжения, а выходом - к первому входу первого элемента И-НЕ 24 и к первому входу третьего элемента ИЛИ 28. Элемент ИЛИ 28 соединен вторым входом с выходом нуль-органа 23 и с первым входом второго элемента И-НЕ 25, а выходом - с первым входом генератора 29 тактовых импульсов. Генератор 29 подключен вторым входом к входу управления формированием тактовых импульсов блока 1, а выходом - к выходу тактовых импульсов блока 1 и к вторым входам элементов И-НЕ 24 и 25, третьи входы которых соединены с входом блокировки преобразования блока 1. Выходы элементов И-НЕ 24 и 25 соединены с первыми входами элементов ИЛИ 26 и 27 соответственно, вторые входы которых подключены к входам прибавления и вычитания единицы младшего разряда блока 1 соответственно.

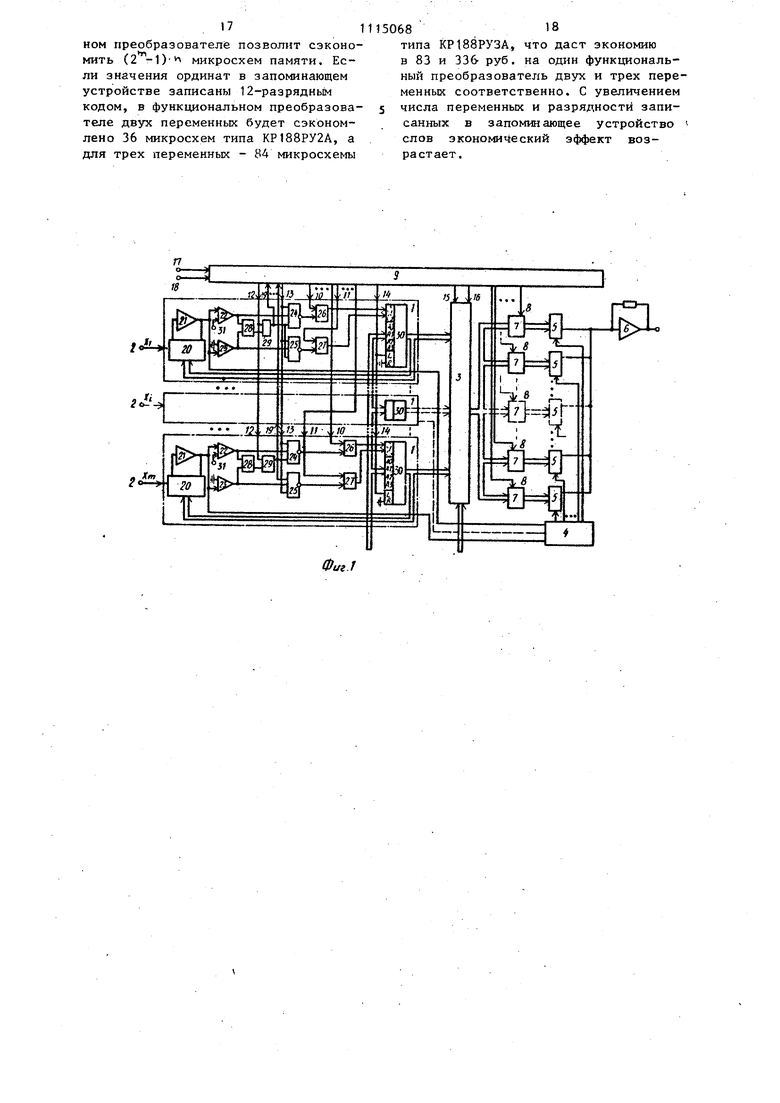

Блок 9 синхронизации может быть выполнен, например, содержащим (фиг. 2) для случая двух переменных триггеры 32 и 33, одновибраторы 34 40, элементы И 41-44, элементы ИЛИ 45-49, элементы НЕ 50-53, элементы И-НЕ 54-61,.элементы ИЛИ-НЕ 62-64, элемент 65 задержки, группу 66 эле5 ментов И и регистр 67 сдвига.

Рассмотрим работу на примере функционального преобразования по двум независимым переменным. Каждая из независимых переменных Х и Х, (фиг. 3) при равномерном расположении узлов разбивается на участков интерполяции. В результате образуется 2 интерполяционных ячеек и ( узлов интерполяции, которыми определяется информационная емкость элемен тов памяти. При записи информации в запоминающее устройство 3 на первый вход 17 блока 9 синхронизации подается команда Запись, на информа ционные шины устройства 3 - код, соответствующий значению ординаты выбранного узла. Координаты узла задаются по информационным шинам (соединенным с установочными входами счетчиков 30) двоичным кодом, составленным из m к.-разрядных кодов адреса ординаты, поступающих на установочные входы разрядов счетчиков 30 блоков 1 аналого-цифрового преобразования. Запись информации в выбранные узлы осуществляется по команде Исполнить которая подается на второй вход 18 блока 9. При этом блоком 9 вырабатывается по третьему выходу 14 команда Загрузка, по пятому выходу 15 - команда Запись ЗУ и производится параллельный ввод кодов В счетчик 30. С выходов счетчиков коды поступают на адресные входы . запоминающего устройства 3, куда одновременно по выходу 16 блока 9 поступает команда Выбор кристалла, разрешающая запись информации в запоминающее устройство 3. Затем произ водится смена адреса узда информации задается значение его ординаты, внов подается команда Исполнить и произ водится запись новой ординаты и т.д. до тех пор, пока не будут записаны все узловые значения ординат. При записи блок 9 синхронизации по своему первому выходу вырабатывает команду, которая запрещает запись ложной информации, поступающей по вычитающему и суммирующему входам счётчиков 30 блоков 1 аналого-цифрового преобразования. Аналогичная команда выоабатывается и на время считывания ьшулиаимвас vn j. . из запоминающего устройства 3 узловых значений выявленной интерполяционной ячейки. Считывание 1О1фровой информации из запоминающего устройства 3 осуществляется при подаче входных напря жений на шине 2 ввода соответствующи переменных и команды Считывание на 1 683 первый вход 17 блока 9. Выборка узлов, принадлежащих той области информации, в которой находятся несущие координаты независимых переменных, производится в 2 тактов (фиг. 3 и 4) при подаче на адресные входы запоминающего устройства 3 адреса этой области. Таким образом, при считывании является код, составленный из кодов основных частей каждой из м входных переменных функционального преобразователя и образующийся на выходах реверсивных счетчиков 30 блоков 1 аналого-цифрового преобразования. Этот код всегда однозначно выявляет ячейку интерполяции и ее первый узел интерполяции (фиг. 3). В первом такте сигнал по второму выходу 13 блока 9 разрешает блокам 1 выполнение аналого-цифрового преобразования переменных, т.е. разрешает реверсивным счетчикам 30 вьшолнение счета. После того, как на выходах счетчиков установятся кодовые эквиваленты независимых входных переменных и в запоминающем устройстве 3 будет выявлен адрес первого узла (фиг. 3), которому соответствует адресный код CX/iij, Xiu,l j значение ординаты выявленного узла переписывается в первый регистр из группы регистров 7. Во втором такте по первому выходу из группы 10 выходов блока 9 вырабатывается сигнал, который увеличивает содержимое счетчика 30 первого из блоков 1 на единицу младшего разряда-. и из запоминающего устройства 3 извлекается и записывается во второй регистр из группы регистров 7 значение ординаты второго интерполяционного узла с адресным кодом СХ/|м + 2. В третьем такте по второму выходу из группы 10 выходов блока 9 вырабатывается сигнал, увеличивающий на единицу содержимое счетчика 30 второго из блоков 1 аналого-цифрового преобразования, и значение орди, наты ретьего интерполяционного узла. которому соответствует адресный код tx,(li+1, , переписывается в третий регистр из группы регистров 7. В четвертом такте из счетчика 30 первого блока 1 аналого-цифрового преобразования по сигналу с первого выхода из группы Т1 выходов блока 9 вычитается единица младшего разряда и значение четвертой ординаты с адресом СХ/,, переписывается в четвертый регистр из группы регист ров 7. По заданному фронту четвертог импульса перезаписи вырабатывается сигнал на втором выходе из группы выходов 11 блока 9, который вычитает единицу младшего разряда из счетчика 30 второго блока 1 аналого-цифрового преобразования. Одновременно на аналоговые входы умножающих цифроана логовых преобразователей 5 с выходов блока 4 поступают интерполирующие функции, и полученные произведения суммируются на выходном усилителе 6. Этим и обеспечивается для случая двух переменных вычисление значений функции в пределах интерполяционной ячейки, ограниченной значениями четырех смежных узлов ординат. При изменении входных напряжений изменяется адрес ячейки интерполяции и процесс считывания повторяется. Перезапись информации из запоминающего уст ройства 3 в регистры 7 осуществляется по сигналам, выработанным по первой группе 8 выходов блока 9 управле .ния и поступающим на управляющие вхо ды регистров 7. Количество используе мых регистров 7 также, как и количество умножающие цифроаналоговых преобразователей 5, соответствует количеству узлов одной интерполяцион ной ячейки и равно 2. Поскольку последовательный характер считывания информации в регистр 7 может приводить к появлению ложных сигналов, то для устранения этого недостатка выкидной усилитель 6 может быть выполнен по схеме усилителя выборки-хранения, запоминающего на время цикла преобразования суммарное значение выходного сигнала в момент времени окончания каждого четвертого такта работы. В качестве блоков 1 аналого-цифро вого преобразования могут быть использованы блоки преобразования следящего типа или поразрядного кодирования или непосредственного считывания, выходная информация которых накапливается в реверсивных счетчиках 30. В данном случае (фиг. 1) использованы блоки 1 аналого-цифрового преобразования следящего типа, которые работают следующим образом На входы компаратора 22 и нульоргана 23 напряжение поступает с выхода суммирующего усилителя 21, который вьщает рассогласование между входным сигналом и компенсирующим его сигналом с выхода цифроаналогового преобразователя 20. Уровень срабатывания компаратора 22 определяет зону нечувствительности, равную весу младшего разряда преобразователя 20. Процесс преобразования аналогового сигнала в двоичный код происходит путем добавления или вычитания младшего разряда в реверсивном счетчике 30 при переходе входной величины к следующему уровню квантования. Когда рассогласование на выходе усилителя 21 меньше единицы младшего разряда преобразователя 20, процесс преобразования прекращается, на выходе счетчика 30 устанавливается двоичньй эквивалент входного напряжения. При срабатывании компаратора 22 или нуль-органа 23 на выходе элемента ИЛИ 28 появляется сигнал, который поступает в генератор 29 (на первьзй вход входного элемента И этого генератора) . С приходом разрешающего сигнала с первого выхода 12 блока 9 на второй вход этого элемента И генератор 29 запускается. Сигнал с выхода генератора 29 поступает на элементы И-НЕ 24 и 25. При наличии разрешающегб сигнала на втором выходе 13 блока 9 и в зависимости от того, сработал компаратор 22 или нульорган 23, выходной сигнал генератора 29 через соответствующий из элементов ИЛИ 26 и 27 проходит либо на суммирующий, либо на вычитающий вход счетчика 30. Для обеспечения нормальной работы цепи обратной связи первый вькод преобразователя 20 (Соединен с входом (суммирующей точкой) усилителя 21, а второй выход - с выходом усилителя 21. Между этими выходами подключен резистор, включенный в цепь обратной связи усилителя (не показано). В схеме может быть использован цифроаналоговый преобразователь К1108ПА1А, в состав которого входит указанный резистор. Блок 9 (фиг. 2) осуществляет синхронизацию взаимодействия отдельных узлов функционального преобразователя многих переменных. Возможный вариант его реализации для случая преобразования по двум независимым переменньм изображен на фиг, 2. Внешнее управление;блоком 9 осуществляется по его первому входу 17 командой Запись или командой Считывание, по его второму входу 18 - командой Исполнить, а также по -группе 19 входов - тактовыми импульсами блоков 1. Блок 9 формирует следующие выходные сигналы: Запрёт по первому выходу 12, Разрешение по второму выходу 13, Загрузка по третьему выходу 14, .Запись-считывание ЗУ по четвертому выходу 15, Выбор кристалла по пятому выходу 16, а также сигналы Запись по отдельным выходам первой группы 8 выходов, +1 по отдельным выходам второй группы 10 выходов и -1 по отдельным выходам третьей группы 11 выходов. Кроме этого, на инверсном выходе-триггера 3 формируется сигнал Готовность, по которому в зависимости от режима работы функционального преобразователя разрешается либо запись информации в запоминающем устройстве 3, либо воспроизведение функции.

При записи информации, когда на вход 17 подается сигнал Запись (высокий уровень), а на информационные входы счетчиков 30 и устройства 3 - соответственно адресная и числовая информации, на вход 18 поступает сигнал Исполнить. Этот сигнал устанавливает триггер 33 в такое положение, когда на его прямом выходе формируется сигнал Запись ЗУ (высокий уровень), который по выходу 15 поступает в запоминающее устройство 3. Одновременно, с инверсного выхода триггера 33 через элемент ИЛИ 48 вьщается сигнал Запрет запрещающий работу генератора 29 в процессе записи ,.во избежание случайного сбоя информации в запоминающем устройстве. С приходом на выход 16 сигнала Исполнить на выходе элемента НЕ 51 формируется тактовый импульс, который поступает через элемент ИЛИ 46 на одновибраторы 34 - 36. На их выходах формируются соответственно установочный импульс t-jjjf , импульс смены кодов tcM и импуо(ьс записи tsfrit .

Эти импульсы поступают на элементы И-НЕ 55 и 56, на выходах которых вырабатываются сигналы Загрузка и Выбор кристалла. Сигнал Загрузка с выхода 14 поступает на реверсивные счетчики 30 и обеспечивает параллельный ввод адреса ординаты

в реверсивные счетчики, с выходов которых этот код поступает на адресные входы запоминающего устройства 3. Импульс с выхода одновибратора 35 задерживает на время смены адресных кодов в запоминающем устройстве 3 исполнение сигнала Запись ЗУ, т.е. появление сигнала Выбор кристалла. Длительность импульса, формируемого одновибратором 36, определяется временем цикла записи в запоминающем устройстве 3. По его заднему фронту одновибратором 37 формируется сигнал Сброс 2, который переводит триггер 33 в исходное состояние и снимает сигнал Запрет, запрещающий работу генератора 29. С момента появления сигнала Исполнить и до конца цикла записи на инверсном выходе триггера 33 действует сигнал, запрещающий вторичную подачу извне сигнала Исполнить. Сигнал Сброс 2 снимает этот запрет. К этому моменту на информационных входах счетчиков 3 и устройства 3 должны быть заданы адресный код и код значения новой ординаты и тогда процесс записи повторится.

В-режиме считывания (воспроизведение функции) на вход 17 подается сигнал Считывание (низкий уровень) триггеры 32 и 33 и генераторы 29 находятся в исходном состоянии, реверсивные счетчики 30 при изменении входных сигналов могут считать тактовые импульсы от генератора 29. На прямом выходе 33 установлен низкий уровень, разрешающий осуществлять считывание из запоминающего устройства 3. I

При изменении входных переменных X , Xg. на единицу младшего разряда цифроаналогового преобразователя 20 срабатывает в каждом из блоков 1 компаратор 22 или нуль-орган 23 и запускает генератор 29. Импульс с выхода любого из генераторов 29 по группе входов 19 проходит через элемент РШИ-НЕ 62 и устанавливает триггер 32 в режим считывания. С выхода триггера 32 сигнал поступает на элемент 65 задержки, и через время tj на выходе элемента ИЛИ 48 появляется сигнал Запрет, который запрещает работу генератора 29 на время четырехтактного цикла считывания. При срабатывании генератора 29 на выходе элемента НЕ 51 появляется

тактовый импульс, который через элемент ИЛИ 46 запускает одновибраторы 34-36, последние, как и в режиме записи, формируют импульсы заданной длительности. Поскольку триггер 33 находится в исходном состоянии, сигналы Загрузка, Выбор кристалла и Сброс 2 не формируются. Одновременно с импульсом на выходе элемента НЕ 51 на выходе элемента НЕ 50так-ИО на

же появляется тактовый импульс считывания, который через элемент ИЛИ 45 запускает одновибраторы 39 и 40. Одновибратор 32 вырабатывает импульс перезаписи, который совместно с им- ts пульсом смены кодов с.выхода одновибратора 35 и сигналами с соответствующих выходов регистра 67 сдвига формирует команды перезаписи информации из запоминающего устройства 3 20 в регистры 7.

Одновибратор 40 формирует импульс в каждом такте считывания, который совместно с соответствующим сигналом с выхода регистра 67 сдвига обес-25 печивает формирование сигнала Разрешение преобразования на выходе 13 и сигналов управления реверсивными счетчиками 30 по группам 10 и 11 выодов. По этим сигналам осуществляет-зо ся увеличение или уменьшение на единицу младшего разряда содержимого счетчика 30 в соответствии с алгоритмом (фиг. 3). Операция перезаписи информации в регистры 7 осуществляет ся таким образом, что в начале каждого такта поступает сигнал, по которым устанавливается код на выходах реверсивных счетчиков 30, т.е. адрес ординаты в запоминающем устройстве 3, а затем появляется соответствующий сигнал перезаписи на одном из выходов группы 8 блока 9. Одновременно через элементы ИЛИ-НЕ 63 и 64 на выходе 16 формируется сигнал Выбор кристалла, который открывает запоминающее устройство 3 только на время считывания информации, а затем вновь его закрывает. Б режиме считывания с появлением импульсов на выходах элементов НЕ 50 и 51 регистр 67 сдвига в первом такте считывания устанавливается в исходное состояние, когда на его выходах логические нули, а затем на первый его выход записывается импульс с выхода элемента НЕ 50. Осуществляется это элементами И-НЕ 54 и- элементами И 41 и 42. Если информационные входы А1-А4 регистра 67 сдвига типа К155ИР1 заземлены, а на входе 40 действует логическая единица, отрицательный перепад на втором управляющем входе С2 устанавливает регистр в исходное состояние. При логическом нуле на третьем управляющем входе V отрицательный перепад

ществляет операции записи или сдвига записанной информации. В первом такте осуществляется запись импульса с выхода элементов НЕ 50, в остальных тактах - сдвиг записанной информации вправо.

При появлении на первом выходе регистра 67 логической единицы элемент И-НЕ 58 сформирует на выходе 13 сигнал Разрешение дл-я реверсивных счетчиков 30 блоков 1. После того, как будет выявлена в запоминающем устройстве 3 первая узловая точка интерполяционной ячейки (фиг. 3), по сигналу Запись на первом (верхнем на фиг. 2) выходе группы 8 выходов блока 9 производится запись в первый регистр группы регистров 7 значения ее ординаты. Задний фронт импульса с выхода одновибратора 39 запускает Одновибратор 38 и по импульсу с его выхода срабатывают одновибраторы 3436, на выходах которых формируются импульсы заданной длительности. Однопервом управляющем вхопе С1 осувременно сигналом Сброс 2 подтверждается исходное состояние триггера 33. Во втором такте в регистре 67 сдвига осуществляется сдвиг единичного сигнала с первого на второй выход. На первом из выходов группы 10 (выход элемента И-НЕ 59) формируется сигнал, при поступлении которого на суммирующий вход реверсивного счетчика содержимое этого счетчика увеличивается на единицу младшего разряда. После установления в запоминающем устройстве 3 нового адреса командой Запись на втором выходе группы 8 выходов осуществляется перезапись во второй из групп регистров 7 значения ординаты узловой точки 2. (фиг. 3) с координатами С ,+1, Xjn. После окончания перезаписи на выходе одновибратора 37 вновь формируется сигнал, который запускает одновибраторы 34 - 36, и процесс считывания в третьем и четвертом тактах значений ординат узловых точек по151вторяется. В третьем такте извлекается из запоминающего устройства 3 значение ординаты с координатами 1Хд„+1, хЧои+П, а в четвертом - значение ординаты с координатами 1:Х/|ц, X2.ii1 С окончанием последнего такта одновибраторы 37 и 38 формируют сигналы, которые устанавливают триггеры 32 и 33 в исходное сос тояние и снимают запрет на работу генератора 29, а по сигналу с второго из выходов группы 11 (блока 9) с выхода одновибратора 38 из реверсивного счетчика 30 второго блока 1 преобразования вычитается единица младшего разряда. В результате описанных операций блоки 1 извлекут из запоминающего устройства 3 значения четьфех ординат интерполяционной ячейки и установятся в исходное состояние в точку 1 с координатами , Xjii . Последняя операция требуется только в случае использования блоков 1 следящего типа. При использовании- блоков 1 поразрядного кодирования или непосредственного считывания вычитание единицы в последнем такте не требуется. Каждый раз, когда изменение напряжения на шинах 2 ввода X и Х2 достигает величины младшего разряда преобразователей 20 срабатывают соответствующие компараторы 22, 23 и генераторы 29 и процесс четырехтактного считывания значений ординат выявленной интерполяционной ячейки повторится. В исходном состояний запоминающее устройство 3 по выходу 16 блока 9 блокировано сигналом Выбор кристалла низкого уровня. Доступ в запоминающее устройство 3 возможен только в момент записи или считывания, когда на выходе 16 блока 9 появляется специально формируемый сигнал высоко го уровня. Длительности импульсов в схеме на фиг. 2, формируемые одновибраторами 34 - 40, указаны для слу чая использования микросхемы памяти типа КР188РУ2А. Аналогичным образом строится рабо та и в случае функционального преобразования по трем независимым переменным Х , Х2. и Х. Процесс считывания информации из запоминающего устройства 3 в этом случае осуществляется в соответствии с алгоритмом, изображенньм на фиг. 4. В первом такте работы по сигналу с выхода 13 8 .1 блока 9 разрешается выполнение блоками 1 преобразования входных переменных из аналоговой .формы в цифровую, накопление кодовых эквивалентон координат узловой точки (фиг. 4) в счетчиках 30 и считывание из запоминающего Устройства ординаты первого узла 1 интерполяции в первый из регистров группы регистров 7, В по- следующих тактах содержимое одного из счетчиков 30 соответствующих блоков 1 каждый раз изменяется на единицу младшего разряда, а код ординаты полученного узла интерполяции (считываемый из запоминающего устройства 3 в соответствии с адресным кодом на его входах) переписывается в соответствующий регистр из группы регистров 7. При этом осуществляется последовательный переход (фиг. 4) из узла 1 в узел 2, затем в узел 3 и т.д. до возвращения в начальный узел 1, выбранный на первом такте ячейки (подобласти) интерполяции. Такая организация считывания в функциональном преобразователе многих переменных не требует дешифрации и коммутации адресных кодов, а следовательно, и дополнительного оборудования при переходе от одной ячейки интерполяции к другой, так как алгоритм считывания для любой ячейки интерполяции одинаков. В этом случае переход от одной ячейки к другой следует рассматривать как перенос начала координат из одной точки в другую, информацию о которой предстоит считать. В общем случае функционального преобразования по многим переменным функциональный преобразователь будет содержать г (где VYI - количество независимых переменных) блоков 1 аналого-цифрового преобразования, по 2 умножгиощих цифроаналоговых преобразователей 5 и регистров 7, односекционное запоминающее устройство 3, суммирзпощий усилитель 6, блок 4 формирования интерполирующих функций и блок 9 синхронизации. Блок 9 по объему используемого оборудования Может быть приравнен к схемам адресных дешифраторов и коммутаторов известного устройства. В то же время переход от известного многосекционного запоминающего устройства к односекционному запоминающему устройству в предлагаемом функциональ.1711

ном преобразователе позволит сэкономить (2 -l) микросхем памяти. Если значения ординат в запоминающем устройстве записаны 12-разрядньм кодом, в функциональном преобразователе двух переменных будет сэкономлено 36 микросхем типа КР188РУ2А, а для трех переменных - 84 микросхемы

-

150688

типа КР188РУЗА, что даст экономию в 83 и 336 руб. на один функциональный преобразователь двух и трех переменных соответственно. С увеличением

5 числа переменных и разрядности записанных в запоминающее устройство слов экономический эффект возрастает.

«

a /r

.J

1 I

-1

H

I

-J I

-r I

.-PC

h

/ j/tfVJ .

r /

I/

/№«v;

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Функциональный преобразователь нескольких переменных | 1976 |

|

SU636633A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Функциональные преобразователи с аналого-цифровым представлением информации | |||

| М., Энергия, 1973, с | |||

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-09-23—Публикация

1981-10-19—Подача