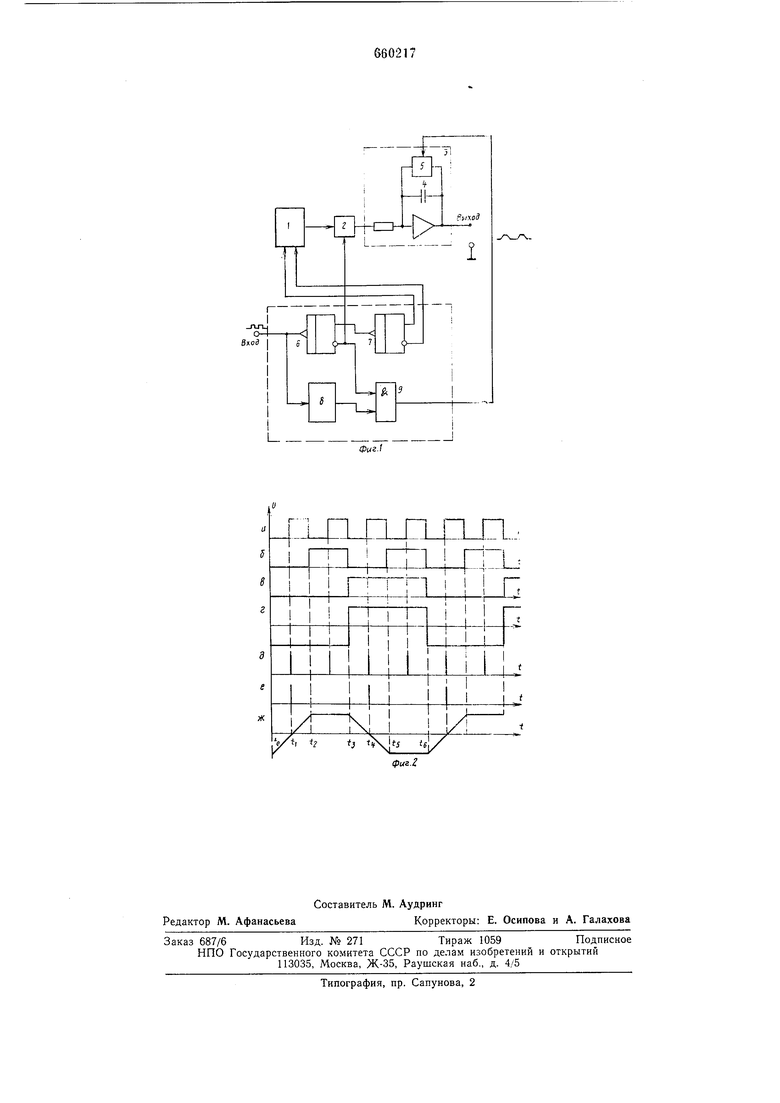

последнего - на вход триггера 7. Периоды импульсов па выходе триггеров 6 п 7 соответственно в два и четыре раза больше входных. Выходные сигналы триггера 7 (фиг. 2,в) управляют блоком 1 формирования биполярных импульсов, которые, при замкнутом дополнительном ключе 2, поступают на вход интегратора 3.

Пусть в начальный момент времени напряжение на выходе блока 1 имеет отрицательную полярность (фиг. 2,г). Тогда напряжение на выходе интегратора 3 (фиг. 2,ж) начнет линейно возрастать до момента времени t-. Теперь управляющие напряжение на дополнительном ключе 2 соответствует «логическому О, при этом ключ 2 закрывается, отключая от интегратора 3 входное напряжение. Интегратор 3 переходит на режим запоминания, который длится до момента времени t, когда управляющее напряжение ключа 2 становится равным «логической 1.

Дополнительный ключ 2 открывается, пропуская на вход интегратора 3 напряжение положительной полярности от блока 1 формирования биполярных импульсов. Выходное напряжение интегратора 3 начинает линейно убывать от момента времени /з до момента 5, когда снова происходит запирание дополнительного ключа 2 управляющим напряжением, равным «логическому О. Интегратор 3 снова переходит на режим запоминания от момента времени 5 ДО момента 6, а затем цикл повторяется.

Формирователь 8 коротких импульсов запускается входными импульсами при переходе «О-1, при этом формируются короткие импульсы, частота следования которых в два раза меньше исходной (фиг. 2,е). Короткие импульсы с выхода элемента И 9 поступают на управляющий вход аналогового ключа 5, вызывая на время действия короткого импульса разряд накопительного конденсатора 4. Моменты и t (фиг. 2,ж) разряда конденсатора 4 соответствуют моментам перехода через ноль возрастающего, либо убывающего напряжения выходного трапецеидального сигнала. Привязка разрядов конденсатора к моментам перехода через нулевое значение обеснечивает стабильность выходного сигнала относительно нулевого уровня. Незначительные различия в напряжении положительной и отрицательной полярностей блока 1 формирования биполярных импульсов, а также влияние напряжения н тока смещения усилителя, содержащегося в интеграторе, приводят к сползанию выходного сигнала в сторону насыщения усилителя, если отсутствует периодический разряд накопительного конденсатора 4.

В случае изменения амплитуды биполярных импульсов или изменения параметров

цепей интегрирования изменяется лишь амплитуда трапецеидального сигнала, а форма его сохранется, так как длительность нарастания, спада и участка постоянного напряжения определяются импульсами управления дополнительным аналоговым ключом 2.

При повышении частоты прямоугольных импульсов при неизменных по амплитуде

биполярных импульсах, форма импульсов при этом сохраняется. Если блок 1 формирования биполярных импульсов построен так, что с увеличением частоты пропорционально изменяется амплитуда биполярных

импульсов, то сохраняется и амплитуда трапецеидального сигнала.

Формирователь трапецеидальных импульсов разработан для использования в тренажере для задания определенного закона

двилсения фигуры на экране видеоконтрольного устройства. В частности, для движения фигуры по периметру экрана необходимо иметь два генератора трапецеидальных колебаний, выходные сигналы которых

сдвинуты один относительно другого на 90°, при этом важно иметь стабильные по длительностям и относительно нулевого уровня имнульсы в виде равнобочной трапеции со средней линией, равной 2о.

.

Формула изобретения

Формирователь импульсов, содержащий блок формирования биполярных импульсов, интегратор, накопительный конденсатор которого щунтирован ключом, и формирователь коротких импульсов, отличающийся тем, что, с целью получения выходных импульсов в виде равнобочной трапеции со средней линией равной 2а, где а-

меньшее основание трапеции, в него введены дополнительный ключ, триггеры и элемент И, причем выход блока формирования биполярных импульсов соединен со входом интегратора через дополнительный ключ,

счетный вход первого триггера соединен со входом тактовых импульсов и входом формирователя коротких импульсов, выход которого соединен с первым входом элемента И, инверсный выход первого триггера соединен с управляющим входом дополнительного ключа и вторым входом элемента И, выход которого соединен с управляющим входом ключа, а прямой - со счетным входом второго триггера, прямой и инверсный

выходы которого соединены с первым и вторым входами блока формирования биполярных импульсов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 174664, кл. Н ОЗК 4/00, 1971 г.

2. Патент Японии № 48-11501, кл. 98(5) С 12, опублик. 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1978 |

|

SU769717A1 |

| Формирователь трапецеидальных симметричных импульсов | 1978 |

|

SU712939A1 |

| Удвоитель частоты сигнала | 1979 |

|

SU828366A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Источник калиброванных напряжений | 1986 |

|

SU1345179A1 |

| Преобразователь интервал-напряжение | 1985 |

|

SU1287272A1 |

| Устройство для управления регулируемым мостовым инвертором | 1988 |

|

SU1548830A1 |

| Способ формирования дефибрилляционного импульса со ступенчатой формой фронта и среза и устройство для его осуществления | 2023 |

|

RU2827917C1 |

| Формирователь импульсов | 1980 |

|

SU944091A1 |

| Устройство для управления вентильным преобразователем со слежением | 1988 |

|

SU1607061A1 |

-Ui-UJU

Авторы

Даты

1979-04-30—Публикация

1977-04-06—Подача