УСТРОЙСТВО для ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ

(54) ИЗ ПРОИЗВЕДЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелятор | 1976 |

|

SU599272A1 |

| Устройство для определения параметров объекта | 1987 |

|

SU1446602A1 |

| УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ ИЗ СУММЫ КВАДРАТОВ ДВУХ ВЕЛИЧИН | 1992 |

|

RU2037201C1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1993 |

|

RU2082996C1 |

| Адаптивный фильтр | 1988 |

|

SU1522382A1 |

| КОСИНУСНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2065203C1 |

| УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ ИЗ СУММЫ КВАДРАТОВ ТРЕХ ВЕЛИЧИН | 1992 |

|

RU2024938C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ УПРАВЛЯЮЩИХ ВОЗДЕЙСТВИЙ ДЛЯ ОБЕСПЕЧЕНИЯ УСТОЙЧИВОЙ РАБОТЫ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ | 2011 |

|

RU2475828C1 |

| Устройство для прогнозирования надежности по результатам ускоренных испытаний | 1987 |

|

SU1508238A1 |

| УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ ИЗ СУММЫ ИЗВЕСТНОЙ И КВАДРАТА НЕИЗВЕСТНОЙ ВЕЛИЧИН | 1992 |

|

RU2047218C1 |

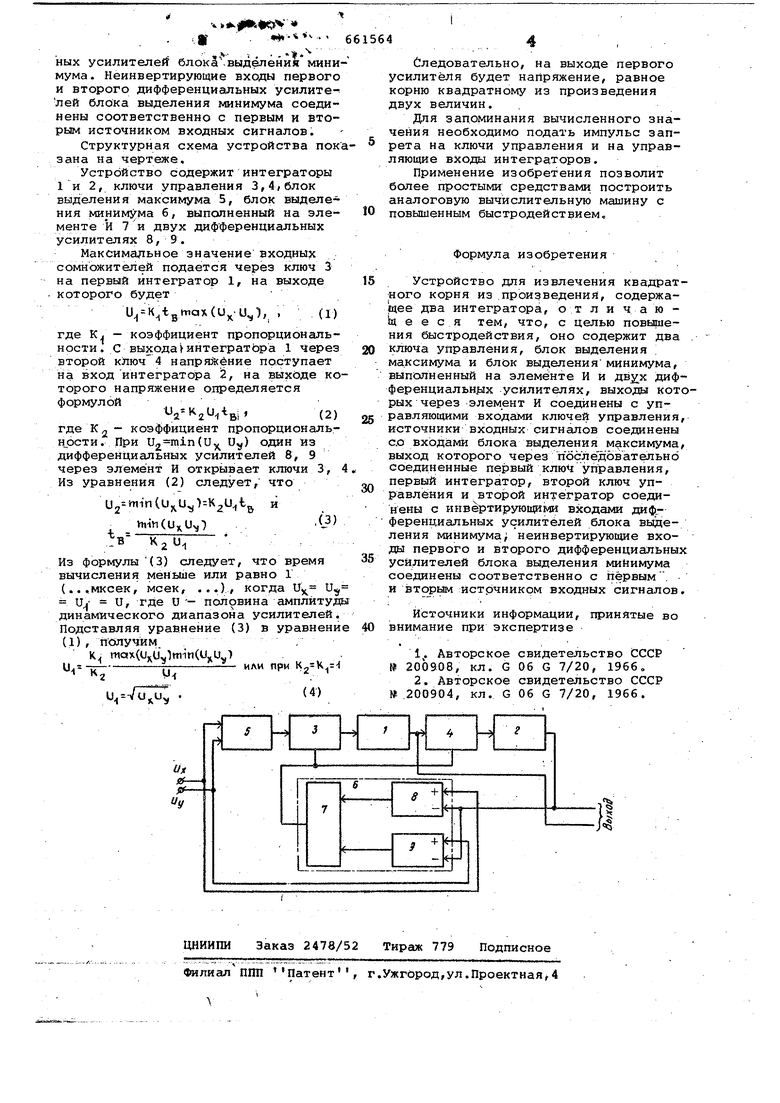

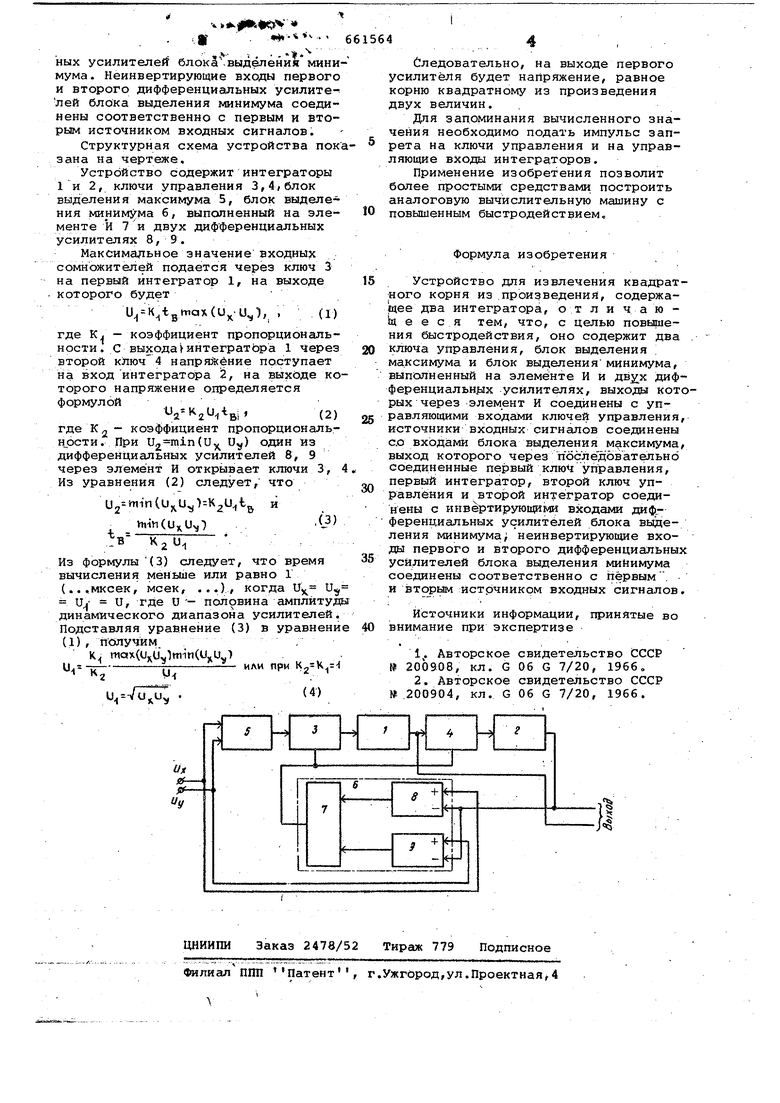

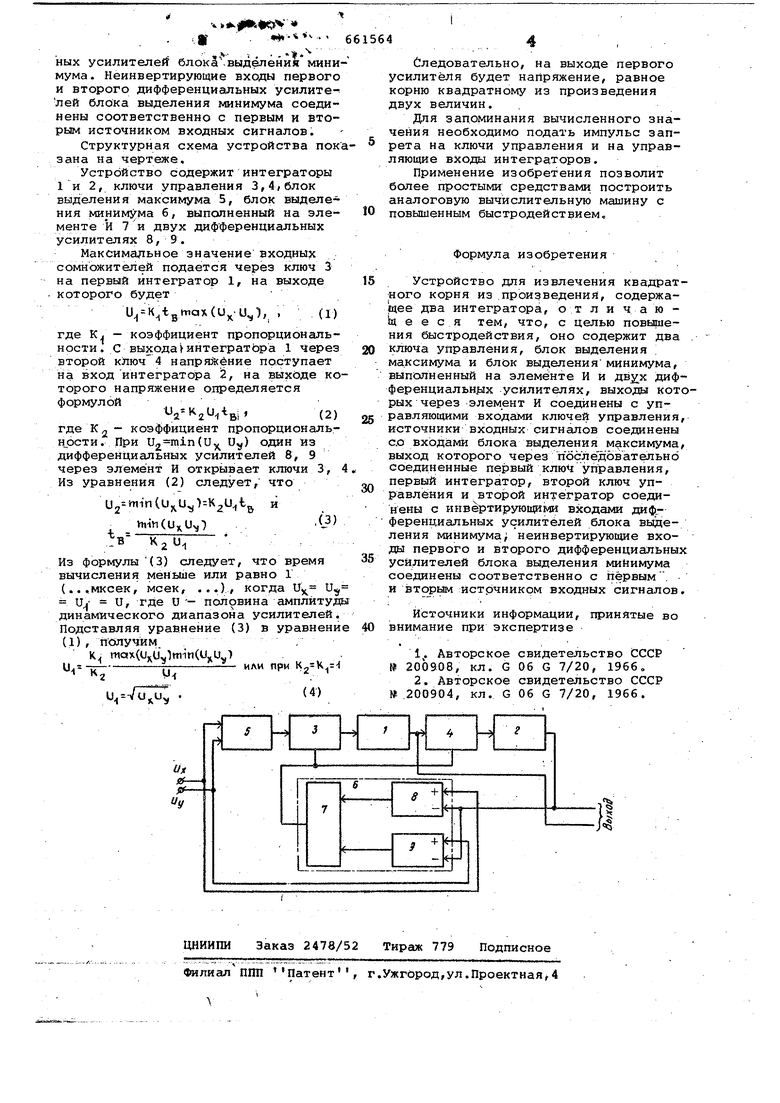

Изобретение может быть использовано в быстродейр«гвую1цих аналоговых вычислительных машинах, коррелятора где требуется производить операцию извлечения квадратного корня из про изведения двух величин, а также вычисление квадратного корня из одной величины. Устройство для выполнения аналогичной операции и глножительные устройства 1 и 2 известны. Однако последовательное соединение блока у нохсения и блока извлечения квадратн го корня увеличивает габариты и потребляемую мощность вычислительных машин.Кроме того,эти схемы без дополнительных устройств не позволяют запоминать результат, что особенно важно при .гюстроении корреляторов. Наиболее близким техническим решением к изобретению является устройство для извлечения квадратного корня из произведения 2, содержащее два интегратора, соединенных последовательно, пиковый детектор на выходе, нуль-органы и блок управ пенйя. Недостатком этого устройства явпяется зависимость времени вычисления корня квадратного (при замене постоянного напряжения и s и х вторым сомножителем) от величины сомножителя, поступающего на вход интегратора (и) и нуль-органа (U). При и и время вычисления (tg) резко увеличивается, так как t - f(U) . Наличие пикового детектора с определенной постоянной времени увеличивает запаздывание правильной выдачи вычисления, что снижает быстродействие и точность работы. Цель изобретения повышение быстродействия. Эта цель достигается тем, что предложенное устройство для извлечения квадратного корня из произведения содержит два ключа управления, блок выделения максимума, блок выделения минимума, выполненный на элементе И и двух дифференциальных усилителях, выходы которых через элемент И соединены с управляющими входами ключей управления, источники входных сигналов соединены со входами блока выделения максимума, выход которого через последовательно соединенные первый ключ управления, первый интегратор, второй ключ Управления и второй интегратор соединены с инвертирующими входами дифференциальч.|( ,.ii . ных усилителей блока .выдёлёниЬ мини мума. Неинвертирующие входы первого и второго дифференциальных усилителей блока выделения минимума соединены соответственно с первым и вторым источником входных сигналов. Структурная схема устройства пок зана на чертеже. Устройство содержит интеграторы 1 и 2, ключи управления 3,4/блок выделения максимума 5, блок выделения минимума 6, выполненный на элементе И 7и двух дифференциальных усилителях 8, 9. Максимальное значение входных сомножителей подается через ключ 3 на первый интегратор 1, на выходе . которого будет U -K tgmax(,,), ,(I) где К , - коэффициент пропорциональности. С выхода интегратора 1 через второй ключ4 напряйс ние поступает на вход интегратора 2, на выходе ко торого напряжение определяется формулой V 2 f4i(2) где Kj коэффициент пропорциональн ости. При Uj,min(U К) один из дифференциальных усилителей 8, 9 через элемент И открывает ключи 3, Из уравнения (2) следует, что () и Ып(,) Из формулы (3) следует, что время вычисления меньше или равно 1 (...мксек, мсек, ...), когда Ux и.у и, где и -- половина амплитуд динамического диапазона усилителей. Подставляя уравнение (3) в уравнени (1), получим. К, niax(U,Uv)min( JLL или при . .... 4 , 4 Следовательно, на выходе первого усилителя будет напряжение, равное корню квадратному из произведения двух величин. Для запоминания вычисленного значения необходимо подать импульс запрета на ключи управления и на управляющие входы интеграторов. Применение изобретения позволит более простыми средствами построить аналоговую вычислительную машину с повышенным быстродействием. Формула изобретения Устройство для извлечения квадратного корня из.произведения, содержаlaee два интегратора, от л и чаю Ьд е е с я тем, что, с целью повышения быстродействия, оно содержит два . ключа управления, блок выделения ; ма.ксимума и блок выделенияминимума, выполненный на элементе И и дифференциальных усилителях, выходы которых через элемент И соединены с управляющими входами ключей управления, источники входных сигналов соединены С.О входами блока выделения максимума, выход которого через пбследовательно соединенные первый ключ управления, первый интегратор, второй ключ управления и второй интегратор соединены с инвертирующими входами диф,ференциальных усилителей блока выделения минимума; неинвертирующие входы первого и второго дифференциальных усилителей блока выделения минимума соединены соответственно с первым. и вторым истрчником входных сигналов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 200908, кл. G 06 G 7/20, 1966, 2.Авторское свидетельство СССР №,200904, кл. G 06 G 7/20, 1966.

Авторы

Даты

1979-05-05—Публикация

1977-11-09—Подача