Изобретение относится к автоматике и вычислительной технике, а именно к устройствам извлечения квадратного корня из суммы квадратов трех величин, и может быть использовано в вычислительных устройствах для преобразования координат, определения суммарного вектора с высокой точностью.

Известно устройство для извлечения корня, содержащее три амплитудных модулятора, генератор синусоидальных напряжений, два сумматора, фазовращатель, ограничитель, детектор и фильтр.

Устройство осуществляет сложение модулированных по амплитуде высокочастотных колебаний напряжений, сдвинутых по фазе относительно друг друга, и выделение огибающей суммарного сигнала. Устройство ограничено по быстродействию и точности измерений.

Известен функциональный преобразователь, содержащий операционный усилитель, три инвертора, блоки выделения модуля, каждый из которых выполнен на трех двухвходовых диодных элементах, и несколько резистивных звезд с четырьмя входами каждая. Устройство обладает высоким быстродействием, в нем нет сложных элементов, однако наличие большого количества диодов ограничивает точность измерений из-за падения в них напряжения.

Наиболее близким техническим решением к заявляемому по большему количеству сходных существенных признаков и достигаемому эффекту является устройство для извлечения квадратного корня из суммы квадратов трех величин, содержащее три блока выделения модуля сигналов, подключенных входами к входам устройства с первого по третий, соответственно, три двухвходовых и один трехвходовый блоки вычисления максимума, входы которых подключены к выходам блоков выделения модулей, а выходы подключены к входам многовходового сумматора на операционном усилителе с резистивной обратной связью.

Устройство простое по конструкции и построено на принципе кусочно-линейной аппроксимации искомого выражения суммой из комбинации входных напряжений, которые в зависимости от их соотношений складывают с постоянными коэффициентами, задаваемыми соотношением сопротивлениями резистора обратной связи ОУ и сопротивлений его входных резисторов.

Точность преобразования, определяемая точностью аппроксимации, ограничена, что обусловлено выбором семи постоянных коэффициентов независимо от величины входных напряжений. Методическая погрешность составляет около 4%.

Целью изобретения является уменьшение погрешности преобразования.

Цель в устройстве для извлечения квадратного корня из суммы квадратов трех величин, содержащем три блока выделения модуля, подключенных входами к входам устройства с первого по третий, соответственно, и сумматор, выход которого является выходом устройства, достигается тем, что в него введены амплитудный селектор, два блока деления и два управляемых делителя напряжения, причем к первому входу сумматора подключен выход максимального сигнала амплитудного селектора, этот же выход подключен к первому входу первого блока деления и к первому входу второго блока деления, выход медианного сигнала амплитудного селектора подключен к второму входу первого блока деления и к сигнальному входу первого управляемого делителя, выход минимального сигнала амплитудного селектора подключен к второму входу второго блока деления и к сигнальному входу второго управляемого делителя напряжения, выход первого блока деления подключен к управляющему входу первого управляемого делителя напряжения, выход второго блока деления подключен к управляющему входу второго управляемого делителя напряжения, выход первого управляемого делителя напряжения подключен к второму сумматору, а выход второго управляемого делителя напряжения подключен к третьему входу сумматора, входы амплитудного селектора с первого по третий подключены к выходам блоков выделения модуля с первого по третий соответственно: амплитудный селектор содержит два трехвходовых блока вычисления максимума, три двухвходовых блока вычисления максимума и минимума и алгебраический сумматор, причем два входа первого двухвходового блока вычисления максимума и минимума подключены соответственно к первому и второму входам амплитудного селектора, два входа второго двухвходового блока вычисления максимума и минимума подключены соответственно к второму и третьему входам амплитудного селектора, два входа третьего двухвходового блока вычисления максимума и минимума подключены соответственно к второму и третьему входам амплитудного селектора, выходы максимальных сигналов двухвходовых блоков вычисления максимума и минимума подключены к входам первого трехвходового блока вычисления максимума, выходы минимальных сигналов двухвходовых блоков вычисления максимума и минимума подключены к входам второго трехвходового блока вычисления максимума, выход максимального сигнала амплитудного селектора подключен к выходу первого трехвходового блока вычисления максимума, выход медианного сигнала подключен к выходу второго трехвходового блока вычисления максимума, выход минимального сигнала подключен к выходу алгебраического сумматора, входы которого с первого по третий подключены к входам амплитудного селектора с первого по третий, соответственно к четвертому и пятому входам алгебраического сумматора подключены выходы первого и второго трехвходовых блоков вычисления максимума соответственно.

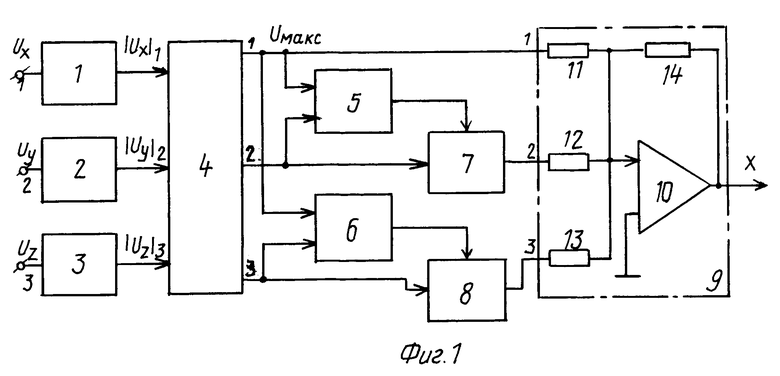

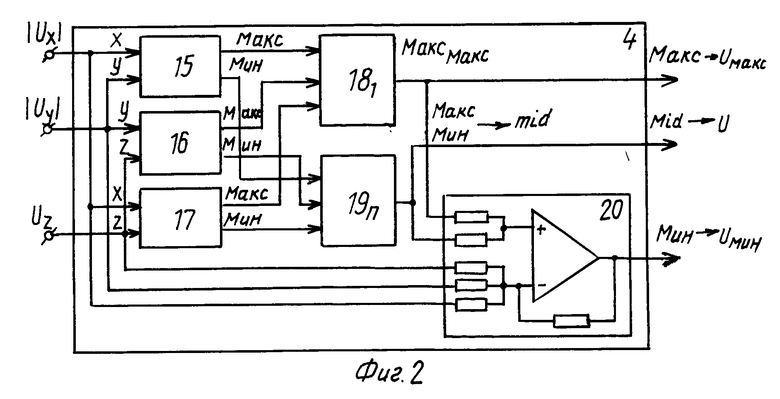

На фиг.1 показана функциональная схема устройства; на фиг.2 - амплитудный селектор.

Устройство для извлечения квадратного корня из суммы квадратов трех величин содержит: блоки 1, 2, 3 выделения модуля; амплитудный селектор 4; блоки деления 5 и 6; управляемые делители напряжения 7 и 8; сумматор 9.

Блоки в устройстве соединены следующим образом. Входы блоков 1-3 выделения модулей с первого по третий подключены к входам устройства с первого по третий соответственно. Выходы блоков 1-3 выделения модулей с первого по третий подключены к входам амплитудного селектора 4 с первого по третий соответственно. Первый выход амплитудного селектора 4 по сигналу максимальной амплитуды подключен к первому входу сумматора 9 и к первым входам блоков деления 5 и 6. Второй выход амплитудного селектора 4 по сигналу медианной амплитуды подключен к второму входу блока деления 5 и через управляемый делитель напряжения 7 подключен к второму входу сумматора 9. Третий выход амплитудного селектора 4 по сигналу минимальной амплитуды подключен к второму входу блока деления 6 и через второй управляемый делитель напряжения 8 подключен к третьему входу сумматора 9, выход которого подключен к входу устройства. Выходы блоков деления 5 и 6 подключены к управляющим входам управляемых делителей напряжения 7 и 8, соответственно.

Амплитудный селектор 4 (фиг.2) содержит три двухвходовых блока 15, 16, 17 вычисления максимума и минимума, два трехвходовых блока 18, 19 вычисления максимума и алгебраический сумматор 20. Блоки в амплитудном селекторе 4 соединены между собой следующим образом. Два входа блока 15 подключены соответственно к первому и второму входам (x,y) амплитудного селектора 4, два входа блока 16 подключены соответственно к второму и третьему входам (y, z) амплитудного селектора 4, два входа блока 17 подключены соответственно к первому и третьему входам (x,z) амплитудного селектора 4. Три выхода максимального сигнала блоков 15, 16, 17 подключены к трем входам блока вычисления максимума 18, а три выхода минимального сигнала блоков 15, 16, 17 подключены к трем входам блока вычисления максимума 19. К трем выходам амплитудного селектора 4 подключены к первому выходу (макс) подключен выход блока вычисления максимального сигнала блока 18; к второму выходу (mid) подключен выход блока вычисления максимума блока 19; к третьему выходу (мин) подключен выход алгебраического сумматора.

Устройство работает следующим образом. На входы устройства поступают входные сигналы напряжения Ux,Uy,Uz . Эти сигналы каждый поступает на свой блок выделения модуля 1, 2, 3, с выхода которых получают сигналы I Ux I, I Uy I, I Uz I . Эти сигналы поступают на три входа амплитудного селектора 4, с первого выхода которого снимают сигналы максимальной амплитуды Uмакс ,со второго - сигнал среднего значения амплитуды U, с третьего - сигнал минимальной амплитуды Uмин, причем Uмин < U <макс.

Сигналы Uмакс и U с первого и второго выходов амплитудного селектора 4 поступают на первый и второй входы блока деления 5, а сигналы Uмакс и Uмин с первого и третьего выходов амплитудного селектора 4 поступают на первый и второй входы блока деления 6. С выхода блока деления 5 снимают напряжение, пропорциональное K1 = =Uмакс/U, а с выхода блока деления 6 снимают напряжение, пропорциональное K2 = =Uмакс/Uмин. Эти напряжения поступают на управляющие входы управляемых делителей напряжения 7 и 8 соответственно, а на их сигнальные входы поступают сигналы U и Uмин соответственно. С выходов управляемых делителей напряжения 7 и 8 снимают напряжения U/K1 и Uмин/К2 соответственно. С первого выхода амплитудного селектора 4 напряжение Uмакс поступает на первый вход сумматора 9, с выхода управляемого делителя напряжения 7 напряжение U/K1 поступает на второй вход сумматора 9, а на его третий вход поступает напряжение Uмин/K2 с выхода управляемого делителя напряжения 8.

Амплитудный селектор 4 формирует их входных напряжений I Ux I, I Uy I, I Uz I три выходных напряжения Uмакс, Umid, Uмин следующим образом. Для простоты обозначены сигналы, поступающие на вход амплитудного селектора 4, (x = Ux, y = Uy, z = Uz). На двухвходовые блоки вычисления максимума далее макс и минимума далее мин 15, 16, 17 поступают попарно сигналы: x, y; y,z; x, z - соответственно. С выходов этих блоков снимают сигналы двух типов из каждой пары входных сигналов - макс и мин. Все сигналы макс поступают на три входа первого трехвходового блока вычисления максимума 18, а все сигналы мин поступают на три входа второго трехвходового блока вычисления максимума 19. С выходов этих блоков снимают сигнал максимальный из трех входных сигналов, но с выхода блока 18 снимают максимальный сигнал из максимальных, а с выхода блока 19 снимают максимальный сигнал из минимальных, соответствующий среднему по величине выходному сигналу mid из трех входных сигналов амплитудного селектора 4. Сигналы Uмакс и Umidпоступает на первый и второй выходы амплитудного селектора 4. Алгебраический сумматор 20 вычитает из суммы сигналов Uмакс, Umid, Uминсигналы напряжений Uмакс, Umid, и на выходе алгебраического сумматора получают сигнал напряжения Uмин, который поступает на третий выход амплитудного селектора 4.

На выходе сумматора 9 формируется напряжение

Uвых = Ко(Uмакс + aU/K1 + bUмин/K2, где коэффициенты Ко, а, b определяются соотношением сопротивлений резисторов сумматора 9:

Ko = R14/R11, Koa = R14/R12, Kob = =R14/R13.

Коэффициенты могут быть подобраны таким образом, чтобы с минимальной погрешностью обеспечить равенство двух выражений: =Ko(Uмакс+aU/K1+bUмин/K2) (1)

=Ko(Uмакс+aU/K1+bUмин/K2) (1)

По исходному условию Uz < Uu < Ux, K1 = Ux/Uy, K2 = Ux/Uz, K1<K2.

Для простоты рассуждений положим Ко = 1 (учтем это упрощение в дальнейшем). Выражение (1) можно представить в следующем виде:

Uz·  = Uz·[K2+aK2/K

= Uz·[K2+aK2/K

В выражении (2) Uz можно сократить, тогда равенство (1) будет выполняться при равенстве: = [K2+aK2/K

= [K2+aK2/K

Следовательно, нужно выбрать такие значения коэффициентов а и b, чтобы погрешность выражения (1) была минимальна.

Предположим, что Uz намного меньше двух других напряжений, тогда выражение (1) упрощается и сводится к выражению: = Ux+aUy/K1, откуда

= Ux+aUy/K1, откуда = K1+a/K1 (4)

= K1+a/K1 (4)

Из выражения (4) определим коэффициент а, приняв K1 = 1:

a=K1( -K1)= 0,4142.

-K1)= 0,4142.

Погрешность а1 при выполнении равенства (4) будет равна:

q1= {[K1+0,4142/K1]/[ ] - 1}·100 % (5)

] - 1}·100 % (5)

Из выражения (5) определим значение коэффициента К1, при котором погрешность а1 будет иметь экстремальное значение. Для этого определим выражение для производной (q1) и, приравняв ее к нулю, определим К1( q1макс), как 0,4142/(1-0,8284) = 1,5536.

Этому значению К1 будет соответствовать величина экстремальной погрешности, равная Iq1 I макс = -1,48%.

Подставим а = 0,4142 в выражение (3) и, положив К1 = К2 = 1 определим величину коэффициента b. Коэффициент b = 0,31785.

Таким образом, при К1 = К2 = 1 и выбранных коэффициентах, погрешность равенства выражения (1) будет равна нулю. Оценим величину погрешности при других возможных значениях коэффициентов К1 и К2.

При К2>>K1 коэффициент b оказывает минимальное влияние на результат измерений, что видно из выражения (1), а величина погрешности в этом случае, как было показано, не превышает значение - 1,48%. Определим, при каком значении отношения К2/К1 погрешность измерения будет иметь эстремальное значение.

Из выражения (3) определим погрешность измерения q2:

q2= {[(K2+ 0,4142K2)/K _1}100 % (6)

_1}100 % (6)

Домножим числитель и знаменатель в выражении для q2 на К2 и, обозначив (К2/K1)2 = =С, продифференцируем функцию q2 по С и приравняем ее нулю. После преобразований получим:

0,4142(К22 + С + 1) - 0,5(К22 + 0,4142С + +0,3178) = 0

Откуда получим:

С = 0,4142 К22 - 1,2326 (7)

Как видно из (7) область существования экстремумов зависит от значения коэффициента К2. Определим из (7) значение К2 для минимального значения Смин = 1, получим К2 = 2,32. Подставим его в выражение для ошибки (6) и получим q2 = -3%. С увеличением К2/К1 коэффициент К2 будет увеличиваться, а погрешность q2 будет уменьшаться, что видно (6), до величины q2 = -1,48%.

Определим значение методической ошибки q2 в окрестности значений К1= 1,55, соответствующих экстремуму q1. Получим:

Если К1 = К2 = 1,55, то q2 = -3,58%

Если К1 = К2 = 1,5, то q2 = -3,57%

Если К1 = К2 = 1,6, то q2 = -3,65%

Если К1 = К2 = 1,7, то q2 = -3,64%.

Как видно из проведенного анализа значений погрешностей, q2 имеет экстремальное значение около -3,65%. Это означает, что напряжение Uвыхна выходе сумматора 9 будет получаться меньше истинного значения максимально в 1,038 раза. Чтобы получить методическую погрешность измерений в 2 раза меньше, т. е. около 1,9%, следует увеличить выходное напряжение устройства в 1,019 раза, чему и должен быть равен коэффициент Ко выражения (1). Такая коррекция выходного напряжения осуществляется с помощью выбора резисторов сумматора 9:

Ko=R14/R11=1,019;

Ko a=R14/R12=0,422;

Ko b=R14/R13=0,324.

В этом устройстве для извлечения квадратного корня из суммы квадратов трех величин методическая ошибка вычисления равна 1,9% , что в 2 раза меньше, чем у прототипа.

Заявленное устройство имеет более широкие функциональные возможности по сравнению с известными аналогичными устройствами, так как позволяет определять отношение искомых сигналов, которое является одним из важных параметров при исследовании входных сигналов.

Использование: в вычислительной технике в качестве прецизионного функционального преобразователя при определении модуля вектора. Цель: повышение точности измерений. Сущность изобретения: такое устройство реализует приближенное равенство:  . Устройство содержит три блока выделения модуля, амплитудный селектор, два блока деления, два управляемых делителя напряжения и сумматор, выход которого является выходом устройства. Положительный эффект: повышение точности вычисления модуля вектора за счет измерений отношений входных сигналов, методическая и инструментальная погрешность измерений при изменении входных сигналов в широком динамическом диапазоне, не превышает 2%. 1 з.п.ф-лы, 2 ил.

. Устройство содержит три блока выделения модуля, амплитудный селектор, два блока деления, два управляемых делителя напряжения и сумматор, выход которого является выходом устройства. Положительный эффект: повышение точности вычисления модуля вектора за счет измерений отношений входных сигналов, методическая и инструментальная погрешность измерений при изменении входных сигналов в широком динамическом диапазоне, не превышает 2%. 1 з.п.ф-лы, 2 ил.

| Устройство для извлечения квадратного корня | 1974 |

|

SU503255A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-12-15—Публикация

1992-03-31—Подача