СП

оо tc

О9

00

Изобретение относится к вычислительной технике и автоматике и может быть использовано для прогнозирования надежности технических объектов по результатам ускоренных испытаний, когда до испытаний априорная информация о предельных значениях предельных свойств (сопротивляемости) технических объектов отсутствует.

Цель изобретения - повышение точности устройства.

Сущность изобретения состоит в следу гощем.

В отличие от устройства-прототипа, в котором прогноз надежности осуществляется с помощью неизменной во времени условной .функции F(x)y(, распределения внешнего воздействия относительно гипотезы о том, что допусти- мое значение воздействия принадлежит отрезку x,x-i-dx7, в предлагаемом устг ройстве учитывается изменение., математического ожидания сопротивляемости при форсированных нагрузках, обусловленное старением.

По статистике об отказах в процессе ускоренных испытаний оцениваются статистическая функция сопротивляемости (х)и статистическая функ- UJiH надежности R(n)j, .Затем осуществляется прогноз надежности Rj(n) , при форсированном режиме нагруження, соответствующем случайному процессу воздействия .

Rfi(n),Hur |1 , dF.Cx.f,

п - глубина прогноза, выражен- нал через число интервалов корреля- 1щи случайного процесса внешнего воздействия (п ),

ЛИ - интервал корреляции исследуемого случайного процесса; условная функция распределения внешнего воздействия относительно гипотезы о том, что предельное (допустимое) значение воздействия принадлежит элементарному отрезку х, X + dxj;

dF,j(x) - вероятность элементарной гипотезы X 4- dx.

Функция F А (х ) j, 3 g для каждого 1-го значения определяется как

,где Z

, р. expr-exp(-Z;g)J,

(2)

1-е

J I- ic jyut

- нормированное уклонениЪ от моды;

Z,-f - АУН. (Xie РуиЬ 3)

|Ь параметр масштаба распределения наибольших некоррелированных значений случайного процесса нагруже- ния;

т параметр положения этого же распределения;

Х|5 - i - значение сопротивляемости На 1-м шаге прогноза, получаемое путем разбиения ее возможных значе- ршй На К подынтервалов;

РУК N /SH

- и -

/5 aw

(4)

и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ УПРАВЛЯЮЩИХ ВОЗДЕЙСТВИЙ ДЛЯ ОБЕСПЕЧЕНИЯ УСТОЙЧИВОЙ РАБОТЫ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ | 2011 |

|

RU2475828C1 |

| Устройство формирования оптимальных управляющих воздействий для обеспечения устойчивой работы сложных технических систем | 2017 |

|

RU2674281C1 |

| Устройство для диагностики и прогнозирования отказов | 1989 |

|

SU1629898A1 |

| Устройство для прогнозирования времени восстановления сложного технического объекта | 1989 |

|

SU1661797A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| УСТРОЙСТВО ДЛЯ ВЫЗОВА ПОДПРОГРАММ | 1990 |

|

RU2009538C1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для возведения в степень (его варианты) | 1982 |

|

SU1076905A1 |

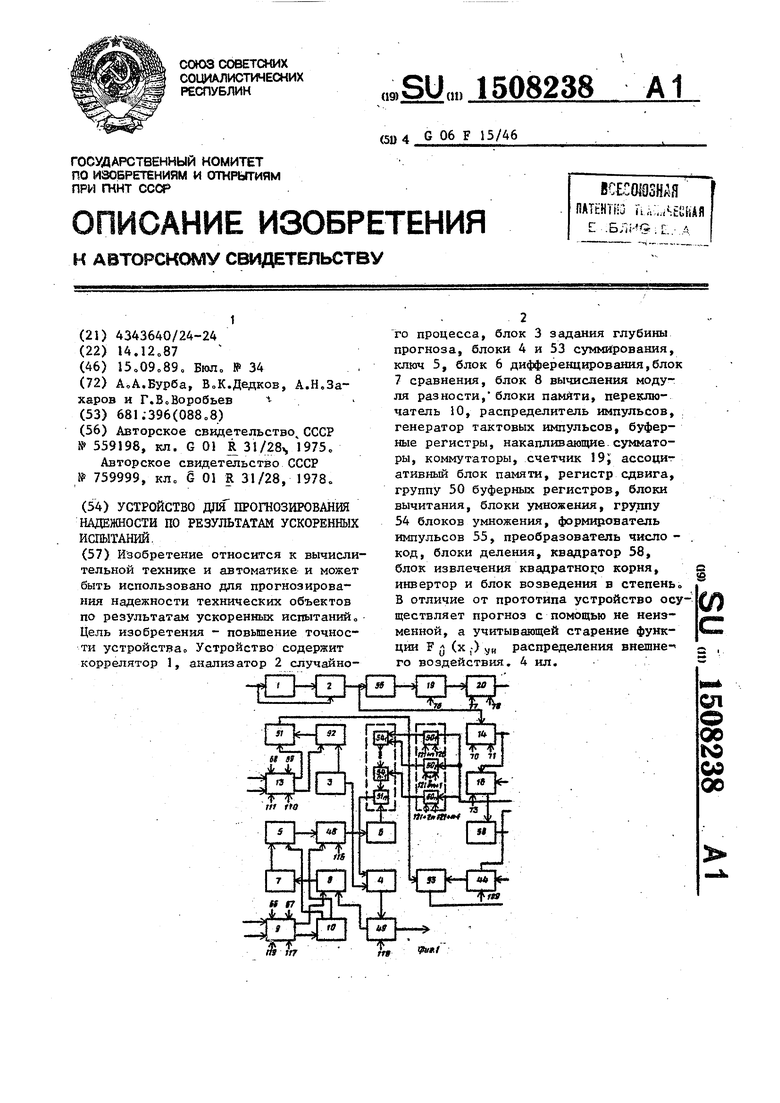

Изобретение относится к вычислительной технике и автоматике и может быть использовано для прогнозирования надежности технических объектов по результатам ускоренных испытаний. Цель изобретения - повышение точности устройства. Устройство содержит коррелятор 1, анализатор 2 случайного процесса, блок 3 задания глубины прогноза, блоки 4 и 53 суммирования, ключ 5, блок 6 дифференцирования, блок 7 сравнения, блок 8 вычисления модуля разности, блоки памяти, переключатель 10, распределитель импульсов, генератор тактовых импульсов, буферные регистры, накапливающие сумматоры, коммутаторы, счетчик 19, ассоциативный блок памяти, регистр сдвига, группу 50 буферных регистров, блоки вычитания, блоки умножения, группу 54 блоков умножения, формирователь импульсов 55, преобразователь число-код, блоки деления, квадратор 58, блок извлечения квадратного корня, инвертор и блок возведения в степень. В отличие от прототипа устройство осуществляет прогноз с помощью не неизменной, а учитывающей "старение" функции Fи (XI)Yи распределения внешнего воздействия. 4 ил.

где Кл(п)

УИ to

- функция надежности

н

при (|jopcnpoBaHH ix нагрузках или вероятность того, что за время разу внешнее по отношенио к испыты- ваемому техническому объекту воздействие не превысит допустимого с учетом старения;

F/i(x) - статистическая функция распределения сопротивляемости, полу ченная по результатам ускоренных испытаний, основная и исчерпываюш;ая характерист1-1Ка допустимого предела величины внешнего воздействия, приводящего испытываемый технический объект к отказу;

и

и

- наибольшее случайное воздействие на отрезке времени, равном интервалу корреляции;

(1) 40

(5)

N - объем выборки наибольших не

коррелированных значений U.- ;

Zf J. .1 . t |vj -

.fj, ищ постоянные, oi конкретного Nj.

зависящие

50

Значение i сопротивляемости на 1-м шаге прогноза определяется как

Х

+ дх

.К .. (т -)

(6)

где Лх - величина шага разбиения интервала изменения сопротивляемости}

Xj - математическое ожидание сопротивляемости:

г X., - ml;

(7)

5

X - начальное значение математического ожидания сопротивляемости при

m - коэффициент, определяющий скорость старения.

После этого определяется степень близости эмпирической функции надежности R (п), и прогнозируемой R Р помощи критерия Колмогорова, который предусматривает выполнение неравенства

d max |Кд(п),, -R((n);j

(8)

где d - допустимое значение макси- ,мальной величины модуля разности расчетной и эмпирической функций надежности..

Если неравенство (8) соблюдается, то итог проверки результатов ускоренных испытаний положительньй и статистическую функцию распределения сопротивляемости Рл(х) можно использовать для прогноза надежности исследуемого технического объекта при эксплуатационных нагрузкахо В формуле (1) вместо параметра, характеризующего форсированную нагрузку (F(x.) ) подставляется условная функция распределения при эксплуатационной нагрузке „

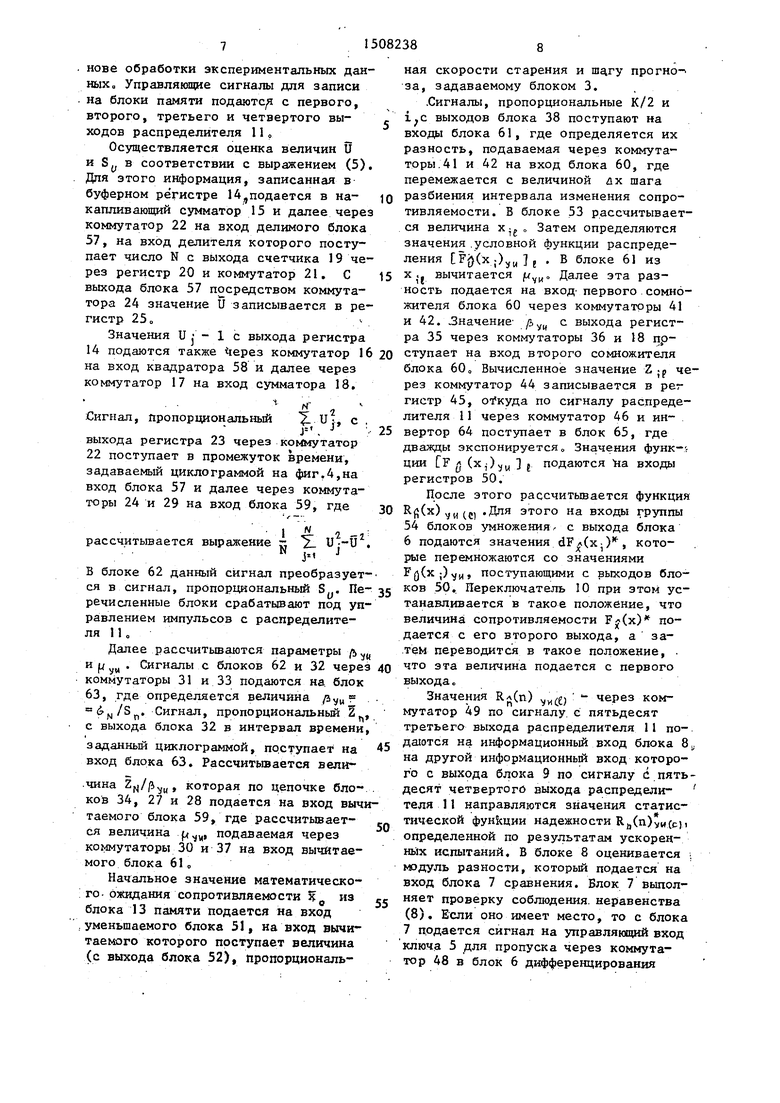

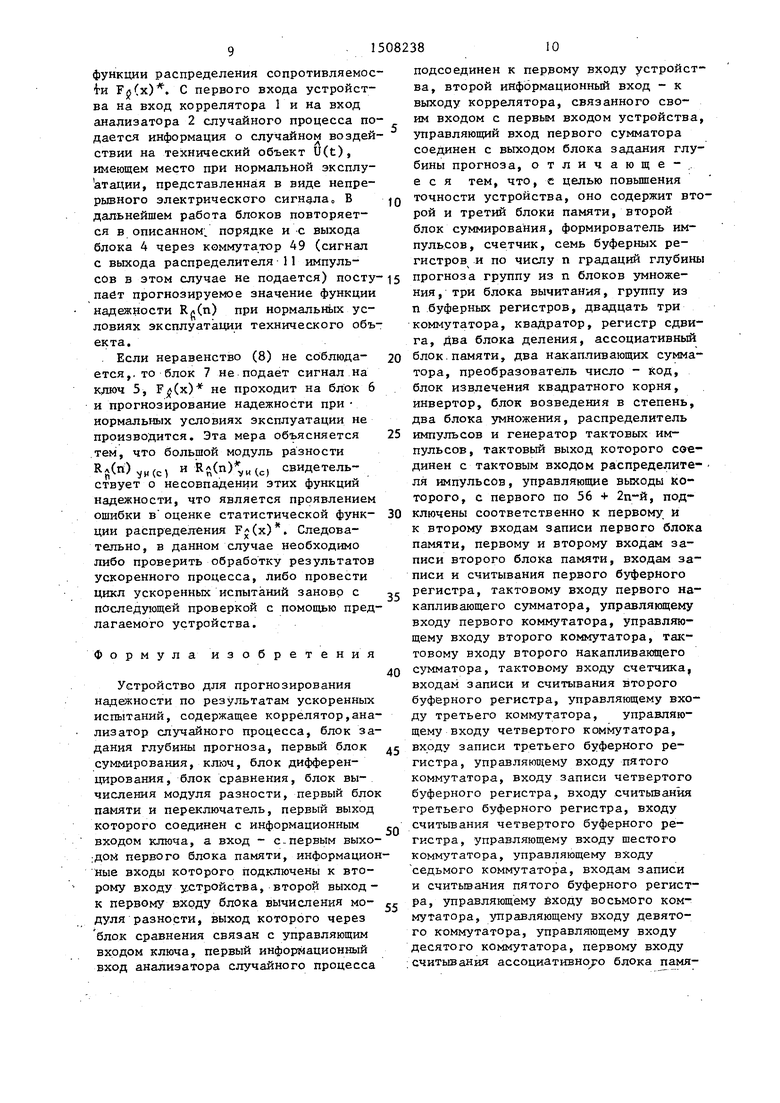

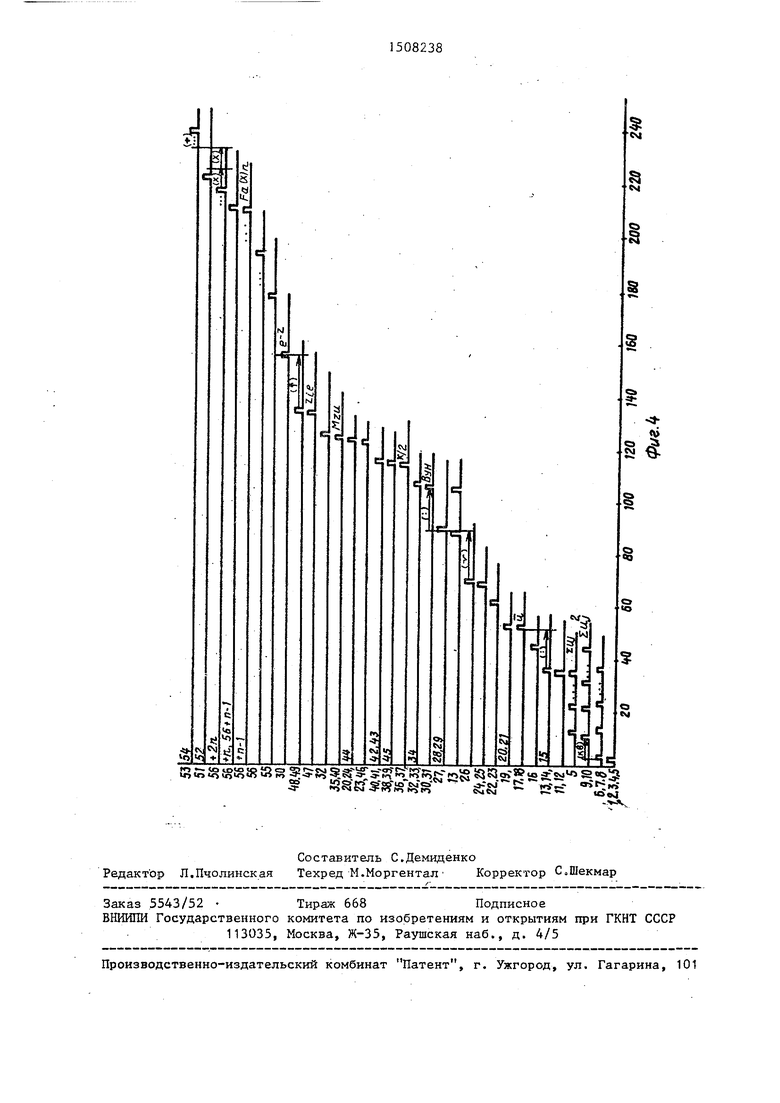

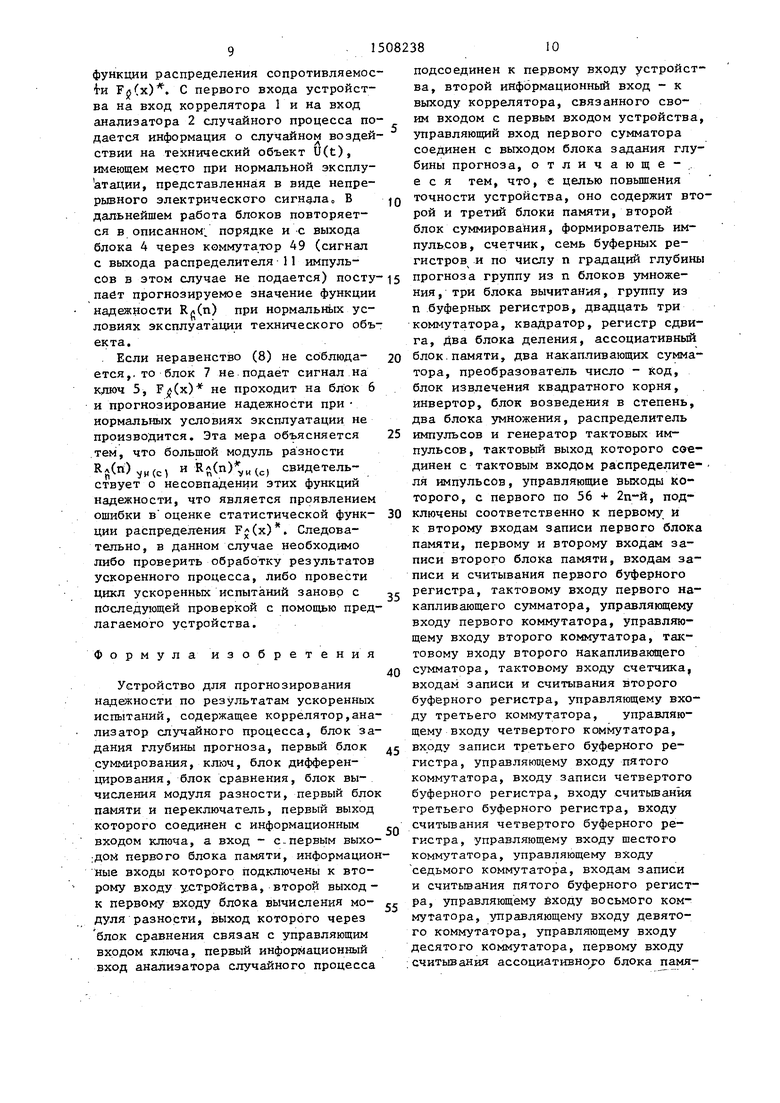

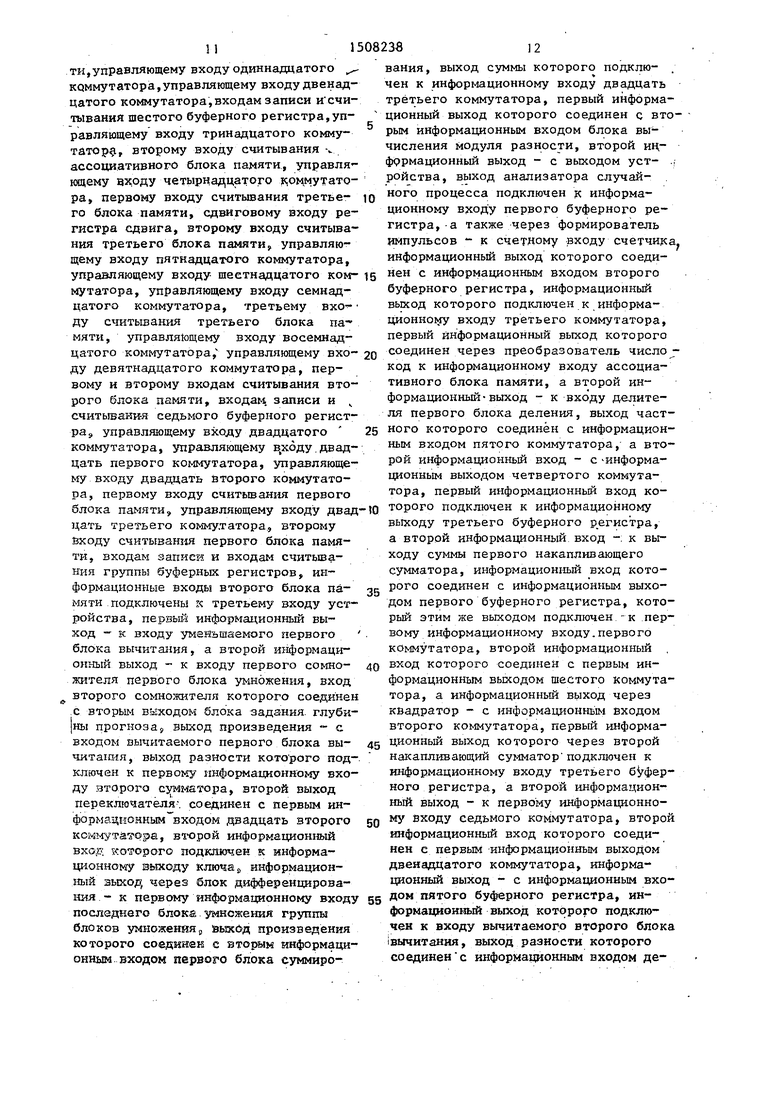

На фиг.1-3 приведена схема устройства; на фиГо4 - циклограмма его работы.

Устройство содержит коррелятор 1, анализатор 2 случайного процесса, блок 3 задания глубины прогноза,первый блок 4 суммирования, ключ 5, блок 6 дифференцирования, блок 7 сравнения, блок 8 вычисления модуля разности, первый блок 9 памяти, переклю- .чатель 10, распределитель 11 импульсов, генератор 12 тактовых импульсов второй блок 13 памяти, первый буферный регистр 14,-первый накапливающий сумматор 15,первый 16и второй 17 коммутаторы, второй накапливающий сумматор 18, счетчик 19, второй : буферный регистр 20, третий 21 и четвертый 22 коммутаторы, третий буферный регистр 23, пятый коммутатор 24, четвертый буферный регистр 25, щес- той 26 и седьмой 27 коммутаторы, пя- тьй буферный регистр 28, восьмой 29, девятый 30 и десятый 31 коммутаторы, ассоциативный блок 32 памяти, одиннадцатый 33 и двенадцатый 34 комму- таторы, шестой буферный регистр 35,

082386

тринадцатый 36 и четьфнадцатый 37 коммутаторы, третий блок 38 памяти, регистр 39 сдвига с пятнадцатого по. девятнадцатый коммутаторы 40. - 44, седьмой буферный регистр 45, коммутаторы с двадцатого по двадцать третий 46 - 49, группу 50 буферных регистров, первый блок 51 вычитания,

,Q первый блок 52 умножения, второй блок 53 суммирования, группу 54 блоков умножения, формирователь 55 импульсов, преобразователь 56 число - код,, первьш блок 57 деления, квадратор 58,

5 второй блок 59 вычитания, второй блок 60 умножения, третий блок 61 вычитания, блок 62 извлечения квадратного корня, второй блок 63 деления, инвертор 64 и блок 65 возведения в степень.

20 Позициями 66 - 121 обозначены вы- ходы распределителя И импульсов.

Устройство работает следующим образом.

Информация о форсированном случай25 ном воздействии на исследуемый технический объект и (t)yM имеющем место при ускоренных испытаниях, представленная в виде непрерьшного электрического сигнала, -поступает на вход

30 коррелятора 1 и на вход анализатора 2. В корреляторе 1 определяется автокорреляционная функция исследуемого случайного сигнала и по ней оценивается его интервал корреляции 411 . Этот интервал задается анализатору 2, в котором исследуемый сигнал разбивается на промежутки A S , и затем в каждом из них определяется наибольшее значение Выбранные наибольшие

0 значения Uj из интервалов разбиения исследуемого случайного сигнала подаются на информационный вход буферного регистра 14 (сигнал на запись подается на его управляющий вход с

5 пятого выхода распределителя И,темп работы которого задается генератором 12) и на вход формирователя 55, Таким образом, на информационный вход счетчика 19 поступает число импульQ сов, соответствующее количеству наибольших некоррелированных значений . U;. Кроме того, на информационные входы блока 9 с второго входа устройства подаются статистические знаg чения Гл(х) и R(n), полученные по результатам ускоренных испытаний На информационные входы блока 13 с третьего входа устройства поступают значения х „ и т, определенные на ос35

нове обработки экспериментальных данных. Управляющие сигналы для записи на блоки памяти подазотс с первого, второго, третьего и четвертого вы- ходов распределителя 11

Осуществляется оценка величин U и Sy в соответствии с выражением (5). Для этого информация, записанная в буферном регистре 14,подается в на- кашшвающий сумматор 15 и далее через коммутатор 22 на вход делимого блока 57, на вход делителя которого поступает число N с выхода счетчика 19 через регистр 20 и коммутатор 21. С выхода блока 57 посредством коммутатора 24 значение U записывается в регистр 25 о

Значения U j - 1 с выхода регистра 14 подаются также 1ерез коммутатор 16 на вход квадратора 58 и далее через коммутатор 17 на вход сумматора 18.

2

Сигнал, пропорциональный 2. U:, с .

Р. выхода регистра 23 через коммутатор

22 поступает в промежуток времени, задаваемый циклограммой на фиг.4,на вход блока 57 и далее через коммута торы 24 и 29 на вход блока 59, где

I

т ffi

рассчитьтается выражение :; U --U .

j

В блоке 62 данный сигнал преобразуется в сигнал, пропорциональный S . Пе- речисленные блоки срабатывают под управлением импульсов с распределителя 1 1 о

Далее рассчитываются параметры /ь,, и f . Сигналы с блоков 62 и 32 через коммутаторы 31 и 33 подаются на. блок 63, где определяется величина уц . . Сигнал, пропорциональньш 2, с выхода блока 32 в интервал времени,

заданный циклограммой, поступает на вход блока 63. Рассчитьшается величина которая по цепочке бло-. ков 34, 27 и 28 подается на вход вычитаемого блока 59, где рассчитывается величина , подаваемая через коммутаторы 30 и 37 на вход вычитаемого блока 61 о

Начальное значение математическо: го- ожидания сопротивляемости 5j из блока 13 памяти подается на вход

.уменьшаемого блока 51, на вход вычитаемого которого поступает величина (с выхода блока 52), пропорциональ

5

0

5

о

5

0

5

0

5

ная скорости старения и прогно- за, задаваемому блоком 3. ,

-Сигналы, пропорциональные К/2 и i.c выходов блока 38 поступают на входы блока 61, где определяется их разность, подаваемая через коммутаторы. 41 и 42 на вход блока 60, где перемежается с величиной дх шага разбиения интервала изменения сопротивляемости. В блоке 53 рассчитывается величина Х Затем определяются значения .условной функции распределения CFJ)(X ;),,1 J , в блоке 61 из X., вычитается /и, Далее эта разность подается на вход первого.сомножителя блока 60 через коммутаторы 41 и 42. Значение- /ь с выхода регистра 35 через коммутаторы 36 и 18 пр- ступает на вход второго сомножителя блока бОо Вычисленное значение Z ;р через коммутатор 44 записывается в per гистр 45, откуда по сигналу распределителя 11 через коммутатор 46 и инвертор 64 поступает в блок 65, где дважды экспонируется о Значения функ-г ции CF л (х,-)/и 1 t подаются на входы регистров 50.

После этого рассчитьшается функция ) этого на входы группы 54 блоков умножения, с выхода блока

6подаются значения dFACx-), которые перемножаются со значениями Р(х;)у(4, поступающими с выходов блоков 50. Переключатель 10 при этом устанавливается в такое положение, что величина сопротивляемости F(x) подается с его второго выхода, а за- .тем переводится в такое положение, . что эта величина подается с первого выхода.

Значения Кл(п) через коммутатор 49 по сигналу, с пятьдесят третьего выхода распределителя 11 по-. даются на информационный вход блока 8„ на другой информационньй вход которого с выхода блока 9 по сигналу с пятьдесят четвертого выхода распредели- теля 11 направляются значения статистической фyнkции надежности Rj,(n)vM(c)i определенной по результатам ускоренных испытаний. В блоке 8 оценивается ; модуль разности, которьй подается на вход блока 7 сравнения. Блок 7 выполняет проверку соблюдения, неравенства (8). Если оно имеет место, то с блока

7подается сигнал на управляющий вход ключ.а 5 для пропуска через коммутатор 48 в блок 6 дифференцирования

функции распределения сопротивляемос- -и Fjj(x) . С первого входа устройства на вход коррелятора 1 и на вход анализатора 2 случайного процесса подается информация о случайном воздействии на технический объект U(t), имеющем место при нормальной эксплу- атации, представленная в виде непрерывного электрического сигнала В дальнейшем работа блоков повторяется в описанном, порядке и с выхода блока 4 через коммутатор 49 (сигнал с выхода распределителя 11 импульсов в этом случае не подается) посту- 5 прогноза группу из п блоков умноже- пайт прогнозируемое значение функции надежности Кл(п) при нормапьньсх условиях эксплуатации технического объекта.

. Если неравенство (8) не соблюда- 20 ется,. то блок 7 не подает сигнал на ключ 5, FA(X) не проходит на блок 6 и прогнозирование надежности при нормальных условиях эксплуатации не производится. Эта мера объясняется 25 .тем, что большой модуль разности

fi(VM(c) и R(n) v(c) свидетельствует о несовпадении этих функций надежности, что является проявлением ошибки в оценке статистической функ- 30 ции распределения Fjj(x). Следовательно, в данном случае необходимо либо проверить обработку результатов ускоренного процесса, либо провести цикл ускоренных испытаний заново с

35

ния, три блока вычитания, группу из п буферных регистров, двадцать три коммутатора, квадратор, регистр сдви га, два блока деления, ассоциативный блок.памяти, два накапливающих сумма тора, преобразователь число - код, блок извлечения квадратного корня, инвертор, блок возведения в степень, два блока умножения, распределитель импульсов и генератор тактовых импульсов, тактовьА выход которого сое динен с тактовым входом распределите ля импульсов, управляющие выходы которого, с первого по 56 + 2п-й, подключены соответственно к первому и к второму входам записи первого блок памяти, первому и второму входам записи второго блока памяти, входам за писи и считывания первого буферного регистра, тактовому входу первого на капливающего сумматора, управляющему входу первого коммутатора, управляющему входу второго коммутатора, тактовому входу второго накапливающего сумматора, тактовому входу счетчика, входам записи и считывания второго буферного регистра, управляющему входу третьего коммутатора, управляющему входу четвертого коммутатора, входу записи третьего буферного регистра, управляющему входу пятого коммутатора, входу записи четвертого буферного регистра, входу считьюания третьего буферного регистра, входу считывания четвертого буферного регистра, управляющему входу шестого коммутатора, управляющему входу седьмого коммутатора, входам записи и считывания пятого буферного регистра, управляющему входу восьмого коммутатора, управляющему входу девятого коммутатора, управляющему входу десятого коммутатора, первому входу считывания ассоциативного блока памя

последующей проверкой с помощью предлагаемого устройства.

Формула изобретения

Устройство для прогнозирования

надежности по результатам ускоренных исгытаний, содержащее коррелятор,анализатор случайного процесса, блок задания глубины прогноза, первьй блок суммирования, ключ, блок дифференцирования, блок сравнения, блок вычисления модуля разности, первый блок памяти и переключатель, первый выход которого соединен с информационньм входом ключа, а вход - с-первым выхо- ;дом первого блока памяти, информационные входы которого подключены к второму входу устройства, второй выход- к первому входу блока вычисления мо- дуля разности, выход которого через блок сравнения связан с управляющим входом ключа, первый информационный вход анализатора случайного процесса

подсоединен к первому входу устройства, второй информационный вход - к выходу коррелятора, связанного своим входом с первым входом устройства, управляющий вход первого сумматора соединен с выходом блока задания глубины прогноза, отличающе-,. вся тем, что, с целью повьшения точности устройства, оно содержит второй и третий блоки памяти, второй блок суммирования, формирователь импульсов, счетчик, семь буферных регистров и по числу п градаций глубины

5 прогноза группу из п блоков умноже-

0 5

0

5

0

g

ния, три блока вычитания, группу из п буферных регистров, двадцать три коммутатора, квадратор, регистр сдвига, два блока деления, ассоциативный блок.памяти, два накапливающих сумматора, преобразователь число - код, блок извлечения квадратного корня, инвертор, блок возведения в степень, два блока умножения, распределитель импульсов и генератор тактовых импульсов, тактовьА выход которого соединен с тактовым входом распределите- ля импульсов, управляющие выходы которого, с первого по 56 + 2п-й, подключены соответственно к первому и к второму входам записи первого блока памяти, первому и второму входам записи второго блока памяти, входам записи и считывания первого буферного регистра, тактовому входу первого накапливающего сумматора, управляющему входу первого коммутатора, управляющему входу второго коммутатора, тактовому входу второго накапливающего сумматора, тактовому входу счетчика, входам записи и считывания второго буферного регистра, управляющему входу третьего коммутатора, управляющему входу четвертого коммутатора, входу записи третьего буферного регистра, управляющему входу пятого коммутатора, входу записи четвертого буферного регистра, входу считьюания третьего буферного регистра, входу считывания четвертого буферного регистра, управляющему входу шестого коммутатора, управляющему входу седьмого коммутатора, входам записи и считывания пятого буферного регистра, управляющему входу восьмого коммутатора, управляющему входу девятого коммутатора, управляющему входу десятого коммутатора, первому входу считывания ассоциативного блока памяти,управляющему входу одиннадцатого коммутатора,управляющему входу двенадцатого коммутатора,входам записи и счи- тывания шестого буферного регистра,управляющему входу тринадцатого коммутатору, второму входу считывания v ассоциативного блока памяти, управляющему входу четырнадцатого к;оимутато- ра, первому входу считьшания третье- ш го блока памяти, сдвиговому входу регистра сдвига, второму входу считывания третьего блока памяти, управляющему входу пятнадцатого коммутатора, управляющему входу шестнадцатого ком- 15 мутатора, управляющему входу семнадцатого коммутатора, третьему вхо- ду считьшания третьего блока памяти, управляющему входу восемнадцатого коммутатора, управляющему вхо- 20 ду девятнадцатого коммутатора, первому и второму входам считывания второго блока памяти, входам, записи и считывания седьмого буферного регистра., управляющему входу двадцатого 25 коммутатора, управляющему в,х6ду.двад-: цатБ первого коммутатора, управляющему входу дваддать йторого коммутатора, первому входу считывания первого

вания, выход суммы которого подключен к информационному входу двадцат третьего коммутатора, первый информ ционный выход которого соединен Q в рым информационным входом блока вычисления модуля разности, второй иц фррмационный выход - с выходом устройства, выход анализатора случай- ного процесса подключен к информационному ВХОДУ первого буферного ре гистра, -а также через формирователь импульсов - к счетному входу счетчи информационный выход которого соеди нен с информационным входом второго буферного регистра, информационный вьрсод которого подключен к информационному входу третьего коммутатора первый информационный выход которог соединен через преобразователь числ код к информационному входу ассоциа тивного блока памяти, а второй информационный- выход - к входу делите ля первого блока деления, выход час ного которого соединён с информацио ным входом пятого коммутатора, а вт рой информационный вход - с -информа ционным выходом четвертого коммутатора, первый информационный вход ко

блока памяти, управляющему входу двад-Ю торого подключен к информационному

выходу третьего буферного р егистра, а второй информационный вход -: к вы ходу суммы первого накапливающего сумматора, информацион1С)1й вход кото рого соединен с информационным выхо дом первого буферного регистра, кот рый этим же выходом подключен - к пе вому информационному входу.первого коммутатора, второй информационный вход которого соединем с первым информационным выходом шестого коммут тора, а информационный выход через квадратор - с информационным входом второго коммутатора, первый информа ционный выход которого через второй накапливающий сумматор подключен к информационному входу третьего ного регистра, а второй информацион ный выход - к первому информационно му входу седьмого коммутатора, втор информационный вход которого соединен с первым информационным выходом двенадцатого коммутатора, информационный выход - с информационным вх сс дом пятого буферного регистра, информационный выход которого подключен к входу вычитаемого второго бло 1вычитания, выход разности которого соединен с информационным входом де

цать третьего комму.татора, второму бходу считывания первого блока памяти, входам записи и входам считьюа- ния группь5 буферных регистров, информационные входы второго блока памяти .подключены к третьему входу устройства, первь5Й информационный выход - к входу уменьшаемого первого блока вычитания, а второй информационный выход - к входу первого co fflo- жителя первого блока умножения, вход второго сомножителя которого соединен .с вторым выходом блока задания, глуби- |ны прогноза выход произведения с входом вычитаемого первого блока вы- чита1шя, выход разности кото рого подключен к первому информационному входу .viTOporo сенатора, второй выход переключателя-, соединен с первым ин- формацнонным входом двадцать второго ксммутй уора, второй: информационный вход которого подключен к информационному выходу КЛЮЧИ;, информационный зыход через блок дифференцирования - к первому информационному входу последнего блока.умножения группы блоков умножения, аыхбд произведения которого соединен с вторым информационным входом первого блока суммирования, выход суммы которого подклю . чен к информационному входу двадцать третьего коммутатора, первый информационный выход которого соединен Q вторым информационным входом блока вычисления модуля разности, второй иц- фррмационный выход - с выходом уст ., ройства, выход анализатора случай- . ного процесса подключен к информационному ВХОДУ первого буферного регистра, -а также через формирователь импульсов - к счетному входу счетчика информационный выход которого соединен с информационным входом второго буферного регистра, информационный вьрсод которого подключен к информационному входу третьего коммутатора, первый информационный выход которого соединен через преобразователь числоj- код к информационному входу ассоциативного блока памяти, а второй информационный- выход - к входу делителя первого блока деления, выход частного которого соединён с информационным входом пятого коммутатора, а второй информационный вход - с -информационным выходом четвертого коммутатора, первый информационный вход которого подключен к информационному

выходу третьего буферного р егистра, а второй информационный вход -: к выходу суммы первого накапливающего сумматора, информацион1С)1й вход которого соединен с информационным выходом первого буферного регистра, который этим же выходом подключен - к первому информационному входу.первого коммутатора, второй информационный , вход которого соединем с первым информационным выходом шестого коммутатора, а информационный выход через квадратор - с информационным входом второго коммутатора, первый информационный выход которого через второй накапливающий сумматор подключен к информационному входу третьего ного регистра, а второй информационный выход - к первому информационному входу седьмого коммутатора, второй информационный вход которого соединен с первым информационным выходом двенадцатого коммутатора, информационный выход - с информационным вхо- дом пятого буферного регистра, информационный выход которого подключен к входу вычитаемого второго блока 1вычитания, выход разности которого соединен с информационным входом де

13

вятого коммутатора, а вход уменьшаемого - с информационным выходом восьмого коммутатора, первый информационный вход которого подключен к второму информационному выходу шестого комму- татора, а второй информационный вход к первому информационному выходу пятого коммутатора, второй информационный выход которого подключен к инфор- мационному входу четвертого буферного регистра, информационный выход которого соединен с вторым информационным входом шестого коммутатора, выход суммы второго блока суммирования подключен к первому информацион- ному входу пятнадцатого коммутатора, а второй информационный вход - к первому информационному выходу девятнадцатого коммутатора, второй информационный выход которого соединен с информационным входом седьмого буферного регистра, а информационньвн вход - с выходом произведения второго

блока умножения, входы первого и вто- 25 коммутатора, первый информационный

рого сомножителей которого подключены к информационным выходам соответственно семнадцатого и восемнадцатого коммутаторов, первые информационные входы которых подключены соответственно к первым информационным выходам тринадцатого коммутатора и третьего блока: памяти, а вторые информационные входы - соответственно к первому и второму информационным выходам шестнадцатого коммутатора, информационный вход которого соединен с выходом разности третьего блока вычитания, входы вычитаемого и уменьшаемого которого подключены к информационным выходам соответственно че- тьфнадцатого и пятнадцатого коммута- . торов, второй информационный вход последнего из которых через регистр

вход двадцатого коммутатора подключ к информационному выходу седьмого б ферного регистра, вто.рой информацио ньш вход - к первому информационном

30 выходу двадцать первого коммутатора а информационный выход через послед вательно соединенные инвертор и бло возведения в степень - к информационному входу двадцать первого ком

35 мутатора, второй информационный вых которого соединен с информационными входами группы буферных регистров,и формационные выходы двух первых буф ньпс регистров которой подключены к

40 входам соответственно первого и второго сомножителей первого блока умножения группы.блоков умножения, информационные выходы остальньк буферных- регистрюв - к входам первого сом

40 входам соответственно первого и второго сомножителей первого блока умножения группы.блоков умножения, информационные выходы остальньк буферных- регистрюв - к входам первого сомсдвига соединен с вторым информацион- 45 ножителя соответствующих последукицих

ным выходом третьего блока памяти, третий информационный выход .которого подключен к первому информационному входу четырнадца тог О коммутатора, : второй информационный вход которого соединен с первым информационным выблоков группы блоков умножения, входы второго сомножителя каждого последу- кщего из которых соединены с выходами произведения каждого из предьщущих 50 блоков умножения.

238I i

ходом девятого коммутатора, второй информационный выход которого через блок извлечения квадратного корня подключен к первому информационному входу десятого коммутатора, второй информационный вход которого соединен с вторым информационным выходом тринадцатого коммутатора, информационный выход - с входом делителя второго блока деления, выход частного которого подключен к информационному входу двенадцатого коммутатора,вход делимого - к информационному выходу одиннадцатого коммутатора, первый и второй информационные входы которого соединены соответственно с первым и вторым информационными выходами ассоциативного блока памяти, второй ин- формац:ронный выход двенадцатого коммутатора подключен к информационному входу шестого буферного регистра,информационный выход которого соединен с информационным входом тринадцатого

вход двадцатого коммутатора подключен к информационному выходу седьмого буферного регистра, вто.рой информацион- ньш вход - к первому информационному

выходу двадцать первого коммутатора, а информационный выход через последовательно соединенные инвертор и блок возведения в степень - к информационному входу двадцать первого коммутатора, второй информационный выход которого соединен с информационными входами группы буферных регистров,ин- формационные выходы двух первых буфер- ньпс регистров которой подключены к

входам соответственно первого и второго сомножителей первого блока умножения группы.блоков умножения, информационные выходы остальньк буферных- регистрюв - к входам первого сомножителя соответствующих последукицих

блоков группы блоков умножения, входы второго сомножителя каждого последу- кщего из которых соединены с выходами произведения каждого из предьщущих блоков умножения.

Ъег

И GS«ef5 RK fcS5R SuftfeaiftS ef

tttttirtttTttftttfttM

Ф1(г,2

,

;гг л±1

т т м

пв

«7

г;б

W flj

т -

t;

ш

)9J W

т т т т

1М 1ог

101

к

55

fcS5R SuftfeaiftS ef

S7 Ж

as §j вг я

| Устройство для прогнозирования надежности | 1975 |

|

SU559198A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-09-15—Публикация

1987-12-14—Подача