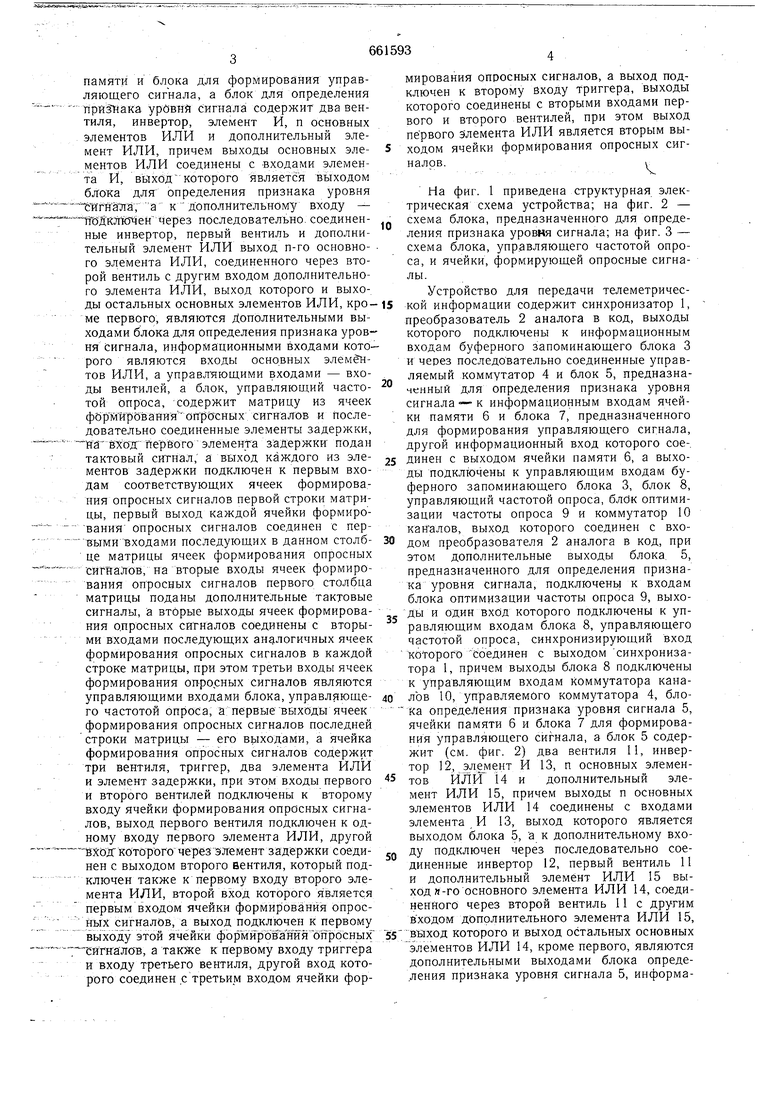

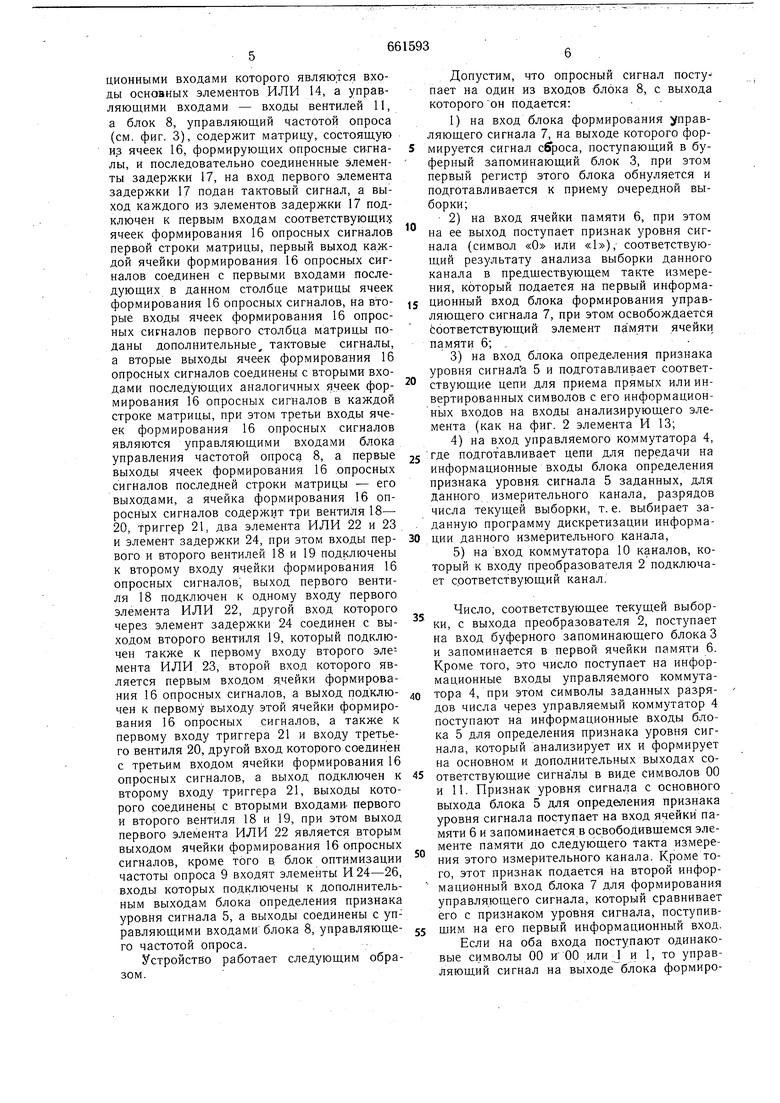

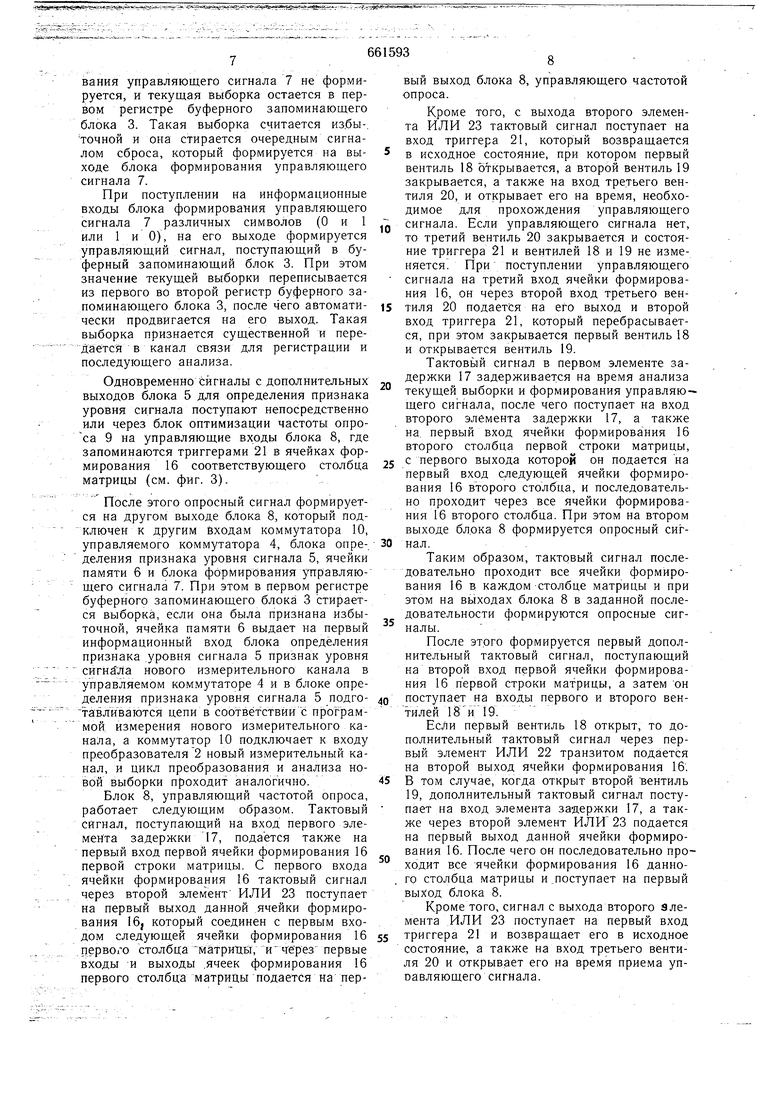

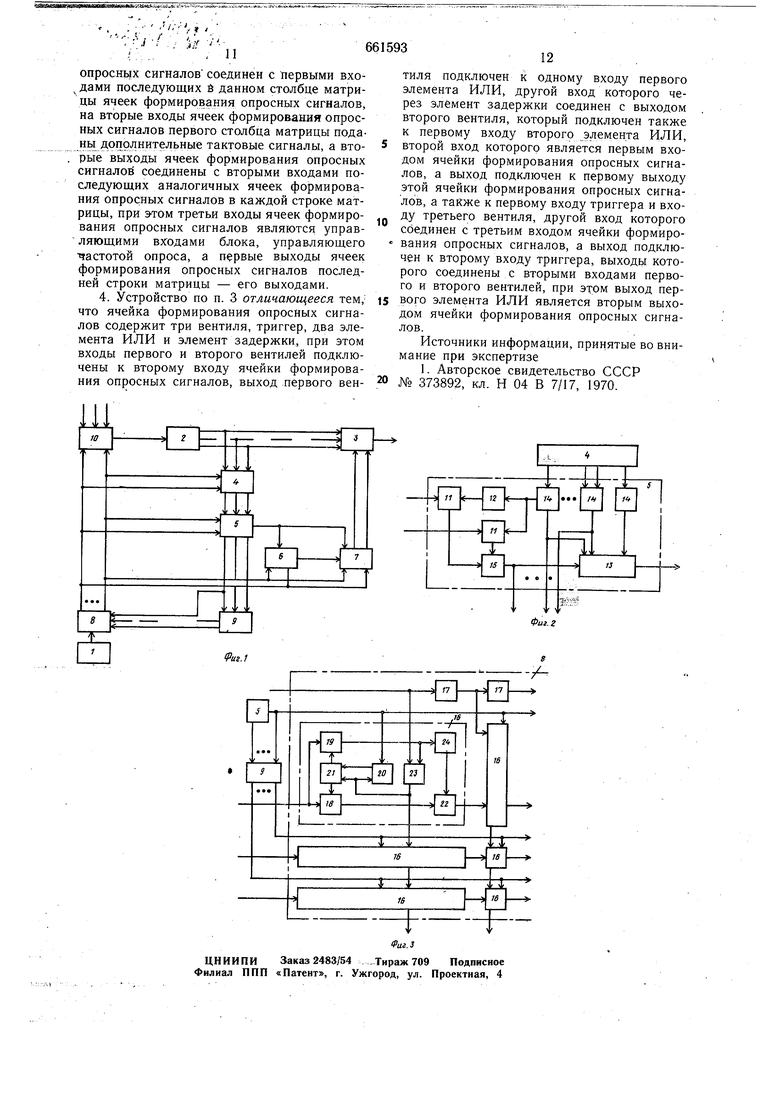

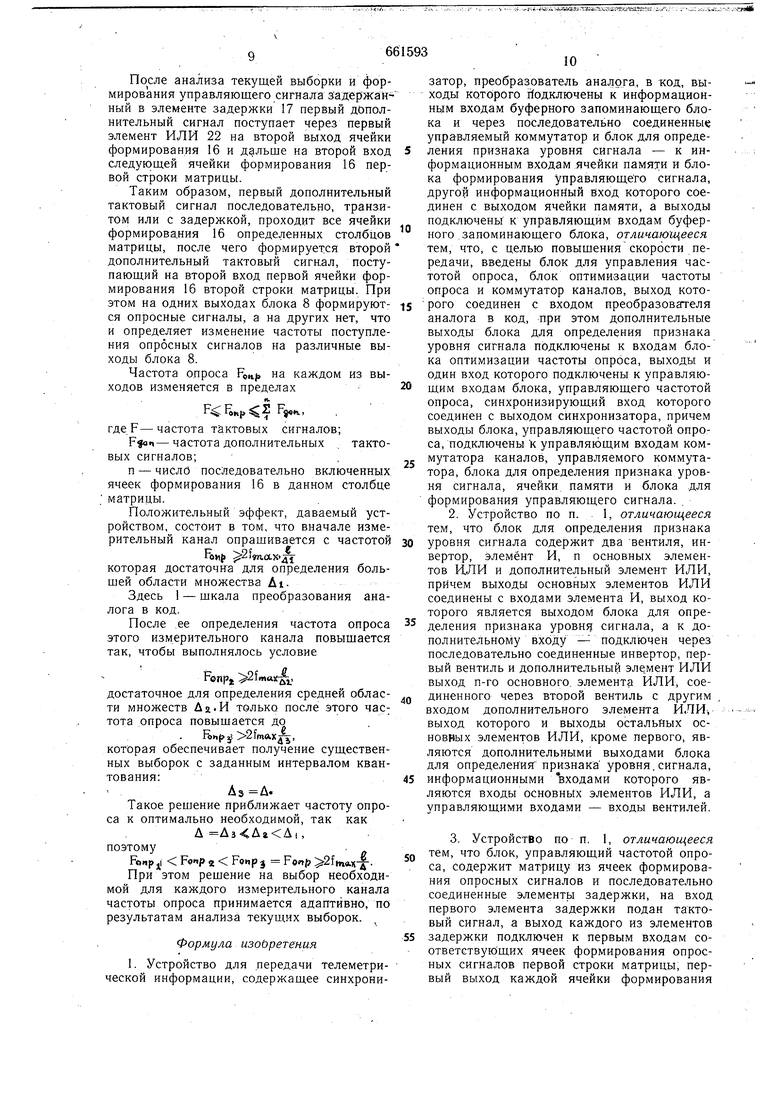

памяти и блока для формирования управляющего сигнала, а блок для определения Признака уровни сигнала содержит два вентиля, инвертор, элемент И, п основных элементов ИЛИ и дополнительный элемент ИЛИ, причем выходы основных элементов ИЛИ соединены с -входами элемента И, ВЫХОД которого является выходом блока для определения признака уровня ТйТнатта, а кДополнительному входу - TTolKAltotieH Через последовательно, соединенные инвертор, первый вентиль и дополнительный элемент ИЛИ выход п-го основного элемента ИЛИ, соединенного через второй вентиль с другим входом дополнительного элемента ИЛИ, выход которого и выхо- ды остальных основных элементов ИЛИ, кроме первого, являются Дополнительными выходами блока для определения признака уровня сигнала, информационными входами которого являются входы основных элементов ИЛИ, а управляющими входами - входы вентилей, а блок, управляющий частотой опроса, содержит матрицу из ячеек формирования опрасных сигналов и последовательно соединенные элементы задержки, первого элемента задержки подан тактовый сигнал, а выход каждого из элементов задержки подключен к первым входам соответствующих ячеек формирования опросных сигналов первой строки матрицы, первый выход каждой ячейки формиро вания опросных сигналов соединен с пер выми входами последующих в данном столбце матрицы ячеек формирования опросных сигналов, на вторые входы ячеек формирования опросных сигналов первого столбца матрицы поданы дополнительные тактовые сигналы, а вторые выходы ячеек формирования опросных сигналов соединены с вторыми входами последующих аналогичных ячеек формирования опросных сигналов в каждой строке матрицы, при этом третьи входы ячеек формирования оп-ро,сных сигналов являются управляющими входами блока, управляющего частотой опроса, а первые выходы ячеек формирования опросных сигналов последней строки матрицы - его вь1ходами, а ячейка формирования опросных сигналов содержит три вентиля, триггер, два элемента ИЛИ и элемент задержки, при этом входы первого и второго вентилей подключены к второму входу ячейки формирования опросных сигналов, выход первого вентиля подключен к одному входу первого элемента ИЛИ, другой Ёхйд которого черезэл емент задержки соединен с выходом второго вентиля, который подключен также к первому входу второго элемента ИЛИ, второй вход которого я вляется первым входом ячейки формирования опросных сигналов, а выход подключен к первому выходу этой ячейки формйрования отТрбсных сигналов, а также к первому входу триггера и входу третьего вентиля, другой вход которого соединен с третьим входом ячейки формирования опросных сигналов, а выход подключен к второму входу триггера, выходы которого соединены с вторыми входами первого и второго вентилей, при этом выход первого элемента ИЛИ является вторым выходом ячейки формирования опросных сигналов., На фиг. 1 приведена структурная электрическая схема устройства; на фиг. 2 - схема блока, предназначенного для определения признака уровня сигнала; на фиг. 3 - схема блока, управляющего частотой опроса, и ячейки, формирующей опросные сигналы. Устройство для передачи телеметрической информации содержит синхронизатор 1, преобразователь 2 аналога в код, выходы которого подключены к информационным входам буферного запоминающего блока 3 и через последовательно соединенные управляемый коммутатор 4 и блок 5, предназначенный для определения признака уровня сигнала -к информационным входам ячейки памяти 6 и блока 7, предназначенного для формирования управляющего сигнала, другой информационный вход которого сое-, динен с выходом ячейки памяти 6, а выходы подключены к управляющим входам буферного запоминающего блока 3, блок 8, управляющий частотой опроса, оптимизации частоты опроса 9 и коммутатор 10 каналов, выход которого соединен с входом преобразователя 2 аналога в код, при этом дополнительные выходы блока. 5, предназначенного для определения признака уровня сигнала, подключены к входам блока оптимизации частоты опроса 9, выходы и один вход которого подключены к управляющим входам блока 8, управляющего Частотой опроса, синхронизирующий вход которого Соединен с выходом синхронизатора 1, причем выходы блока 8 подключены к управляющим входам коммутатора каналов 10, управляембго коммутатора 4, блока определения признака уровня сигнала 5, ячейки памяти 6 и блока 7 для формирования управляющего сигнала, а блок 5 содержит (см. фиг. 2) два вентиля 11, инвертор 12, эл.емент И 13, п основных элементов ИЛИ 14 и дополнительный элемент ИЛИ 15, причем выходы п основных элементов ИЛИ 14 соединены с входами элемента , И 13, выход которого является выходом блока 5, а к дополнительному входу подключен через последовательно соединенные инвертор 12, первый вентиль 11 и дополнительный элемент ИЛИ 15 выход -го основного элемента ИЛИ 14, соединенного через второй вентиль 11 с другим входом дополнительного элемента ИЛИ 15, выход которого и выход остальных основных элементов ИЛИ 14, кроме первого, являются дополнительными выходами блока определения признака уровня сигнала 5, информационными входами которого являю.тся входы основных элементов ИЛИ 14, а управляющими входами - входы вентилей 11, а блок 8, управляющий частотой опроса (см. фиг. 3), содержит матрицу, состоящую из ячеек 16, формирующих опросные сигналы, и последовательно соединенные элементы задержки 17, на вход первого элемента задержки 17 подан тактовый сигнал, а выход каждого из элементов задержки 17 подключен к первым входам соответствующие ячеек формирования 16 опросных сигналов первой строки матрицы, первый выход каждой ячейки формирования 16 опросных сигналов соединен с первыми входами последующих в данном столбце матрицы ячеек формирования 16 опросных сигналов, на вторые входы ячеек формирования 16 опросных сигналов первого столбца матрицы поданы дополнительные, тактовые сигналы, а вторые выходы ячеек формирования 16 опросных сигналов соединены с вторыми входами последующих аналогичных ячеек формирования 16 опросных сигналов в каждой строке матрицы, при этом третьи входы ячеек формирования 16 опросных сигналов являются управляющими входами блока управления частотой опроса 8, а первые выходы ячеек формирования 16 опросных сигналов последней строки матрицы - его выходами, а ячейка формирования 16 опросных сигналов содержит три вентиля 18- 20, триггер 21, два элемента ИЛИ 22 и 23 и элемент задержки 24, при этом входы первого и второго вентилей 18 и 19 подключены к второму входу ячейки формирования 16 опросных сигналов; выход первого вентиля 18 подключен к одному входу первого элемента ИЛИ 22, другой вход которого через элемент задержки 24 соединен с выходом второго вентиля 19, который подключен также к первому входу второго элемента ИЛИ 23, второй вход которого является первым входом ячейки формирования 16 опросных сигналов, а выход подключен к первому выходу этой ячейки формирования 16 опросных сигналов, а также к первому входу триггера 21 и входу третьего вентиля 20, другой вход которого соединен с третьим входом ячейки формирования 16 опросных сигналов, а выход подключен к второму входу триггера 21, выходы которого соединены с вторыми входами- первого и второго вентиля 18 и 19, при этом выход первого элемента ИЛИ 22 является вторым выходом ячейки формирования 16 опросных сигналов, кроме того в блок оптимизации частоты опроса 9 входят элементы И 24-26, входы которых подключены к дополнительным выходам блока определения признака уровня сигнала 5, а выходы соединены с управляющими входами блока 8, управляющего частотой опроса.

Устройство работает следующим образом.

Допустим, что опросный сигнал поступает на один из входов блока 8, с выхода которого он подается:

1) на вход блока формирования управляющего сигнала 7, на выходе которого формируется сигнал сброса, поступающий в буферный запоминающий блок 3, при этом первый регистр этого блока обнуляется и подготавливается к приему очередной выборки;

2) на вход ячейки памяти 6, при этом на ее выход поступает признак уровня сигнала (символ «О или «1), соответствующий результату анализа выборки данного канала в предществующем такте измерения, который подается на первый информационный вход блока формирования управляющего сигнала 7, при этом освобождается Соответствующий элемент памяти ячейки памяти 6; ,

3)на вход блока определения признака уровня сигнала 5 и подготавливает соответствующие цепи для приема прямых или инвертированных символов с его информационных входов на входы анализирующего элемента (как на фиг. 2 элемента И 13;

4)на вход управляемого коммутатора 4, 5 где подготавливает цепи для передачи на

информационные входы блока определения

признака уровня, сигнала 5 заданных, для

данного, измерительного канала, разрядов

числа текущей выборки, т. е. выбирает за. данную программу дискретизации информа0 ции данного измерительного канала,

5)на вход коммутатора 10 каналов, который к входу преобразователя 2 подключает соответствующий канал.

Число, соответствующее текущей выборки, с выхода преобразователя 2, поступает на вход буферного запоминающего блока 3 и запоминается в первой ячейки памяти 6. Кроме того, это число поступает на информационные входы управляемого коммутатора 4, при этом символы заданных разрядов числа через управляемый коммутатор 4 поступают на информационные входы блока 5 для определения признака уровня сигнала, который анализирует их и формирует на основном и дополнительных выходах соответствующие сигналы в виде символов 00 и 11. Признак уровня сигнала с основного выхода блока 5 для определения признака уровня сигнала поступает на вход ячейки памяти 6 и запоминается в освобоДивщемся элементе памяти до следующего такта измерения этого измерительного канала. Кроме того, этот признак подается на второй информационный вход блока 7 для формирования управляющего сигнала, который сравнивает его с признаком уровня сигнала, поступившим на его первый информационный вход. Если на оба входа поступают одинаковые символы 00 И00 или J и 1, то управляющий сигнал на выходе блока формирования управляющего сигнала 7 не формируется, и текущая вь борка остается в первом регистре буферного запоминающего блока 3. Такая выборка считается избы-, точной и она стирается очередным сигналом сброса, который формируется на выходе блока формирования управляющего сигнала 7. При поступлении на информационные входы блока формирования управляющего сигнала 7 различных символов ( 1 или 1 и 0), на его выходе формируется управляющий сигнал, поступающий в буферный запоминающий блок 3. При этом значение текущей выборки переписывается из первого во второй регистр буферного запоминающего блока 3, после чего автоматически продвигается на его выход. Такая выборка признается существенной и передается в канал связи для регистрации и последующего анализа. Одновременно сигналы с дополнительных выходов блока 5 для определения признака уровня сигнала поступают непосредственно или через блок оптимизации частоты опро са 9 на управляющие входы блока 8, где запоминаются триггерами 21 в ячейках формирования 16 соответствующего столбца матрицы (см. фиг. 3). После этого опросный сигнал формируется на другом выходе блока 8, который подключен к другим входам коммутатора 10, управляемого коммутатора 4, блока опре-. деления признака уровня сигнала 5, ячейки памяти 6 и блока формирования управляю- щего сигнала 7. При этом в первом регистре буферного запоминающего блока 3 стирается выборка, если она была признана избыточной, ячейка памяти 6 выдает на первый информационный вход блока определения признака уровня сигнала 5 признак уровня сигнала нового измерительного канала в управляемом коммутаторе 4 и в блоке определения признака уровня сигнала 5 подго тавл ваются цепи в соответствии с программой измерения нового измерительного канала, а коммутатор 10 подключает к входу преобразователя 2 новый измерительный канал, и цикл преобразования и анализа новой выборки проходит аналогично. Блок 8, управляющий частотой опроса, работает следующим образом. Тактовый сигнал, поступающий на вход первого элемента задержки 17, подается также на первый вход первой ячейки формирования 16 первой строки матрицы. С первого входа ячейки формирования 16 тактовый сигнал через второй элемент ИЛИ 23 поступает на первый выход данной ячейки формирования 16, который соединен с первым входом следующей ячейки формирования 16 первого столбца матрицы, и через первые входы и выходы .ячеек формирования 16 первого столбца матрицы подается на пер661593ВЫЙ выход блока 8, управляющего частотой опроса. Кроме того, с выхода второго элемента ИЛИ 23 тактовый сигнал поступает на вход триггера 21, который возвращается в исходное состояние, при котором первый вентиль 18 открывается, а второй вентиль 19 закрывается, а также на вход третьего вентиля 20, и открывает его на время, необходимое для прохождения управляющего сигнала. Если управляющего сигнала нет, то третий вентиль 20 закрывается и состояние триггера 21 и вентилей 18 и 19 не изменяется. При поступлении управляющего сигнала на третий вход ячейки формирования 16, он через второй вход третьего вентиля 20 подается на его выход и второй вход триггера 21, который перебрасывается, при этом закрывается первый вентиль 18 и открывается вентиль 19. Тактовый сигнал в первом элементе задержки 17 задерживается на время анализа текущей выборки и формирования управляющего сигнала, после чего поступает на вход второго элемента задержки 17, а также на первый вход ячейки формирования 16 второго столбца первой строки матрицы, с первого выхода которой он подается на первый вход следующей ячейки формирования 16 второго столбца, и последовательно проходит через все ячейки формирования 16 второго столбца. При этом на втором выходе блока 8 формируется опросный сигнал. Таким образом, тактовый сигнал последовательно проходит все ячейки формирования 16 в каждом столбце матрицы и при этом на выходах блока 8 в заданной последовательности формируются опросные сигналы. После этого формируется первый дополнительный тактовый сигнал, поступающий на второй вход первой ячейки формирования 16 первой строки матрицы, а затем он поступает на входы первого и второго вентилей 18 и 19. Если первый вентиль 18 открыт, то дополнительный тактовый сигнал через первый элемент ИЛИ 22 транзитом подается на второй выход ячейки формирования 16. В том случае, когда открыт второй вентиль 19, дополнительный тактовый сигнал поступает на вход элемента задержки 17, а также через второй элемент ИЛИ 23 подается на первый выход данной ячейки формирования 16. После чего он последовательно проходит все ячейки формирования 16 данного столбца матрицы и .поступает на первый выход блока 8. Кроме того, сигнал с выхода второго элемента ИЛИ 23 поступает на первый вход триггера 21 и возвращает его в исходное состояние, а также на вход третьего вентиля 20 и открывает его на время приема упоавляющего сигнала. После анализа текущей выборки и формирования управляющего сигнала задержанный в элементе задержки 17 первый дополнительный сигнал поступает через первый элемент ИЛИ 22 на второй выход ячейки формирования 16 и на второй вход следук)щей ячейки формирования 16 первой строки матрицы. Таким образом, первый дополнительный тактовый сигнал последовательно, транзитом или с задержкой, проходит все ячейки формирования 16 определенных столбцов матрицы, после чего формируется второй дополнительный тактовый сигнал, поступающий на второй вход первой ячейки формирования 16 второй строки матрицы. При этом на одних выходах блока 8 формируются опросные сигналы, а на других нет, что и определяет изменение частоты поступления опросных сигналов на различные выходы блока 8. Частота опроса на каждом из выходов изменяется в пределах гдеF-частота тактовых сигналов; F n-частота дополнительных тактовых сигналов; п - число последовательно включенных ячеек формирования 16 в данном столбце матрицы. Положительный эффект, даваемый устройством, состоит в том, что вначале измерительный канал опращивается с частотой FOH .oi. которая достаточна для определения большей области множества At. Здесь 1 - щкала преобразования аналога в код. После ,ее определения частота опроса этого измерительного канала повыщается так, чтобы выполнялось условие Fonpj 2fmaifg, достаточное для определения средней области множеств Да.И только после этого час; тота опроса повышается до fiih( 2fmax, которая обеспечивает получение существенных выборок с заданным интервалом квантования:Лз-Д. Такое рещение приближает частоту опроса к оптимально необходимой, так как , поэтому Foflpji Fonp z FoMp j Fofit) 2frtja.-|-. При этом рещение на выбор необходимой для каждого измерительного канала частоты опроса принимается адаптивно, по результатам анализа текущих выборок. Формула изобретения 1. Устройство для передачи телеметрической информации, содержащее синхронизатор, преобразователь аналога, в код, выходы которого йодключены к информационным входам буферного запоминающего блока и через последовательно соединенные управляемый коммутатор и блок для определения признака уровня сигнала - к информационным входам ячейки памяти и блока формирования управляющего сигнала, другой информационный вход которого соединен с выходом ячейки памяти, а выходы подключены к управляющим входам буферного запоминающего блока, отличающееся тем, что, с целью повыщения скорости передачи, введены блок для управления частотой опроса, блок оптимизации частоты опроса и коммутатор каналов, выход которого соединен с входом преобразователя аналога в код, при этом дополнительные выходы блока для определения признака уровня сигнала подключены к входам блока оптимизации частоты опроса, выходы и один вход которого подключены к управляющим входам блока, управляющего частотой опроса, синхронизирующий вход которого соединен с выходом синхронизатора, причем выходы блока, управляющего частотой опроса, подключены к управляющим входам коммутатора каналов, управляемого коммутатора, блока для определения признака уровня сигнала, ячейки, памяти и блока для формирования управляющего сигнала. 2. Устройство по п. I, отличающееся тем, что блок для определения признака уровня сигнала содержит два вентиля, инвертор, элемент И, п основных элементов И.ЛИ и дополнительный элемент ИЛИ, причем выходы основных элементов ИЛИ соединены с входами элемента И, выход которого является выходом блока для определения признака уровня сигнала, а к дополнительному входу - подключен через последовательно соединенные инвертор, первый вентиль и дополнительный элемент ИЛИ выход п-го основного, элемента ИЛИ, соединенного чеоез ВТОРОЙ вентиль с другим входом дополнительного элемента ИЛИ-, выход которого и выходы остальйых основных элементов ИЛИ, кроме первого, являются дополнительными выходами блока для определения признака уровня.сигнала, информационными входами которого являются входы основных элементов ИЛИ, а управляющими входами - входы вентилей. 3. Устройство по п. I, отличающееся тем, что блок, управляющий частотой опроса, содержит матрицу из ячеек формирования опросных сигналов и последовательно соединенные элементь задержки, на вход первого элемента задержки подан тактовый сигнал, а выход каждого из элементов задержки подключен к первым входам соответствую щих ячеек формирования опросных сигналов первой строки матрицы, первый выход каждой ячейки формирования

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

| Устройство для передачи информации с адаптивной дискретизацией | 1976 |

|

SU608187A1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

| Генератор случайного процесса | 1983 |

|

SU1164705A1 |

| Устройство для проверки электрического монтажа | 1984 |

|

SU1259289A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| Устройство для сигнализации состояний объектов | 1988 |

|

SU1711213A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА С ДВУСЛОЙНОЙ ПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1998 |

|

RU2134448C1 |

Авторы

Даты

1979-05-05—Публикация

1976-03-23—Подача