Изобретение относится к области вычислительной техники и предназначено для создания высокоскоростных систем обработки больших потоков данных в реальном режиме времени.

Известна ячейка однородной вычислительной среды, содержащая арифметико-логический элемент, регистр команд, дешифратор, входы которого подключены к первой группе выходов регистра команд, три элемента задержки, три коммутатора входов и четыре коммутатора выходов, причем настроечные входы регистра команд соединены с настроечными входами вычислительной ячейки, программный выход регистра команд соединен с настроечным выходом вычислительной ячейки, первый управляющий выход регистра команд соединен с первым входом первого элемента задержки, второй вход которого подключен к выходу арифметико-логического элемента, управляющий вход которого соединен с выходом дешифратора, а первый и второй информационные входы подключены к выходам первого и второго коммутаторов входов, соединенных своими входами с четырьмя информационными входами вычислительной ячейки, управляющие входы коммутаторов входов соединены с третьим управляющим выходом регистра команд, выход первого элемента задержки соединен с первыми входами коммутаторов выходов, выходы которых подключены к выходам вычислительной ячейки, входы третьего коммутатора входа соединены с информационными входами вычислительной ячейки, выход третьего коммутатора входа соединен со входом второго элемента задержки, управляющий вход которого подключен к первому управляющему выходу регистра команд, а выход соединен со вторыми входами коммутаторов выхода и со входом третьего элемента задержки, выход которого соединен с третьими входами коммутаторов выходов, управляющие входы которых соединены с четвертым управляющим выходом регистра команд, а входы адресов управления вторым элементом задержки которого соединены с выходами адресов хранения констант [1].

Недостатком ее является сложность выполнения операций коммутации данных в потоках (сортировки, перестановки, вставки, удаления), которые встречаются в любой задаче обработки видео- и радиолокационных сигналов и в задачах линейной алгербы, т.е. в основных областях применения потоковых вычислительных систем, из-за чего много вычислительных ячеек занято выполнением операций коммутации, что приводит к значительному снижению производительности системы в целом.

Наиболее близкой к описываемому изобретению (прототип) является однородная вычислительная среда, содержащая матрицы вычислительных ячеек, соединенных двусторонними связями по вертикали и горизонтали, матрицу запоминающих ячеек, соединенных двусторонними связями по вертикали и горизонтали, причем вычислительные ячейки крайних строк и столбцов матрицы вычислительных ячеек соединены двухсторонними связями с запоминающими ячейками крайних строк и столбцов матрицы запоминающих ячеек, запоминающее устройство программ, первый вход которого соединен общей шиной со входами управления вводом программы всех ячеек, а группа вторых выходов которого соединена со входами программы ячеек матриц вычислительных и запоминающих ячеек, и генератор тактовых импульсов соединен общей шиной с тактовыми входами всех ячеек, при этом информационные входы крайних ячеек соединены с устройствами сопряжения, а программный выход каждой вычислительной ячейки в строке матрицы вычислительных ячеек связан с программным входом следующей вычислительной ячейки, и выход программы каждой запоминающей ячейки в строке матрицы запоминающих ячеек связан с программным входом следующей запоминающей ячейки, при этом каждая вычислительная ячейка содержит арифметико-логическое устройство, регистр команд и дешифратор кода операции, четыре элемента задержки, три схемы коммутации входов и три схемы коммутации выходов, причем входы дешифратора кода операции подключены к первой группе управляющих выходов регистра команд, а программные входы и программный выход регистра команд являются соответственно программными входами и выходом для вычислительной ячейки, управляющие входы арифметико-логического устройства соединены с первой группой выходов дешифратора кода операции, вторая группа выходов которого соединена с первым входом схемы управления транзитом и первым входом второй схемы управления расширенным транзитом, третий выход дешифратора кода операции связан с первым входом первой схемы управления расширенным транзитом, а четвертый выход дешифратора кода операции связан с первым входом схемы управления регистром команд, второй вход которого связан с первым информационным входом, а третий и четвертый входы схемы управления регистра команд связаны со второй и шестой группой выходов регистра команд, третья, четвертая и пятая группы выходов которого связаны соответственно с группой управляющих входов первой, второй и третьей схем коммутации входов, а шестая, седьмая и восьмая группы выходов регистра команд связаны соответственно с группой управляющих входов первой, второй и третьей схем коммутации выходов, причем информационные входы вычислительной ячейки являются входами для каждой из схем коммутации входов, выходы же схем коммутации выходов являются выходами вычислительной ячейки, а первой и второй информационные входы арифметико-логического устройства подключены соответственно к выходам первой и второй схем коммутации входов, которые также соответственно подключены к первым информационным входам первой и второй схем расширенного транзита, при этом второй информационный вход первой схемы расширенного транзита соединен с выходом арифметико-логического устройства, а второй информационный вход второй схемы расширенного транзита соединен с выходом третьего элемента задержки, вход которого соединен со схемой управления транзитом, второй управляющий вход которой соединен с первым выходом схемы управления регистром команд, второй выход которой соединен с информационным входом регистра команд, при этом выходы первой и второй схем расширенного транзита соединены соответственно со входами первого и четвертого элементов задержки, а выход первого элемента задержки соединен со входом второго элемента задержки и со вторым входом схемы управления дополнительной задержкой, первый вход которой соединен с выходом второго элемента задержки, а выход схемы управления дополнительной задержкой соединен со входом первой схемы коммутации входов, входы же второй и третьей схем коммутации выходов соответственно соединены с выходами третьего и четвертого элементов задержки, а выход третьей схемы коммутации входов соединен с третьим входом схемы управления транзитом, при этом каждая запоминающая ячейка содержит командный регистр, два входных и два выходных коммутатора, матрицу памяти, коммутатор матрицы памяти, схему управления транзитом и триггер задержки, причем входы входных коммутаторов являются информационными входами своей запоминающей ячейки, информационные выходы которой являются выходами выходных коммутаторов, причем выход первого входного коммутатора соединен с первым информационным входом коммутатора матрицы памяти, управляющий вход которого соединен с пятой группой выходов командного регистра, первая и вторая группы выходов которого соединены соответственно с управляющими входами первого и второго выходных коммутаторов, а третья и четвертая группы выходов командного регистра соединены соответственно с управляющими входами первого и второго выходных коммутаторов, причем выход второго входного коммутатора соединен со входом схемы управления транзитом, выход которой соединен со входом триггера задержки, выход которого соединен со входом второго выходного коммутатора, а вход и выход матрицы памяти соединены соответственно со вторыми информационными выходом и входом коммутатора матрицы памяти, первый информационный выход которого соединен со входом первого выходного коммутатора, а вход программы, вход сигнала управления ввода программы и выход программы командного регистра являются соответственно входом программы, входом сигнала управления ввода программы и выходом программы для запоминающей ячейки [2].

Недостатком ее является то, что при использовании запоминающих ячеек, расположенных не с края матрицы, доступ к ним от вычислительных ячеек затруднен, так как требуется передать данные через несколько ячеек. Кроме того, при выполнении операций коммутации требуются многочисленные переходы от матрицы вычислительных ячеек к матрице запоминающих ячеек и обратно, что связано с тем, что запоминающая ячейка предназначена для синхронизации потоков данных и не может выполнять какие-либо функции по коммутации данных. Таким образом большая часть ячеек занята непроизводительными операциями передачи данных. Реально эти недостатки выражаются в увеличении числа вычислительных и запоминающих ячеек, необходимых для решения задачи и в уменьшении быстродействия системы в целом.

Техническим результатом предлагаемого изобретения является увеличение быстродействия и упрощение выполнения операций коммутации данных.

Указанный результат достигается тем, что в известном устройстве введен блок управления, у которого первая и вторая группы выходов соединены соответственно с программными входами крайних ячеек матрицы вычислительных ячеек и входами программы матрицы запоминающих ячеек, а третий выход блока управления связан общей шиной со входами сигналов управления вводом программы всех вычислительных и запоминающих ячеек, при этом группа входов блока управления соединена с группой информационных выходов крайних ячеек матрицы вычислительных ячеек, а все запоминающие ячейки соединены двусторонними связями и соответствующими вычислительными ячейками, при этом в вычислительную ячейку введены четвертая схема коммутации входов, четвертая и пятая схемы коммутации выходов и сдвигающий параллельно-последовательный регистр, группа первых управляющих входов которого связана с группой выходов дешифратора кода операций, а группа вторых управляющих входов связана со второй группой выходов регистра команд, информационных вход сдвигающего параллельно-последовательного регистра связан с первым выходом арифметико-логического устройства, второй выход которого связан со входом третьего элемента задержки, группа параллельных информационных выходов сдвигающего параллельно-последовательного регистра связана с группой третьих информационных входов арифметико-логического устройства, а выход третьей схемы коммутации входов связан с четвертым информационным входом арифметико-логического устройства, причем последовательный информационный выход сдвигающего параллельно-последовательного регистра связан с информационным входом первого элемента задержки, выход которого соединен с первыми информационными входами схем коммутации выходов, при этом информационный вход второго элемента задержки связан с выходом четвертой схемы коммутации входов, а выход второго элемента задержки связан с третьими информационными входами всех схем коммутации выходов, вторые информационные входы которых связаны с выходом третьего элемента задержки, при этом управляющие входы первого, второго и третьего элементов задержки подключены ко второй группе выходов регистра команд, управляющие входы всех схем коммутации выходов соединены с четвертой группой выходов регистра команд, причем во всех схемах коммутации входов добавлен пятый информационный вход, который является информационным входом вычислительной ячейки, а управляющие входы всех схем коммутации входов подключены к третьей группе выходов регистра команд и число информационных входов и выходов вычислительной ячейки увеличено до пяти для связи с запоминающей ячейкой, в которую дополнительно введены сдвигающий регистр, два входных коммутатора, три выходных коммутатора, вентиль, и переключатель, первый информационный вход которого связан с выходом третьего входного коммутатора, второй информационный вход переключателя связан с выходом четвертого входного коммутатора, а управляющий вход переключателя связан с выходом второго входного коммутатора, при этом первый выход переключателя связан с информационным входом сдвигающего регистра, а второй выход переключателя связан с информационным входом триггера задержки, выход которого соединен с первыми информационными входами выходных коммутаторов, вторые информационные входы которых связаны с выходом сдвигающего регистра, группа первых управляющих входов которого связана с группой первых выходов командного регистра, второй управляющий вход сдвигающего регистра связан с выходом вентиля, второй вход которого связан с шиной тактовых импульсов, а первый вход - с выходом первого входного коммутатора, причем вторая группа выходов командного регистра с группой управляющих входов третьего входного коммутатора, четвертая группа выходов командного регистра связана с группой управляющих входов четвертого входного коммутатора, третья и пятая группы выходов командного регистра связаны соответственно с первыми и вторыми управляющими входами всех выходных коммутаторов, шестая группа выходов командного регистра связана с группой управляющих входов второго входного коммутатора, а седьмая группа выходов командного регистра связана с группой управляющих входов первого входного коммутатора.

На фиг. 1 представлена структурная схема соединения матриц вычислительных и запоминающих ячеек. На ней обозначены: 1 - устройство управления, 2 - вычислительная ячейка, 4 - генератор тактовых импульсов, 6, 7 - первая и вторая соответственно группы управляющих выходов устройства управления, 5 - третий выход устройства управления, 8 - группа входов устройства управления.

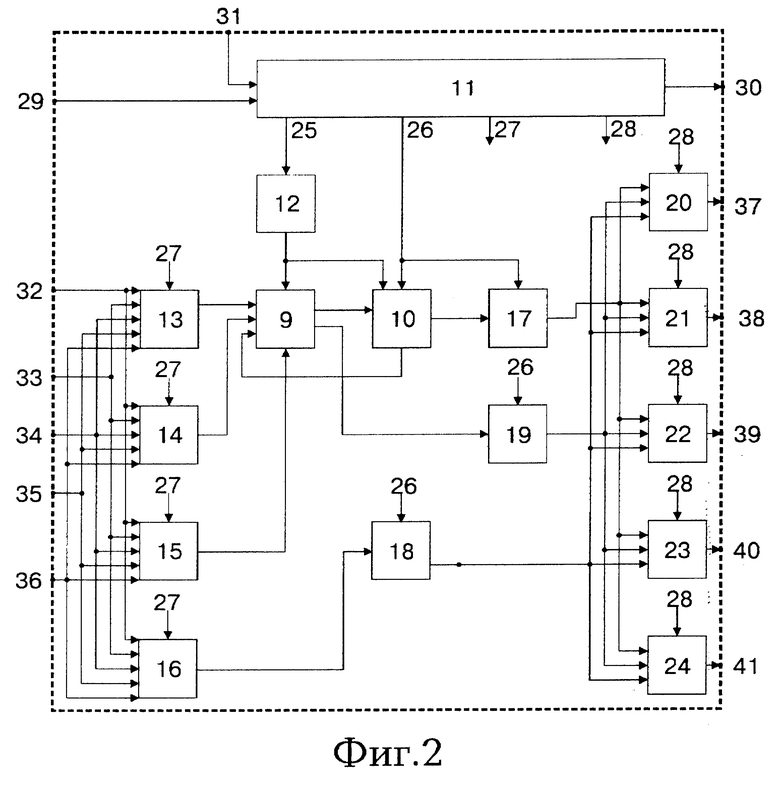

На фиг. 2 представлена структурная схема вычислительной ячейки. На ней обозначены: 9 - арифметико-логическое устройство, 10 - сдвигающий параллельно-последовательный регистр, 11 - регистр команд, 12 - дешифратор кода операций, 13, 14, 15, 16 - первая, вторая, третья и четвертая соответственно схемы коммутации входов, 17, 18, 19 - первый, второй и третий соответственно элементы задержки, 20, 21, 22, 23, 24 - первая, вторая, третья, четвертая и пятая соответственно схемы коммутации выходов, 25, 26, 27, 28 - первая, вторая, третья и четвертая соответственно группы управляющих выходов регистра команд, 29 - программный вход вычислительной ячейки, 30 - программный выход вычислительной ячейки, 31 - вход сигнала условия ввода программы, 32, 33, 34, 35, 36 - первый, второй, третий, четвертый и пятый соответственно входы вычислительной ячейки, 37, 38, 39, 40, 41 - первый, второй, третий, четвертый и пятый соответственно выходы вычислительной ячейки.

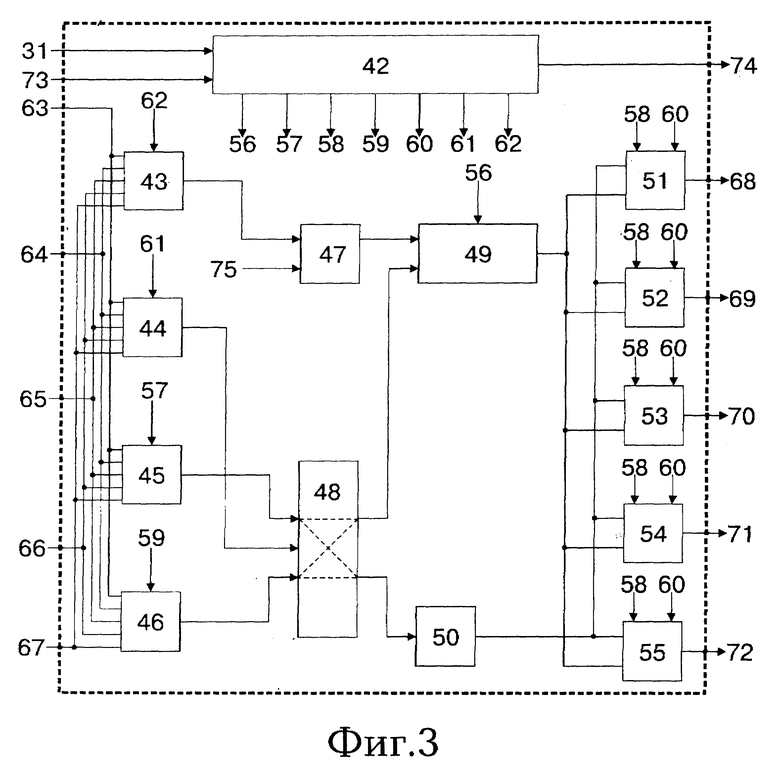

На фиг. 3 представлена структурная схема запоминающей ячейки. На ней обозначены: 42 - командный регистр, 43, 44, 45, 46 - первый, второй, третий и четвертый соответственно входные коммутаторы, 47 - вентиль, 48 - переключатель, 49 - сдвигающий регистр, 50 - триггер задержки, 51, 52, 53, 54, 55 - первый, второй, третий, четвертый и пятый соответственно выходные коммутаторы, 56, 57, 58, 59, 60, 61, 62 - первая, вторая, третья, четвертая, пятая, шестая и седьмая соответственно группы выходов командного регистра, 63, 64, 65, 66, 67 - первый, второй третий, четвертый и пятый соответственно входы запоминающей ячейки, 68, 69, 70, 71, 72 - первый, второй, третий, четвертый и пятый соответственно выходы запоминающей ячейки, 73 - вход программы запоминающей ячейки, 74 - выход программы запоминающей ячейки, 75 - вход тактовых импульсов.

Предлагаемое устройство работает следующим образом. Каждая задача состоит из множества шагов, представляющих собой законченные действия (процессы). Перед началом решения задачи в регистры команд каждой вычислительной 2 и командные регистры каждой запоминающей 3 ячейки с помощью устройства управления 1 производится запись команд программы корневого (первого) процесса, и каждый процесс как бы "раскладывается" по матрицам ячеек. Первая группа управляющих выходов 6 устройства управления 1 соединена с программными входами крайних в строке ячеек матрицы вычислительных ячеек 2. Вторая группа управляющих выходов 7 устройства управления также соединена с матрицей запоминающих ячеек 3. И при включении питания устройство управления 1 через третий выход 5 выдает через общую шину на входы сигнала условия ввода программы всех ячеек этот сигнал. По окончании этого сигнала начинается выполнение программы.

В дальнейшем каждая вычислительная 2 и запоминающая 3 ячейка выполняет свою команду до тех пор, не завершится очередной процесс. Тогда в ячейки могут быть записаны команды нового процесса. Причем выполнение нового процесса инициируется крайними ячейками матрицы вычислительных ячеек 3, выходы которых связаны с группой управляющих входов 8 устройства управления 1.

На время выполнения текущего процесса на однородной вычислительной структуре как бы организуется двухуровневый конвейер, с одного конца которого загружаются входные данные, а затем обрабатываются, передаваясь от ячейки к ячейке, и выгружаются с другого конца конвейера. Одновременно могут существовать несколько конвейеров, то есть загружаются несколько процессов, если они размещаются в матрице. Устройство управления может быть реализовано так, как это описано в RU N 2110088 C1, 27.04.98.

Матрицы вычислительных и запоминающих ячеек могут наращиваться для увеличения быстродействия и коммутационных возможностей системы. Все ячейки обеих матриц соединяются с общими шинами тактовых импульсов и с общими шинами сигнала управления ввода программы (на фиг. 1 разводка общих шин не показана, также не показаны связи регистров команд и командных регистров. Это подробно описано в [2]). Работа всех ячеек жестко синхронизирована тактовыми импульсами, на каждом такте ячейки получают по одному биту входных данных по каждому задействованному входу и отсылают по одному биту результата по каждому задействованному выходу. Тактовые импульсы синхронизируют работу всех схем входной и выходной коммутации, регистров и триггеров обычным образом, поэтому их разводка на фиг. 2 и 3 не показана.

Вычислительная ячейка 2 перед началом решения задачи получает команду в регистр команд 11. Код команды вводится через программный вход 29 вычислительной ячейки последовательно разряд за разрядом в регистр команд 11 по сигналу управления ввода программы, подаваемому на вход 31. Программный выход 30 обеспечивает возможность последовательного соединения регистров команд 11 вычислительных ячеек. При этом образуется единый сдвиговый регистр. Когда вся программа введена в матрицу, то по окончании сигнала управления ввода программы 31 в регистре команд 11 каждой ячейки находится свой код команды, и с этого момента времени вычислительная ячейка 2 переходит в режим выполнения программы. Обработка данных ведется последовательно разряд за разрядом младшими разрядами вперед.

Вычислительная ячейка 2 одновременно выполняет следующие функции: выполнение арифметико-логических операций, передача информации транзитом, без обработки.

Дешифратор кода операций 12 настраивает арифметико-логическое устройство 9 на выполнение заданной операции в соответствии с кодом операции, выдаваемым первой группой управляющих выходов 25 регистра команд. В систему команд могут быть включены любые арифметико-логические операции. В качестве примера можно привести следующую систему команд: "Логическое-И", "Логическое-И с инверсией", "Арифметическое сложение". "Сложение по модулю 2", "DT-триггер", "Умножение целого числа произвольной длины на число фиксированной длины".

В режиме "DT-триггера" второй информационный вход арифметико-логического устройства 9 является управляющим входом триггера, а первый информационный вход арифметико-логического устройства работает как информационный вход триггера, в то время как четвертый информационный вход арифметико-логического устройства обеспечивает его работу в режиме Т-триггера при выполнении этой операции.

"Умножение целого числа произвольной длины на число фиксированной длины". При выполнении этой операции множитель через первую схему коммутации входов 13 и через арифметико-логическое устройство 9 передается в сдвигающий параллельно-последовательный регистр 10, где запоминается. Одновременно через вторую схему коммутации входов 14 подается константа вида ...000111... 11111000. .., причем единицы поступают одновременно с множителем. Когда значение текущего разряда константы меняется с "1" на "0", арифметико-логическое устройство 9 начинает потоковое умножение множимого произвольной длины, поступающего вслед за множителем, на множитель, находящийся в сдвигающем параллельно-последовательном регистре 10. Умножение происходит до тех пор, пока значение текущего разряда константы не поменяется с "0" на "1". При этом выход данных из арифметико-логического устройства 9 идет через параллельно-последовательный регистр 10 транзитом, минуя цепи сдвига.

Система команд является логически полной и достаточной для реализации универсальной вычислительной системы, но для разных областей приложения она может быть дополнена другими командами.

Вторая группа управляющих выходов 26 регистра команд управляет задержкой выходных данных, так, информация с выхода арифметико-логического устройства 9 через первый элемент задержки 17 и сдвигающий параллельно-последовательный регистр 10, который также может выполнять роль задержки, и далее через схемы коммутации выходов 20, 21, 22, 23, 24 идет на выходы данных вычислительной ячейки 37, 38, 39, 40, 41. Одновременно без обработки может быть передана информация через цепи транзита вычислительной ячейки (первая цепь идет через третью схему коммутации входов 15, арифметико-логическое устройство 9, элемент задержки 19, вторая цепь идет через четвертую схему коммутации входов 16, элемент задержки 18 и далее через схемы коммутации выходов 20, 21, 22, 23, 24). При этом в зависимости от состояния второй группы управляющих выходов 26 элементы задержки 17, 18, 19 и сдвигающий параллельно-последовательный регистр 10 либо пропускают информацию через себя без задержки, либо задерживают ее на соответствующее количество тактов.

Третья группа управляющих выходов 27 регистра команд осуществляет выбор направления приема информации на вход арифметико-логического устройства 9 и на входы транзитной передачи информации без обработки через схемы коммутации входов 13, 14 и 15, 16 соответственно. Эта и последующие группы представляют собой набор адресных полей, связанных с соответствующими схемами коммутации.

Четвертая группа управляющих выходов 28 регистра команд осуществляет выбор направления передачи информации с выхода арифметико-логического устройства 9 и с выходов транзитной передачи информации через схемы коммутации выходов 20, 21, 22, 23, 24.

Запоминающая ячейка 3 перед началом решения задачи получает команду в командный регистр 42 аналогично тому, как это описано для вычислительной ячейки. Код команды вводится через программный вход 73 запоминающей ячейки последовательно разряд за разрядом в командный регистр 42 по сигналу управления ввода программы, подаваемому на вход 31. Программный выход 74 обеспечивает возможность последовательного соединения командных регистров 42 запоминающих ячеек. По окончании сигнала управления ввода программы код команды запоминается в командном регистре 42, в результате чего с этого момента времени запоминающая ячейка переходит в режим выполнения программы. Работа с данными ведется последовательно разряд за разрядом младшими разрядами вперед.

Запоминающая ячейка 3 выполняет следующие функции: задержку информации в сдвигающем регистре (динамическое запоминание) на время, заданное в командном регистра 42; хранение информации в сдвигающем регистре (статическое запоминание) на время, определяемое внешним управляющим сигналом: передачу информации без обработки; обмен информацией между двумя потоками данных (коммутацию) по внешнему управляющему сигналу.

Командный регистр 42 настраивает сдвигающий регистр 49 на заданную длину (в битах) в соответствии с состоянием первой группы выходов 56 командного регистра.

При работе в режиме динамического запоминания информация последовательно разряд за разрядом через третий входной коммутатор 45 и через переключатель 48 поступает на информационный вход сдвигающего регистра 49. На выходе они появляется через число тактов, равное заданной длине сдвигающего регистра в битах. Так происходит до тех пор, пока на выходе первого входного коммутатора данных 43 не появляется "1".

Тогда запоминающая ячейка 3 переходит в режим статического запоминания. С этого момента информация в сдвигающем регистре 49 "замораживается", и ее выдача на выходе опять начинается, когда на выходе первого входного коммутатора данных запоминающей ячейки 43 снова появляется "1". При этом вентиль 47 работает в режиме счетного триггера, то есть первая "1", которая появится на выходе первого входного коммутатора 43, запрещает подачу тактовых импульсов на сдвигающий регистр 49, а следующая "1" разрешает, и так далее.

Одновременно без обработки может быть передана информация через цепь транзита запоминающей ячейки (четвертый коммутатор входа 46, триггер задержки 50 и коммутаторы выходов 51, 52, 53, 54, 55).

Обмен информацией между двумя потоками данных (коммутация) производится так. После сброса сигнала ввода программы информация с четвертого входного коммутатора 46 через переключатель 48 поступает на вход триггера задержки 50, а информация с третьего входного коммутатора 45 подается через переключатель 48 на вход сдвигающего регистра 49. С момента, когда на выходе второго входного коммутатора 44 появляется "1", информация с четвертого входного коммутатора 46 через переключатель 48 поступает на вход сдвигающего регистра 49, а информация с третьего входного коммутатора данных запоминающей ячейки 45 подается через переключатель 48 на вход триггера задержки 50. При этом управление переключателя 48 работает в режиме счетного триггера, то есть каждая "1", которая появляется на управляющем входе переключателя, меняет местами информационные входы переключателя.

Вторая группа выходов командного регистра 57 осуществляет выбор направления приема информации на первый вход переключателя 48. Эта и последующие группы представляют собой набор адресных полей, связанных с соответствующими коммутаторами.

Третья и пятая группы выходов командного регистра, соответственно 58 и 60, осуществляют выбор направления передачи информации через выходные коммутаторы 51, 52, 53, 54, 55. При этом третья группа управляет выходом информации, передаваемой по цепи транзита, а пятая - выходом информации, выдаваемой из сдвигающего регистра.

Четвертая группа выходов командного регистра 59 осуществляет выбор направления приема информации на второй вход переключателя 48.

Шестая группа выходов командного регистра 61 осуществляет прием управляющего сигнала на управляющий вход переключателя 48 через второй входной коммутатор 44 и обеспечивает обмен информацией между потоками данных.

Седьмая группа выходов командного регистра 62 осуществляет прием информации на второй управляющий вход сдвигающего регистра 49 и обеспечивает выбор режимов статического и динамического запоминания.

Реализация предлагаемой однородной вычислительной среды позволяет в два раза повысить производительность при выполнении арифметико-логических операций и в десятки раз при выполнении операций коммутации данных в потоках (сортировки, перестановки, вставки, удаления).

Источники информации

1. Авторское свидетельство СССР N 691846, G 06 F 7/00, 1979.

2. Бачериков Г. И., Богачев М.П., Геворкян В.И. и др. Высокопроизводительная система обработки информации в реальном масштабе времени на основе универсальных вычислительных ячеек. В сб.: Мультиконвейерные вычислительные структуры на однородных средах. - Львов: Академия наук УССР, физико-механический институт, препринт N 102 1985, с. 6-13.

3. Патент РФ N 2110088, G 01 F 15/16, 1998.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2000 |

|

RU2180969C1 |

| Ячейка однородной вычислительной среды | 1977 |

|

SU691846A1 |

| СИНЕРГИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2179333C1 |

| ПАРАЛЛЕЛЬНЫЙ ПРОЦЕССОР С ПЕРЕПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1994 |

|

RU2110088C1 |

| Модуль однородной вычислительной структуры | 1984 |

|

SU1359782A1 |

| Ячейка однородной вычислительной структуры | 1990 |

|

SU1798795A1 |

| АСИНХРОННАЯ СИНЕРГИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2198422C2 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА НА БАЗЕ МАТРИЦЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1998 |

|

RU2117326C1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

Изобретение относится к области вычислительной техники и предназначено для создания высокоскоростных систем обработки больших потоков данных в реальном режиме времени. Технический результат - уменьшение сложности выполнения операций коммутации данных и увеличение быстродействия. Технический результат достигается введением блока управления. Группы выходов блока управления соединены с программными входами крайних ячеек матрицы вычислительных ячеек и входами программы матрицы запоминающих ячеек. 3 ил.

Однородная вычислительная среда, содержащая матрицу вычислительных ячеек, соединенных двусторонними связями по вертикали и горизонтали, матрицу запоминающих ячеек, соединенных двусторонними связями по вертикали и горизонтали, генератор тактовых импульсов, выход которого связан общей шиной тактовых импульсов с тактовыми входами всех ячеек, при этом программный выход каждой вычислительной ячейки в строке матрицы вычислительных ячеек связан с программным входом следующей вычислительной ячейки, а выход программы каждой запоминающей ячейки в строке матрицы запоминающих ячеек связан с входом программы следующей запоминающей ячейки, причем каждая запоминающая ячейка содержит командный регистр, два входных коммутатора, два выходных коммутатора и триггер задержки, при этом входы входных коммутаторов являются информационными входами своей ячейки, информационные выходы которой являются выходами выходных коммутаторов, а вход программы, вход сигнала управления ввода программы и выход программы командного регистра являются соответственно входом программы, входом сигнала управления ввода программы и выходом программы для запоминающей ячейки, а каждая вычислительная ячейка содержит арифметико-логическое устройство, регистр команд и дешифратор кода операций, три элемента задержки, три схемы коммутации входов и три схемы коммутации выходов,

причем входы дешифратора кода операции подключены к первой группе выходов регистра команд, а программный вход, вход сигнала управления ввода программы и программный выход регистра команд являются соответственно программным входом, входом сигнала управления ввода программы и программным выходом для вычислительной ячейки, управляющие входы арифметико-логического устройства соединены с группой выходов дешифратора кода операции, первый и второй информационные входы арифметико-логического устройства соответственно подключены к выходам первой и второй схем коммутации входов, причем информационные входы вычислительной ячейки являются входами для каждой из схем коммутации входов, выходы схем коммутации выходов являются выходами вычислительной ячейки, отличающаяся тем, что введен блок управления, у которого первая и вторая группы выходов соединены соответственно с программными входами крайних ячеек матрицы вычислительных ячеек и входами программы крайних ячеек матрицы запоминающих ячеек, а третий выход блока управления связан общей шиной с входами сигналов управления вводом программы всех вычислительных и запоминающих ячеек, при этом группа входов блока управления соединена с группой информационных выходов крайних ячеек матрицы вычислительных ячеек, а все запоминающие ячейки соединены двусторонними связями с соответствующими вычислительными ячейками, при этом в вычислительную ячейку введены четвертая схема коммутации входов, четвертая и пятая схемы коммутации выходов и сдвигающий параллельно-последовательный регистр, группа первых управляющих входов которого связана с группой выходов дешифратора кода операций, а группа вторых управляющих входов связана с второй группой выходов регистра команд, информационный вход сдвигающего параллельно-

последовательного регистра связан с первым выходом арифметико-логического устройства, второй выход которого связан с входом третьего элемента задержки, группа параллельных информационных выходов сдвигающего параллельно-последовательного регистра связана с группой третьих информационных входов арифметико-логического устройства, а выход третьей схемы коммутации входов связан с четвертым информационным входом арифметико-логического устройства, причем последовательный информационный выход сдвигающего параллельно-последовательного регистра связан с информационным входом первого элемента задержки, выход которого соединен с первыми информационными входами схем коммутации выходов, при этом информационный вход второго элемента задержки связан с выходом четвертой схемы коммутации входов, а выход второго элемента задержки - с третьими информационными входами всех схем коммутации выходов, вторые информационные входы которых связаны с выходом третьего элемента задержки, при этом управляющие входы первого, второго и третьего элементов задержки подключены к второй группе выходов регистра команд, управляющие входы всех схем коммутации выходов соединены с четвертой группой выходов регистра команд, причем во всех схемах коммутации входов добавлен пятый информационный вход, который является информационным входом вычислительной ячейки, а управляющие входы всех схем коммутации входов подключены к третьей группе выходов регистра команд и число информационных входов и выходов вычислительной ячейки увеличено до пяти для связи с запоминающей ячейкой, в которую дополнительно введены сдвигающий регистр, два входных коммутатора, три выходных коммутатора, вентиль и переключатель, первый информационный вход которого связан с выходом третьего входного коммутатора, второй информационный вход - с выходом четвертого входного коммутатора, а управляющий вход - с выходом второго входного коммутатора, при этом первый выход переключателя связан с информационным входом сдвигающего регистра, а второй выход - с информационным входом триггера задержки, выход которого соединен с первыми информационными входами выходных коммутаторов, вторые информационные входы которых связаны с выходом сдвигающего регистра, группа первых управляющих входов которого связана с группой первых выходов командного регистра, второй управляющий вход сдвигающего регистра связан с выходом вентиля, второй вход которого связан с шиной тактовых импульсов, а первый вход - с выходом первого входного коммутатора, причем вторая группа выходов командного регистра связана с группой управляющих входов третьего входного коммутатора, четвертая группа выходов командного регистра связана с группой управляющих входов четвертого входного коммутатора, третья и пятая группы выходов командного регистра связаны соответственно с первыми и вторыми управляющими входами всех выходных коммутаторов, шестая группа выходов командного регистра связана с группой управляющих входов второго входного коммутатора, а седьмая группа - с группой управляющих входов первого входного коммутатора.

| Бачериков Г.И | |||

| и др | |||

| Высокопроизводительная система обработки информации в реальном масштабе времени на основе универсальных вычислительных ячеек | |||

| В сб.: Мультиконвейерные вычислительные структуры на однородных средах | |||

| - Львов: Академия наук УССР, 1985 | |||

| ПАРАЛЛЕЛЬНЫЙ ПРОЦЕССОР С ПЕРЕПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1994 |

|

RU2110088C1 |

| Способ лечения поражений мыщелка большеберцовой кости | 1985 |

|

SU1445714A1 |

| Ячейка однородной вычислительной среды | 1977 |

|

SU691846A1 |

| US 5230079 A, 20.07.93 | |||

| СПОСОБ ИЗГОТОВЛЕНИЯ ДРЕВЕСНОСТРУЖЕЧНЫХ ПЛИТ | 0 |

|

SU293701A1 |

Авторы

Даты

1999-08-10—Публикация

1998-08-19—Подача