(54) УСТРОЙСТВО ДЛЯ ИНДИКАЦИИ ЗАПЯТОЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Электронная клавишная вычислительная машина | 1973 |

|

SU496563A1 |

| Электронная клавишная вычислительная машина | 1977 |

|

SU679986A1 |

| Устройств индикации запятой | 1972 |

|

SU485449A1 |

| Устройство для деления в избыточном последовательном коде | 1986 |

|

SU1365078A1 |

| Генератор случайных чисел | 1981 |

|

SU980093A1 |

| Электронная клавишная вычислительная машина | 1982 |

|

SU1068945A1 |

| Электронная клавишная вычислительная машина | 1979 |

|

SU890401A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Устройство для вывода информации | 1986 |

|

SU1322297A1 |

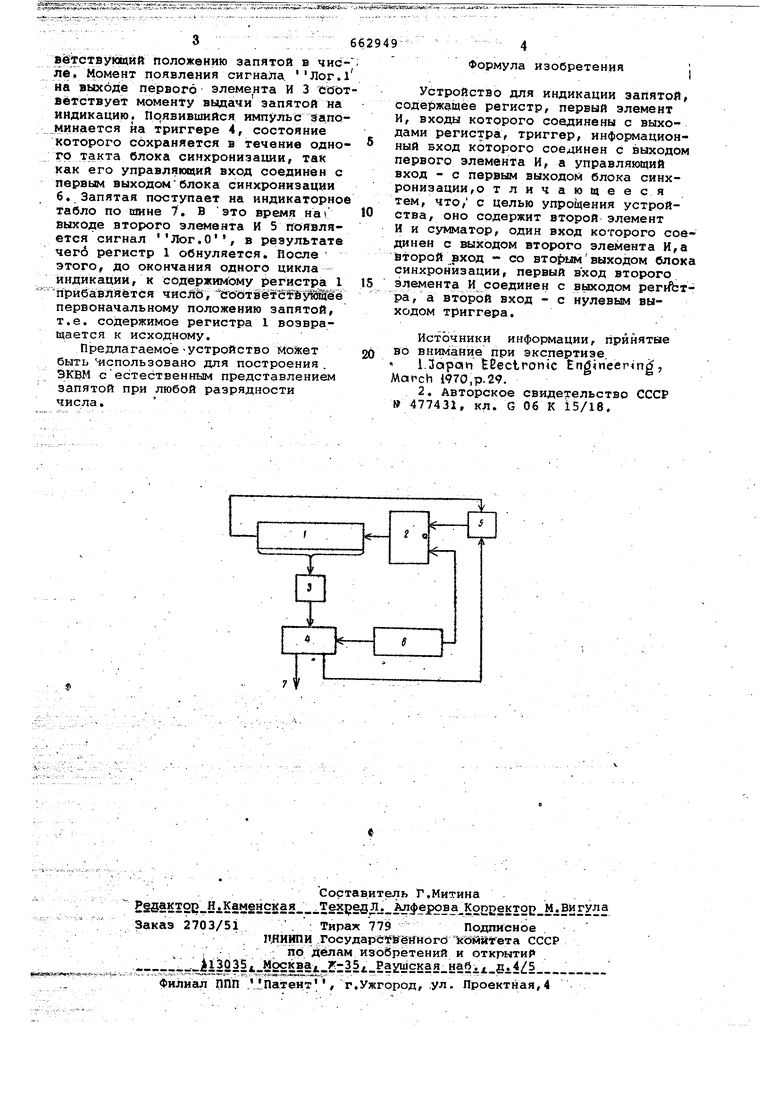

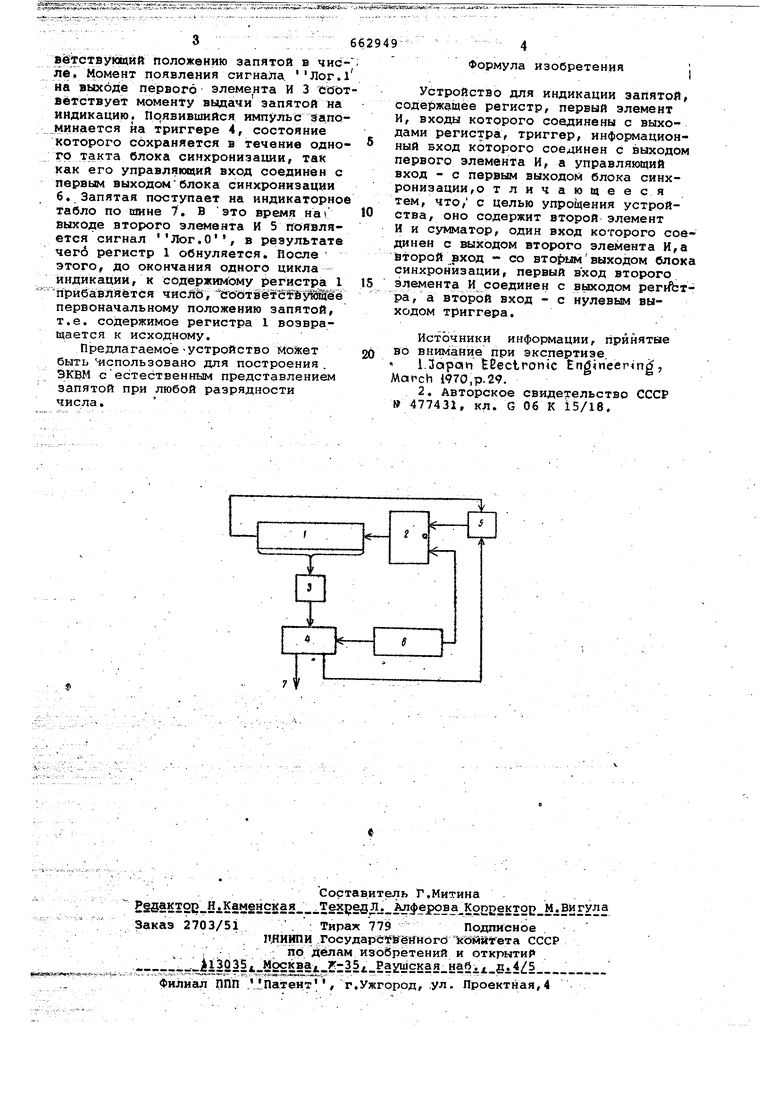

Изобретение относится v. области iвычислительной техники и может найти применение при реализации электрон }ых клавишных вьгчислительньк машин (ЭКВМ). Известно устройство, предназна-. ченное для индикации запятой, содержащее регистр, дешифратор и элементы И, связанные с выходами дешиф ратора и выходами блока синхронизации l .. . недостаток этого устройства состоит в его сложности. Наиболее близким по технической сущности V. данному, изобретению явля ется устройство для индикации запятой, содержащее регистр, элемент И, входы которого соединены с выходами регистра, триггер, информационный вход которого соединен с выходом первого .элемента И, а управлякядий вход - с первым выходом блока син сронизации 2 . недостатком этого устройства яв ляется его сложность из-за большой разрядности регистра запятой и сложности, блока синхронизации. Цель изобретения - упрощение устройства. Это достигается тем, что предлагаемое устройство содержит второй элемент И исумматор, один вход которого соединен с выходсям второго элемента И, а второй вход - со вторым выходом блока синхронизации, первый вход второго элемента И соединен с выходом регистра, а второй вход - с нулевым выходом триггера. Блок-схема предлагаемого устройства п|5еДставлена на чертеже. Устройство содержит регистр 1, сумматор 2, первый элемент И 3, триггер 4, второй элемент И 5, блок синхронизации 6, выходную шину 7. Устройство работает следующим образом. Положение запятой в определенном разряде числа кодируется соотввтствуюЕдим 1СОДОМ, находящимся в регистре 1. наличие запятой в самом старшем разряде числа кодируется нулевым кодсмл; прибавление единицы соответствует сдвигу - пятой вправо, вычитание - сдвигу влево. В режиме индикации за время одного такта блока синхронизации 6 происходит прибавление единицы с помощью сумматора 2 к содержимому регистра 1, в котором первоначально находился код, соотё ствующйй положению запятой в чисе. Момент появления сигнала Лог.l на выходе первого элемента И 3 еоотввтствует моменту выдачи запятой на индикацию. Прявившийся импульс запоминается на триггере 4, состояние которого сохраняется в течение одного такта блока синхронизации, так как его управлякмций вход соединен с первым выходомблока синхронизации 6. Запятая поступает на индикаторное табло по шине 7. В это время на( выходе второго элемента И 5 появляется сигнал Лог.О , в результате чегб регистр 1 обнуляется. После этого, до окончания одного цикла индикации, к содержимому регистра 1 П1эиба;в71йётся числе, 1;1йЬтвётстВ5ШШв первоначальному положению запятой, т.е. содержимое регистра 1 возвращается к исходному.

предлагаемое-устройство может быть «спользовано для построения. ЭКВМ сестественним представлением запятой при любой разрядности числа.

662949

Формула изобретения

Устройство для индикации запятой, содержащее регистр, первый элемент И, входы которого соединены с выходами регистра, триггер, информационный вход которого соединен с выходом первого элемента И, а управляющий вход - с первым выходом блока синхронизации, о тличающееся тем, что, с целью упрощения устройства, оно содержит второй элемент

И и сумматор, один вход которого соединен с выходом второго элемента И,а Второй вход - со вторымвыходом блока синхронизации, первый вход второго

элемента И соединен с выходом perrfbTра, а второй вход - с нулевым выходом триггера.

Источники информации, принятые во внршание при экспертизе

- 1.Japan ESectronic Engineering, March 19ГО,р.2.

Авторы

Даты

1979-05-15—Публикация

1973-03-28—Подача