И добретение относится к вычислительной технике, может быть использовано при создании ЭКВМ с памятью и является усовершенствованием устройства по авт. св. № 1270762.

Цель изобретения - расширение области применения за счет обеспечения двунаправленного обмена информацией.

На фиг. 1 представлена структурная

памяти устройство работает следующим образом.

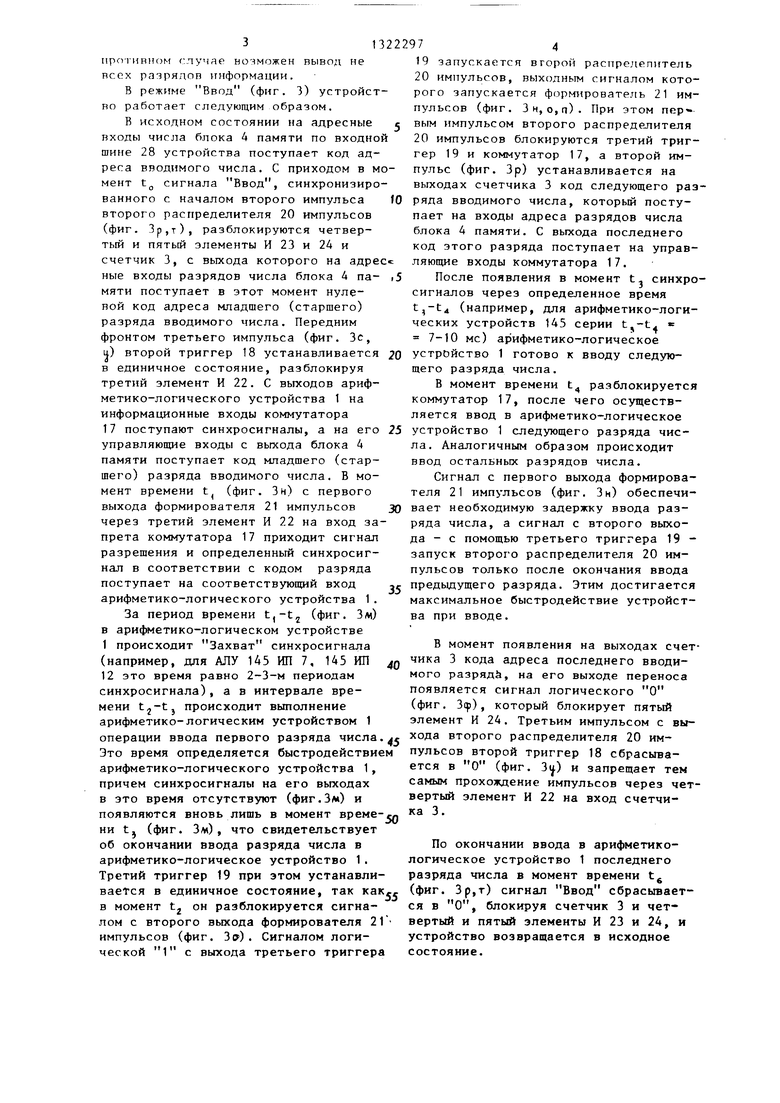

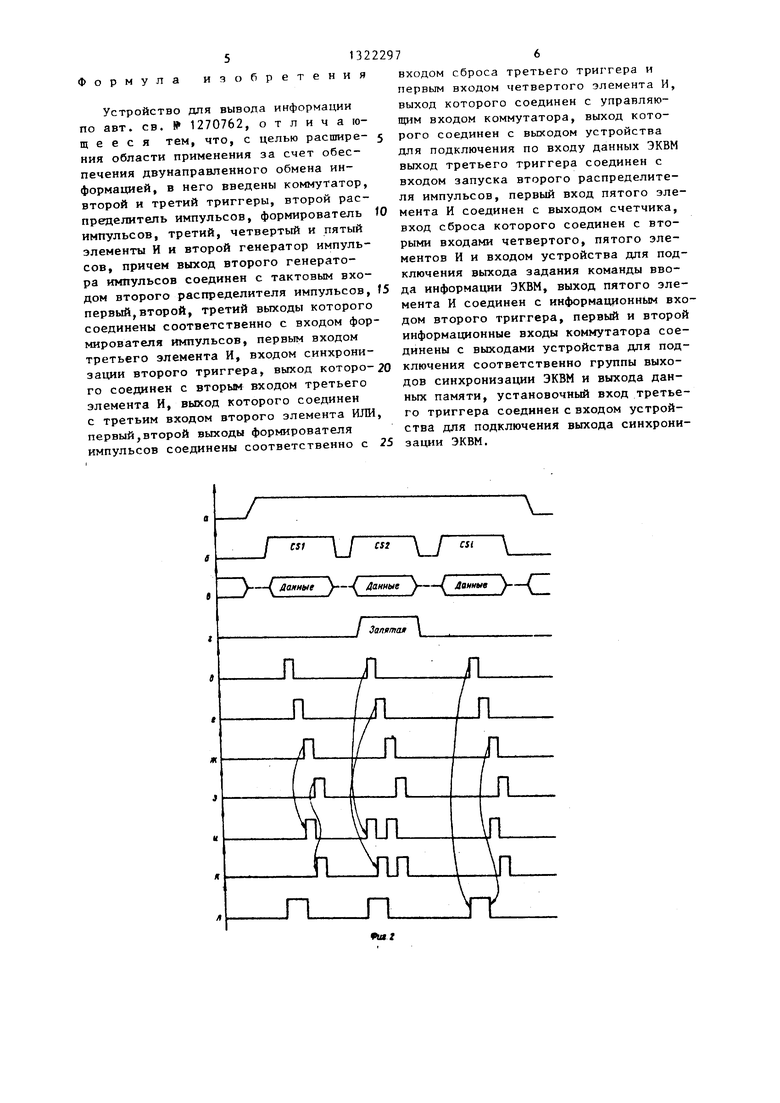

С приходом по шине 14 сигнала Вывод (фиг. 2п) снимается блокировка 5 со счетчика 3, а формирователь 12 формирует пачку импульсов (фиг. 2S ), число которых соответствует числу раз рядов выводимой информации (фиг.26). Причем первый импульс в пачке совпасхема устройства} на фиг. 2 и 3 - вре- О дает по фазе с синхросигналом, соот- менные диаграммы его работы.ветствующим младшему (старшему) разУстройство (фиг. 1) содержит арифметико-логическое устройство 1 электронной клавишной вычислительной машины (ЭКВМ), первый триггер 2, счет- t5 чик 3, блок 4 памяти, первый и второй элементы ИЛИ 5 и 6, первый генератор 7, первый и второй элементы И 8 и 9, преобразователь 10 кода, первый распределитель 11 импульсов, формирова- 20 частоты первого генератора 7 (фиг.2д, тель 12 пачки импульсов, входы груп- е, ж, з) . Первым из этих импульсов пы и вход которого являются соответ- первый триггер 2 устанавливается в ственно входами 13 первой группы и единичное состояние, третьим сбрасы- первым входом 14 устройства, второй вается в нулевое состояние (фиг.2л), вход 15 и вход второй группы 16 уст- а преобразователь 10 кода в первом

ряду выводимой информации, второй импульс совпадает со следующим разрядным сигналом и т.д.

Передним фронтом каждого импульса из пачки запускается распределитель 11 импульсов, который вырабатывает четьфе импульса, сдвинутых относитель но друг друга на один такт выходной

ройства, коммутатор 17, второй и третий триггеры 18 и 19, второй распределитель 20 импульсов, формирователь 21 импульсов, третий, четвертый и пятый элементы И 22-24, второй генератор 25 импульсов.

Устройство работает следующим образом.

В исходном состоянии сигналом логического О по шинам Вывод и Ввод заблокированы счетчик 3, формирователь 12 пачки импульсов и четвертый и пятый элементы И 23 и 24. Таким образом, второй триггер 18 наслучае выдает код запятой, во втором- преобразованный код разряда выходной информации арифметико-логического устройства 1.

30 Сигналы (фиг. 2и), поступающие на счетный вход счетчика 3 с выхода второго элемента ИЛИ 6, устанавливают адрес разрядов числа, вводимого в блок 4 памяти, на входы адреса па которого поступает код адреса числа, а сигналы с первого элемента ИЛИ

элементов И 8 и 9 поступит разрешение (сигнал запятой). В этом случае за время действия разрядного сигнала ад5 осуществляют запись информации в блок 4 памяти. Однако запись кода запятой возможна лишь в том случае,

ходится в нулевом состоянии и блоки- 40 когда с выхода запятой 15 арифметико- рует третий элемент И 22, с выхода логического устройства 1 на входы которого сигнал логического О поступает на третий вход второго элемента ИЛИ 6, а коммутатор 17 заблокирован сигналом логического О, который по-45 Р разряда числа блока 4 памяти из- ступает с выхода четвертого элемента меняется дважды, и дважды поступает И 23. Выходная информация арифмети- сигнал записи (фиг. 2и,к). Первым ко-логического устройства 1 появляет- сигналом осуществляется запись кода ся поразрядно на его выходах, посту- запятой, а вторым - запись информа- пает на преобразователь 10 кода, а 50 соответствующей данному разряд- фаз оимпульсно-кодированные синхросигналы арифметико-логического устройства 1 поступают на входы группы

ному сигналу.

По окончании последнего импульса формирователя 12 и сигнала Вьшод устаройство переходит в исходное состояние. Для нормального функционирования устройства сигнал Вывод должен быть длительностью не менее двух периодов частоты синхросигналов, в

формирователя 12 пачки импульсов и

на информационные входы коммутатора

17.

При выводе информации из арифметико-логического устройства 1 в блок 4

памяти устройство работает следующим образом.

С приходом по шине 14 сигнала Вывод (фиг. 2п) снимается блокировка со счетчика 3, а формирователь 12 формирует пачку импульсов (фиг. 2S ), число которых соответствует числу разрядов выводимой информации (фиг.26). Причем первый импульс в пачке совпачастоты первого генератора 7 (фиг.2д, е, ж, з) . Первым из этих импульсов первый триггер 2 устанавливается в единичное состояние, третьим сбрасы- вается в нулевое состояние (фиг.2л), а преобразователь 10 кода в первом

ряду выводимой информации, второй импульс совпадает со следующим разрядным сигналом и т.д.

Передним фронтом каждого импульса из пачки запускается распределитель 11 импульсов, который вырабатывает четьфе импульса, сдвинутых относительно друг друга на один такт выходной

случае выдает код запятой, во втором- преобразованный код разряда выходной информации арифметико-логического устройства 1.

Сигналы (фиг. 2и), поступающие на счетный вход счетчика 3 с выхода второго элемента ИЛИ 6, устанавливают адрес разрядов числа, вводимого в блок 4 памяти, на входы адреса чиспа которого поступает код адреса числа, а сигналы с первого элемента ИЛИ

элементов И 8 и 9 поступит разрешение (сигнал запятой). В этом случае за время действия разрядного сигнала адкогда с выхода запятой 15 арифметико- логического устройства 1 на входы Р разряда числа блока 4 памяти из- меняется дважды, и дважды поступает сигнал записи (фиг. 2и,к). Первым сигналом осуществляется запись кода запятой, а вторым - запись информа- соответствующей данному разряд-

когда с выход логического у Р разряда ч меняется дваж сигнал записи сигналом осущ запятой, а вт соответс

ному сигналу.

когда с выхода запятой 15 арифметико- логического устройства 1 на входы Р разряда числа блока 4 памяти из- меняется дважды, и дважды поступает сигнал записи (фиг. 2и,к). Первым сигналом осуществляется запись кода запятой, а вторым - запись информа- соответствующей данному разряд-

По окончании последнего импульса формирователя 12 и сигнала Вьшод устаройство переходит в исходное состояние. Для нормального функционирования устройства сигнал Вывод должен быть длительностью не менее двух периодов частоты синхросигналов, в

противном случае ночможен вывод не всех разрядов гнфopмaции.

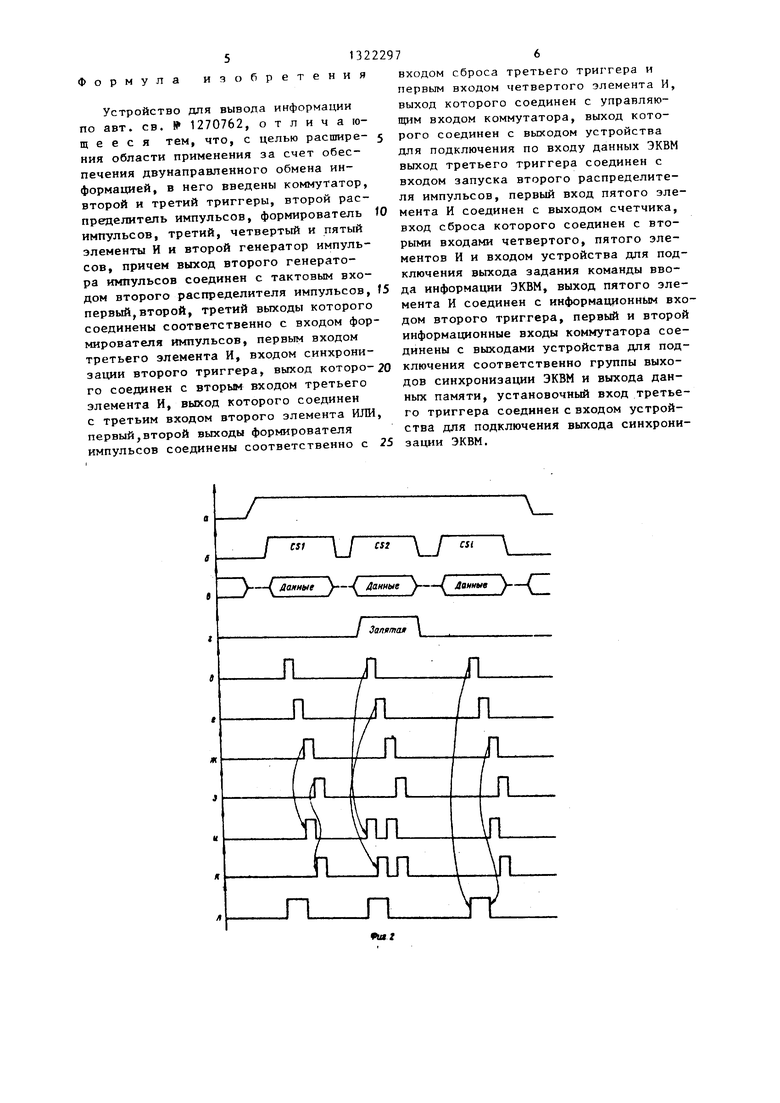

В режиме Ввод (фиг. 3) устройство работает следующим образом.

В исходном состоянии на адресные входы числа блока 4 памяти по входной шине 28 устройства поступает код адреса вводимого числа. С приходом в момент tg сигнала Ввод, синхронизированного с началом второго импульса 10 второго распределителя 20 импульсов (фиг. Зр,т), разблокируются четвертый и пятьй элементы И 23 и 24 и счетчик 3, с выхода которого на адрес ; ные входы разрядов числа блока 4 па- ,5 мяти поступает в этот момент нуле вой код адреса младшего (старшего) разряда вводимого числа. Передним фронтом третьего импульса (фиг. 3с, ц) второй триггер 18 устанавливается 20 в единичное состояние, разблокируя третий элемент И 22. С выходов арифметико-логического устройства 1 на информационные входы коммутатора 17 поступают синхросигналы, а на его 25 управляющие входы с выхода блока 4 памяти поступает код младшего (старшего) разряда вводимого числа. В момент времени t (фиг. Зн) с первого

35

40

выхода формирователя 21 импульсов ЗО через третий элемент И 22 на вход запрета коммутатора 17 приходит сигнал разрешения и определенный синхросигнал в соответствии с кодом разряда поступает на соответствующий вход арифметико-логического устройства 1 . За период времени tj-t (фиг. З/ч) в арифметико-логическом устройстве 1 происходит Захват синхросигнала (например, для АЛУ 145 ИП 7, 145 ИП 12 это время равно 2-3-м периодам синхросигнала), а в интервале времени tj-tj происходит выполнение арифметико-логическим устройством 1 операции ввода первого разряда числа. Это время определяется быстродействием арифметико-логического устройства 1, причем синхросигналы на его выходах в это время отсутствуют (фиг.3м) и появляются вновь лишь в момент време- ни tj (фиг. 3м), что свидетельствует об окончании ввода разряда числа в арифметико-логическое устройство 1 . Третий триггер 19 при этом устанавли19запускается второй распределитель

20импульсов, выходным сигналом которого запускается формирователь 21 импульсов (фиг. Зн, о,п). При этом первым импульсом второго распределителя 20 импульсов блокируются третий триггер 19 и коммутатор 17, а второй импульс (фиг. Зр) устанавливается на выходах счетчика 3 код следующего разряда вводимого числа, который поступает на входы адреса разрядов числа блока 4 памяти. С выхода последнего код этого разряда поступает на управляющие входы коммутатора 17.

После появления в момент t- синхросигналов через определенное время tj-t (например, для арифметико-логических устройств 145 серии t,-t. 7-10 мс) арифметико-логическое устройство 1 готово к вводу следующего разряда числа.

В момент времени t разблокируется коммутатор 17, после чего осуществляется ввод в арифметико-логическое устройство 1 следующего разряда числа. Аналогичным образом происходит ввод остальных разрядов числа.

Сигнал с первого выхода формирователя 21 импульсов (фиг. Зн) обеспечивает необходимую задержку ввода разряда числа, а сигнал с второго выхода - с помощью третьего триггера 19 - запуск второго распределителя 20 импульсов только после окончания ввода предьщущего разряда. Этим достигается максимальное быстродействие устройства при вводе.

В момент появления на выходах счетчика 3 кода адреса последнего вводимого разряди, на его выходе переноса появляется сигнал логического О (фиг. Зф), который блокирует пятый элемент И 24. Третьим импульсом с выхода второго распределителя 20 импульсов второй триггер 18 сбрасывается в О (фиг. 3i) и запрещает тем самым прохождение импульсов через четвертый элемент И 22 на вход счетчика 3.

По окончании ввода в арифметико- логическое устройство 1 последнего разряда числа в момент времени t,

вается в единичное состояние, так (фиг. Зр,т) сигнал Ввод сбрасьшает- в момент tj он разблокируется сигна-ся в С, блокируя счетчик 3 и чет- лом с второго выхода формирователя 2Г вертый и пятый элементы И 23 и 24, и импульсов (фиг. За). Сигналом логи-устройство возвращается в исходное ческой 1 с выхода третьего триггерасостояние.

ой оо10- ,5 20 о 25 35

40

ЗО а. ) .ем , - 3222974

19запускается второй распределитель

20импульсов, выходным сигналом которого запускается формирователь 21 импульсов (фиг. Зн, о,п). При этом первым импульсом второго распределителя 20 импульсов блокируются третий триггер 19 и коммутатор 17, а второй импульс (фиг. Зр) устанавливается на выходах счетчика 3 код следующего разряда вводимого числа, который поступает на входы адреса разрядов числа блока 4 памяти. С выхода последнего код этого разряда поступает на управляющие входы коммутатора 17.

После появления в момент t- синхросигналов через определенное время tj-t (например, для арифметико-логических устройств 145 серии t,-t. 7-10 мс) арифметико-логическое устройство 1 готово к вводу следующего разряда числа.

В момент времени t разблокируется коммутатор 17, после чего осуществляется ввод в арифметико-логическое устройство 1 следующего разряда числа. Аналогичным образом происходит ввод остальных разрядов числа.

Сигнал с первого выхода формирователя 21 импульсов (фиг. Зн) обеспечивает необходимую задержку ввода разряда числа, а сигнал с второго выхода - с помощью третьего триггера 19 - запуск второго распределителя 20 импульсов только после окончания ввода предьщущего разряда. Этим достигается максимальное быстродействие устройства при вводе.

В момент появления на выходах счетчика 3 кода адреса последнего вводимого разряди, на его выходе переноса появляется сигнал логического О (фиг. Зф), который блокирует пятый элемент И 24. Третьим импульсом с выхода второго распределителя 20 импульсов второй триггер 18 сбрасывается в О (фиг. 3i) и запрещает тем самым прохождение импульсов через четвертый элемент И 22 на вход счетчика 3.

По окончании ввода в арифметико- логическое устройство 1 последнего разряда числа в момент времени t,

Формула изобретения

Устройство для вывода информации по авт. св. № 1270762, отличающееся тем, что, с целью расширения области применения за счет обеспечения двунаправленного обмена информацией, в него введены коммутатор, второй и третий триггеры, второй распределитель импульсов, формирователь импульсов, третий, четвертый и пятый элементы И и второй генератор импульсов, причем выход второго генератора импульсов соединен с тактовым вхо10

входом сброса третьего триггера и первым входом четвертого элемента И, выход которого соединен с управляющим входом коммутатора, выход которого соединен с выходом устройства для подключения по входу данных ЭКВМ выход третьего триггера соединен с входом запуска второго распределителя импульсов, первый вход пятого элемента И соединен с выходом счетчика, вход сброса которого соединен с вторыми входами четвертого, пятого элементов И и входом устройства для подключения выхода задания команды ввора импульсов сиемипсп v, .с...,,..

дом второго распределителя импульсов, 15 да информации ЭКВМ, выход пятого .in rtLTr 4ArTUuoun UUftu nM TIUnHHTiTM ВХО

первый,второй, третий выходы которого соединены соответственно с входом фор- 14ирователя импульсов, первым входом третьего элемента И, входом синхронизации второго триггера, выход которо-20 го соединен с вторым входом третьего элемента И, выход которого соединен с третьим входом второго элемента ИЛИ, первый,второй выходы формирователя импульсов соединены соответственно с

25

мента И соединен с информационным входом второго триггера, первый и второй информационные входы коммутатора соединены с выходами устройства для подключения соответственно группы выходов синхронизации ЭКВМ и выхода данных памяти, установочный вход третьего триггера соединен с входом устройства для подключения выхода синхронизации ЭКВМ.

--( Данные -(Данные У- Ланныв У- -(

входом сброса третьего триггера и первым входом четвертого элемента И, выход которого соединен с управляющим входом коммутатора, выход которого соединен с выходом устройства для подключения по входу данных ЭКВМ выход третьего триггера соединен с входом запуска второго распределителя импульсов, первый вход пятого элемента И соединен с выходом счетчика, вход сброса которого соединен с вторыми входами четвертого, пятого элементов И и входом устройства для подключения выхода задания команды вво ,,..

да информации ЭКВМ, выход пятого элеk.in rtLTr 4ArTUuoun UUftu nM TIUnHHTiTM ВХО

мента И соединен с информационным входом второго триггера, первый и второй информационные входы коммутатора соединены с выходами устройства для подключения соответственно группы выходов синхронизации ЭКВМ и выхода данных памяти, установочный вход третьего триггера соединен с входом устройства для подключения выхода синхронизации ЭКВМ.

м

и о

п

/1

п

П

1 Я

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода информации | 1985 |

|

SU1270762A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Процессор с микропрограммным управлением | 1990 |

|

SU1700564A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Устройство для ввода информации | 1986 |

|

SU1403055A1 |

| Устройство для обработки сейсмической информации | 1984 |

|

SU1168963A1 |

| Устройство для отображения информации | 1988 |

|

SU1675929A1 |

Изобретение относится к области вычислительной техники и может быть использовано при создании ЭКВМ с памятью. Целью изобретения является расширение области применения устройства за счет обеспечения двунаправленного обмена информацией. Устройство содержит первый триггер 2, счетчик 3, первый, второй элементы ИЛИ 5, 6, первый генератор 7 импульсов, первый, второй элементы И 8,9, преобразователь 10 кодов, первый распределитель 11 импульсов, формирователь 12 пачки импульсов, коммутатор 17, второй, третий триггеры 18, 19, второй распределитель 20 импульсов, формирователь 21 импульсов, третий, четвертый, пятый элементы И 22, 23, 24 и второй генератор 25 импульсов. Устройство обеспечивает последовательные запись и чтение информации из памяти с.автоматической переадресацией. 3 ил. с € N)

ф

ti t, t, t tf (риг. J

Составитель С.Бурухин Редактор Н.Рогулич Техред И.Попович Корректор А.Обручар

Заказ 2866/46 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для вывода информации | 1985 |

|

SU1270762A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-10—Подача