1

Изобретение относится к вычислительной .технике н може/ найти применение при про бктировании электронных клавишных вычисли|тельных машин (ЭКВМ) с естественньм представлением десятичной запятой.

; Известны электронные клавишные вы1шо1лительные машины, содержащие блок клави туры, входной ш тфратор, три числовых ре;гистра с входными вентилями, два двоичных сумматора, один из которых с входным вен тилем, дешифратор индикации, блок индикации, регистр синхронизации, сдвиговый регистр, два регистра занятой с входными вентилями и устройство управления.

Известная ЗКВМ имеет весьма сложную структуру, так как она сотержит три двоичных сумматора, один из которых используется для обработки регистров запятой, и сложный дешифратор индикации запятой. Кроме того, такая ЭКВМ характеризуется срав: нительпо высоким потреблением мощности за счет вывода на индикацию незначащих нулей,

Цель изобретения - упрощение структуры ЭКВМ и снижение потребляемой мощно- сти.

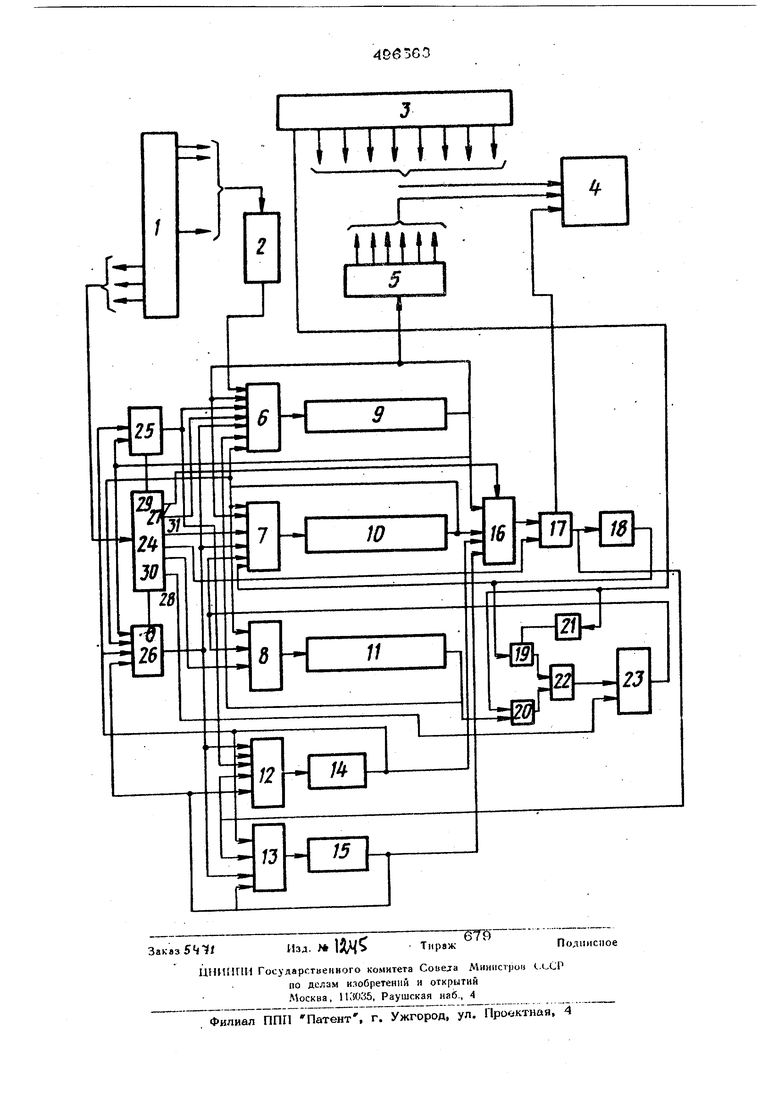

Предлагаемая электронная клавишная вы числительная машина содержит две схемы И , схемы ИЛИ и НЕ , блок нормализации влево, блок норматшзации вправо, первый л второй входы которого соединены с соответствующими вьгходами первого числ(вого регистра и первого регистра запятой, третий аход - с выходом устройства управления, а Bbixorf подключен к входным вентилям указанных perHCTpoBj входы блока нор- мализации влево соединены с выходами первого и второго числовых регистров, выхо- дами регистров запятой и выходом устрой- ства управления, а выход подключен к вхо- )дам входн1х вентилей упомянутых регист- ipOB, вход устройства управления с |выходом блока клавиатуры, а выходы соеди- нены с входным вентилем первого двоично- 1го сумматора, с соответствующими венти- 1дями числовых регистров и двоичных суммаJTopoB, одноименные входы входных вентилей числовых регистров соединены между cQбoйi а также соединены между собой входные вентили второго и третьего числовых регистров, второго и первого числовых реги-1 стров; к входному вентилю первого число- i вого регистра подключен входной шифратор, вход которого соединен с блоком клавиату-1 ры, регистр синхронизации соединен с бло-ч ком индикации, который соединен также ;С дешифратором индикации и первым двоичным сумматором, выход которого подсоединен к сдвиговому регистру и входным вентилям первого и второго per. зтра -за,пятой, вход первого сумматора соединен с выходом входного вентиля, входы которо- : го подключены к выходам первого .и второ- iro числовых регистров и к выходам первого и второго регистров запятой,J выход третьего числового регистра соединен с первым входом первой схемы И , второй вход ко- торой подключен к регистру синхронизации и выходу схемы НЕ, а выход соединен с первым входом схемы ИЛИ , второй вход которой соединен с выходом второй схемы И , входы которой подсоединены к выходу сдвигового регистра и выходу схемы НЕ , выход схемы ИЛИ с вторым двоичным сумматором, выход которого подключен к входным вентилям второго и третьего числовых регистров, На чертеже приведена блок-схема ЭКВМ ЭКВМ ее держит блок клавиатуры 1, входной шифратор 2, регистр синхронизации 3, блок индикации 4, деши4 атор индикащ1и 5, входные вентили 6, 7, 8 числовых регис ров, числовые регистры 9, 10, 11, входные вентили 12, 13, регистров запятой, ре- гистры запятой 14, 13, входные вентили 16 первого двоичного сумматора, первый двоичный сумматор 17, четырехразрядный сдвиговый регистр 18, схемы И 19, 20, инвертор-схема НЕ 21, схему ИЛИ; 22 второй, двоичный сумматор 23, устройство управления 24, блок 25 нормализации впра во, блок 26 нормализации вленэ, шину 27 устройства управления для выдачи сигнала определение порядка и определение результата, шину 28 устройства управления для выдачи сигнала и 6 на вход второго сумматора, шину 29 устройства управ ления для выдачи слгнала окоячание опера шину ЗО устройства управления для выдачи сигнала начало операций ; шину 3 устройства управления для сигнала +; на вход первого сумматора, Эл&ктронная клавишная вычислительная машина работает слегоющим образом, Информация из блока клавиатуры 1 поступает черуез входной 2 и далее через входные вентили 6 в числовой регист . Код, соответствующий запятой числа, наапливается в регистре 14, Код, содержаий, нули во всех четьфех разрядах региста 14, соответствует положению запятой в таршем разряде регистра 9. Для сдвига апятой вправо к содержимому регистра 14 рибавляется , Перед вводом второго перанда число из регистра 9 и запятая из егистра 14 пересылаются в числовой ре« истр 10 и регистр запятой 15 через вхо/ ные вентили 7 и 13, Затем вводится второе число, Таким образом, перед началом операции числа находятся в регистрах 9 и 1О, а их запятые-в регистрах 14 и 15. Вс,якая арифметическая операция состоит из двух последовательно выполняв- мых частей: определение положения запя той, т. е, -порядка результата, и вычисление результата. Определение положения запятой резу льтата производится с помощью сумматора 17. При сложении и вычитании производится выравнивание порядков. Для этого сначала производится сравнёние содержимого регистров 14 и 15 на сумматоре 17, После определения знака разности порядков выполняется выравнивание запятых путем после- довательного прибавления или вычитания из содержимого соответствующего регистра запятой. При этом на шине 27 устройства j управления 24 вырабатывается сигнал определение порядка. Порядок результата накапливается в регистре 15, Определение результата производится с помошью двух двоичных сумматоров 17 и 23 и четырехразрядного сдвигового регистра 18. При этом на шине 27 устройства управления 24 вырабатывается сигнал определение ре-зультата. ; При сложении и вычитании используются только два регистра 9 и 10. Третий регистр 11 используется только при умноже- НИИ и делении. При умножении в нем находится множитель, а при делении в нем вырабатывается частное. Для обработки множителя (частного) не-: обходи:мо последовательно вычитать (прибавлять) по 1 к содержимому младшего разряда регистра 11, Для этой цели ис- , пользуется второй сумматор 23, выполняющий функцию корректирующего сумматора при вычислении числа.При выполнении коррекции на выходе 28 устройства управления 24 вырабатывается сигнал +6.Обработка всех трех регистров при операции умножения и деления производится параллильно . в течение одного цикла регистра синхрони- . зации 3. Возможность одновременной обработки информации всех трех числовых рехистров , обеспечивается тем, что при вычислении первой тетрады результата (при этом на первом выходе регистра синхронизации уро вень ЛОГ 1 } коррекцию можно| не произ водить. Именно в это время производится обработка регистра 11, т. е к младшей тетраде регистра Ц прибавляется или вычитается , с помощью выхода 28 уст ройства управления 24 в зависимости от в полняемой операции Дделение или умножен Обработка первой тетрады регистра 11 производится в первом такте регистра син1хроНизации 3, при этом на вход схемы И 20 поступает уровень ЛОГ 1 из регистра синхронизации 3. Информация из регистра 11 через схему И 20 и схему. ИЛИ 22 поступает на сумматор 23. В течение остальных тактов регистра синхронизации 3 на; входе схемы И 20уровень лог о , а на входе схемы И 19 соединенной с выходом инвертора 21, уро.- вень ЛОГ 1 . Поэтому на сумматор 23 поступает информация из регистра 18 чере схему И 19 и схему ИЛИ 22. Результат операции пересылается в регистр 9, выход которого соединен с дешифратором индикации. 5. I Содержимое регистра 15, определяющее положение запятой результата, передается в регистр 14, откуда запятая выдается на индикацию. В режиме иЕздикации производится после довательное прибавление по шине 31 устройства управления 24 к содержимому регистра 14 на каждом такте регистра сий хронизации 3. I В момент появления переноса в сумма- |Тор 17 запятая высвечивается в блоке ин- .дикации 4. Эта соответствует истинному положению запятой. По окончании цикла регистра синхронизации 3 содержимое регист,ра 14 возБ1..ащается к исходному, поскольIку вычисление производится по модулю, равному количеству тактов регистра синхронизации. Сигналом окончание операции, передаваемым по шине 29 из устройства управления 24, включается блок нормализа ция вправо 25. Сигналы из блока нормализации 25 обеспечивают сдвиг содержимого регистра 9 и положения запятой,хранящейся в регистре 14, вправо с одновремеаным заполнением старших разрядов регистра 9 кодом 1111. Такой сдвиг продолжается до тех пор, пока в младшем разряде ре-, гистра 9 не окажется значащая цифра, и/ш за пятая сдвинется в крайнее правое поло- жение. По окончании нормализации вправо все младшие незначащие нули будут выдви. нуты за разрядную сетку, а старшие разряды будут заполнены кодом 1111. Код 1111 является признаком гашения знакоместа на индикации, по;4тому незначащие ; нули не будут светиться. Перед Е1ачалом операции для приведения регистров в исходное состоя ше производится нормал}1заш1Я влево с помощью блока 26, который запускается с помощью сигнала начало one, рации, выдаваемого на выходе 30 устройства управления 24, После кормализа- |ши1 влево в старших разрядах регистров оказывается значащая цифра или запятая: ЭКВ готова к выполнению операции. Предмет изобретения Электронная клавишная вычислительная машина {ЭКВЛ), содержащая блок клавиатуры, входной шифратор, три числовых регистра с входными вентилями, два двоичных сумматора, один из которых с входным вентилем, дешифратор индикации, блок индикации, регистр синхронизации, сдвиговый :регистр, два регистра запятой с входными вентилями и устройство управления, о тл и ч а ю щ а я с я то.м, что, с целью упрощения структуры ЭКВМ и снижения по требляемой мощности, она содержит дне схемы И , схемы ИЛИ п НН , блок нормализации влево, блок норма.пизации |вправо, первый и второй входы которого соединены с соответствующими выходами первого числового регистра и первого ре |гистра запятой, третий вход - с выходом устройства управления, а выход подключен к входным вентилям указанных регистров, входы блока нормализащп влево соедияеиы с выходами первого и.второго числовых регистров, вь ходами регистров запято(1 и..выходом устройства управления, а В1,1хид подключен ко входам входных вентилей упомянутых регистров, вход устройст-за управления соединен с выходом блока клавиату-. ры,а выходы соединены с входным BGUTii- лем первого двоичного сумматора, с соответствующими вентилями числовых регист- :роБ и двоичных сумматоров, одноименные входы входных вентилей числовьгх регистров соединены между собой, а также со- единены между собой входные вентили вто- рого и третьего числовых рехистров, второго и первого числовых регистров, ко входному вентил1о первого числового регистра подключен входной шифратор, вход которого соединен с блоком клшипггурм, гистр синхрош1заш1И соеоииг-н с блоком и.-

рККЯЩЯ который соединен также с деши4 ратором яндик щив и первым ивоичным сумматором, ыход которсяго полсо«динек к сдвиговому/piMHCTpy и входным вентилям первого и второго; регистра запятой., вход первого сумматора соединен с выходом

входного вентиля, входы которого ПОДКЛ1С ч ны к выходам порвс« о и второго число- iUiix регистров в к выходам первого н второго регистров запятой выход третьего числового регистра соединен с первым

(ВХОДОМ первой схемы И второй вход о Topoii подключен к регистру синхронизац1Л и выходу схемы НЕ , а выход соединен с первым входом схемы ИЛИ , второй вход которой соединен с выходом второй схемы И , входы которой подсоединв 1ы к выходу сдвигового регистра и выходу схемы НЕ: , выход схемы ИЛИ соединен ©о- горым

двоичным сумматором, выход которого ПОДм

кпючен к входным вентилям второго и третьего числовых регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для индикации запятой | 1973 |

|

SU662949A1 |

| ЭЛЕКТРОННАЯ КЛАВИШНАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1973 |

|

SU395837A1 |

| Электронная клавишная вычислительная машина | 1982 |

|

SU1068945A1 |

| Электронная клавишная вычислительная машина | 1977 |

|

SU678487A1 |

| Электронная клавишная вычислительная машина | 1977 |

|

SU679986A1 |

| Цифровой частотомер | 1973 |

|

SU481851A1 |

| Модуль процессора цифровой фильтрации | 1986 |

|

SU1316074A1 |

| Цифровой коррелятор | 1976 |

|

SU610117A1 |

| Устройство преобразования чисел из двоичной системы счисления в двоично-десятичную | 1960 |

|

SU140269A1 |

| УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 1973 |

|

SU408305A1 |

Авторы

Даты

1975-12-25—Публикация

1973-10-04—Подача