Анализ двух старших разрядов показывает, что возможны следующие слу чаи:

1. 0,33..., 0,32..., 0,31..., 0,31,.., 0,23... - это множество

требует умножения на информации.

2. (0,32..., 0,22,

10

1 без сдвига

0,21..., на

на

15

0,20..., 0,21..., - умножения 2 без сдвига.

3. {0,2.., 0,21..., 0,20 0,21..., 0,22...J - умножения 2 без сдвига.

А. 0,22..., 0,12..., 0,11..., 0,10..., 0,11...j - умножения на 1 со сдвигом информации на один

Изобретение относится к вычислительной технике и может быть использовано при конструировании и разработке специализированных и универсальных процессоров.

Цель изобретения - сокращение количества оборудования.

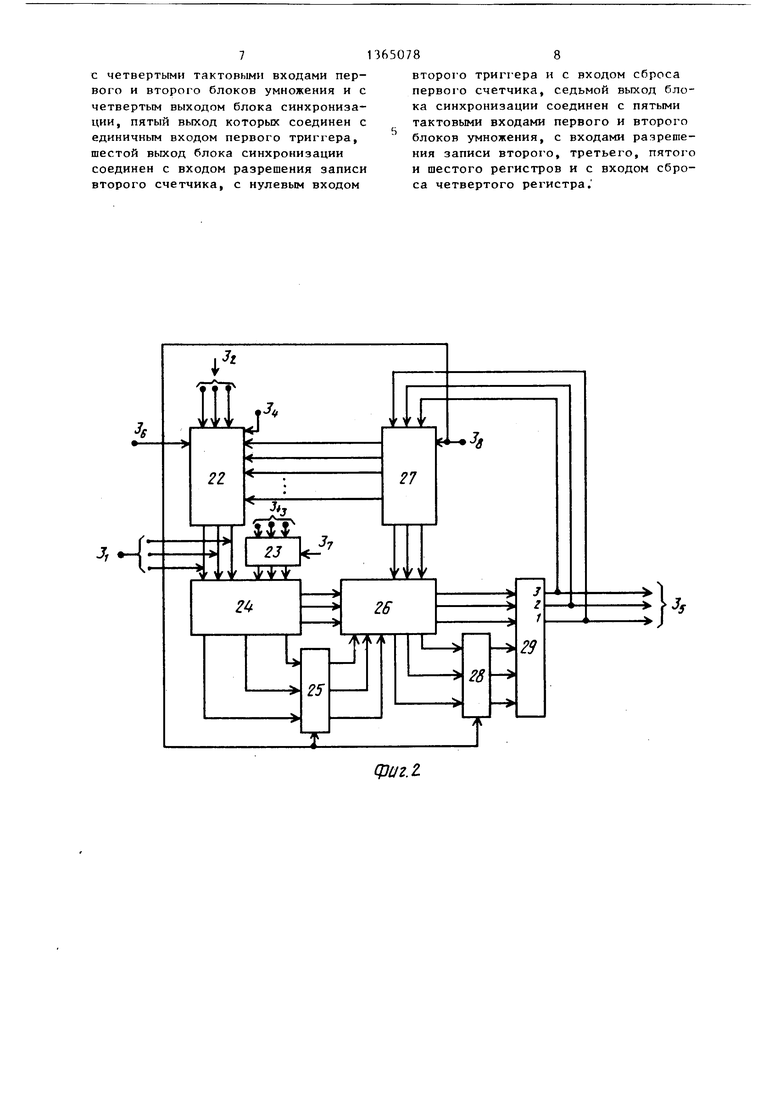

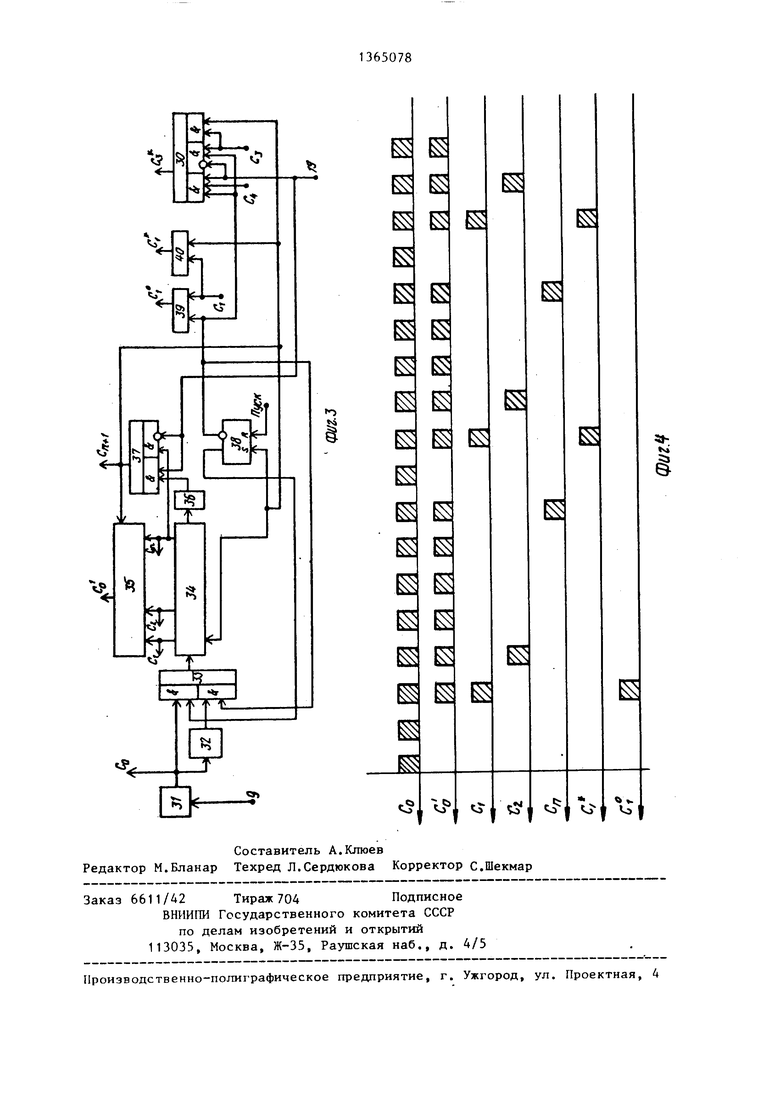

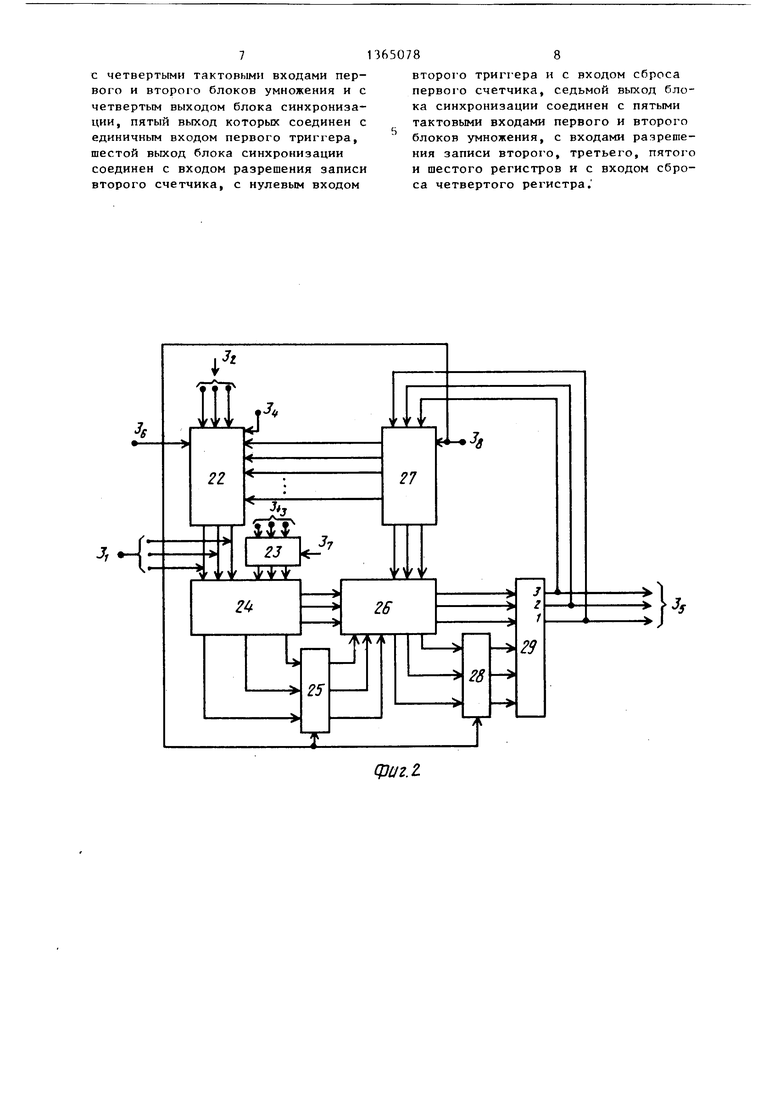

На фиг. 1 представлена схема устройства для деления в избыточном последовательном коде; на фиг. 2 - схема блока умножения; на фиг. 3 - схема блока синхронизации на фиг. 4 - временная диаграмма работы устройства.

Устройство для деления в избыточном последовательном коде (фиг. 1) содержит вход 1 делителя устройства, вход 2 делимого устройства, блоки 3 и 4 умножения, схему 5 сравнения с нулем, регистр 6, элемент И 7, триггер 8, счетчики 9 и 10, триггер 11, элемент И 12, элемент 13 запрета, блок 14 синхронизации, выход 15 устройства, регистры 16 и 17, блок 18 памяти, регистры 19-21.

Блок 3(4) умножения (фиг. 2) содержит регистры 22 и 23, узел 24 памяти, регистр 25, узел 26 памяти, регистры 27 и 28 и сумматор 29. ется цифра, на которую необходимо

Блок 14 синхронизации (фиг. 3) со- зо умножать, и бит, указывающий, требу- держит элемент И-ИЛИ 30, генератор 31 ется или нет дополнительный сдвиг, тактовых импульсов, элемент 32 задержки, элемент И-ЦПИ 33, распределитель 34 импульсов, элемент ИЛИ 35, элемент 36 задержки, элемент И-ИЛИ 37, триггер 38, элементы И 39 и 40.

Устройство работает в четвертичной избыточной системе счисления,код последовательный, под каждую.цифру

40

25

разряд в сторону старшего разряда.

5.,12...| - умножения на 2 20 со сдвигом информации.

6.. П... - умножения на 3 со сдвигом информации.

7.,12... - умножение на 2 со сдвигом информации.

8.(0,П..., О,Го..., 0,ТК..} - умножение на 1 со сдвигом информации.

С выхода блока 18 памяти считываЭта информация по сигналу С, поступающему из блока 14 синхронизации записывается в регистр 19. Одновременно по сигналу С цифра с выхода

35

отводится три двоичных разряда.Чтобы упростить изложение, будем под словами информационный вход (выход) понимать группу, состоящую из трех входов-выходов и называть вход/выход.

Устройство (фиг. 1) работает следующим образом.

Делитель с входа 1 устройства и делимое с входа 2 устройства разряд за разрядом, начиная со старшего, заполняют соответственно регистры 16, 17 и 20, 21. Одновременно два разряда делителя из регистров 16 и 17 поступают на адресные входы блока 18 памяти, где происходит определение первой цифры числа, преобразующего делитель к виду, содержащему единицу в самом старшем разряде, имеющем вес 4°. Делимое (А) и делитель (D) нормализованы.

45

50

55

регистра 19 записывается в регистры

23блоков 3 и 4 умножения. Регистры 20 и 21 служат для задержки на два такта делимого. По окончании шага решения регистр 19 сбрасывается

в нуль сигналом С , . Блок умножения (фиг. 2) работает следующим образом.

В узле памяти в таблицу умножения дополнительно введена строка умножения на цифру (-3). Кроме того, допускается параллельная перезапись содержимого регистра 27 в регистр 22 Перенос в старший разряд из узла 24 памяти в узел 26 памяти кодируется так, как это принято в четверичной избыточной системе счисления. В узле

24памяти записана таблица умножения цифр четверичной избыточной системы счисления, включая цифру (-3).

В узле 26 памяти записана таблица сложения трех цифр, а в сумматор 29 - двух цифр, поступающих на его входы. Регистры 25 и 27 выполняют роль заАнализ двух старших разрядов показывает, что возможны следующие случаи:

1. 0,33..., 0,32..., 0,31..., 0,31,.., 0,23... - это множество

требует умножения на информации.

2. (0,32..., 0,22,

1 без сдвига

0,21..., на

на

0,20..., 0,21..., - умножения 2 без сдвига.

3. {0,2.., 0,21..., 0,20 0,21..., 0,22...J - умножения 2 без сдвига.

А. 0,22..., 0,12..., 0,11..., 0,10..., 0,11...j - умножения на 1 со сдвигом информации на один

ется цифра, на которую необходимо

разряд в сторону старшего разряда.

5.,12...| - умножения на 2 со сдвигом информации.

6.. П... - умножения на 3 со сдвигом информации.

7.,12... - умножение на 2 со сдвигом информации.

8.(0,П..., О,Го..., 0,ТК..} - умножение на 1 со сдвигом информации.

С выхода блока 18 памяти считывао умножать, и бит, указывающий, требу- ется или нет дополнительный сдвиг,

0

Эта информация по сигналу С, поступающему из блока 14 синхронизации записывается в регистр 19. Одновременно по сигналу С цифра с выхода

5

5

0

5

регистра 19 записывается в регистры

23блоков 3 и 4 умножения. Регистры 20 и 21 служат для задержки на два такта делимого. По окончании шага решения регистр 19 сбрасывается

в нуль сигналом С , . Блок умножения (фиг. 2) работает следующим образом.

В узле памяти в таблицу умножения дополнительно введена строка умножения на цифру (-3). Кроме того, допускается параллельная перезапись содержимого регистра 27 в регистр 22. Перенос в старший разряд из узла 24 памяти в узел 26 памяти кодируется так, как это принято в четверичной избыточной системе счисления. В узле

24памяти записана таблица умножения цифр четверичной избыточной системы счисления, включая цифру (-3).

В узле 26 памяти записана таблица сложения трех цифр, а в сумматор 29 - двух цифр, поступающих на его входы. Регистры 25 и 27 выполняют роль задержек на один такт. После выполнения операции умножения цифры, хранимой в регистре 23, на две цифры делимого на выходе сумматора 29 появляется старшая цифра результата. Если умножение должно вестись без дополнительного сдвига, то в старшем разряде появляется цифра 0.01.Следующие за этой цифрой разряды начинают анализироваться на нуль.

Если умножение требует дополнительного сдвига, то анализ на нуль должен начаться на разряд позже. Это достигается изменением номера тактирующего сигнала, устанавливающего триггер 8 в единичное состояние (фиг. 3 и 4 сигнал Cj). Сдвиг произведений делимого У на с/ и делителя X на а осуществляется введением в нулевом шаге дополнительного импульса в серию Ср (фиг. 3 и 4). В результате числа, записываемые в регистры 27 блоков 3 и 4 умножения, перемещащую после запятой цифру текуще -о знаменателя, взятую со знаком минус.Для умножения на единицу число помещается в регистр 27 и пропускается на узел 26 памяти изменения. Умножение на d; осуществляется в узле 24 памяти. Однако кроме умножения следует сдвинуть частичное произведение на такое

Q число разрядов, сколько нулей стояло перед значащей цифрой после запятой. Операция определения количества разрядов сдвига осуществляется следующим образом. После прохождения разряg да с весом 4, триггер 8 перебрасывается в единичное состояние (это осуществляется сигналом С). Схема 5 сравнения осуществляет проверку текущего разряда, если он нулевой, то выдается единица, которая через элемент И 7 поступает на счетчик 9 и увеличивает его содержимое на единицу. Это продолжается до тех пор,пока не встретится значащий разряд. Если

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем алгебраических уравнений | 1986 |

|

SU1324036A1 |

| Делительное устройство | 1983 |

|

SU1168929A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для деления в избыточном коде | 1984 |

|

SU1280612A1 |

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| Устройство для деления | 1990 |

|

SU1803913A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

Изобретение относится к вычислительной технике и может быть использовано при конструировании и разработке специализированных и универсальных процессоров. Целью изобретения является сокращение количества оборудования. Поставленная цель достигается тем, что устройство для деления в избыточном последовательном коде, содержащее блоки 3, 4 умножения, регистры 6, 16, 17, 19, 20, 21, блок 14 синхронизации и блок 18 памяти, содержит счетчики 9, 10,триггеры 8, 11, элементы И 7, 12, элемент 13 запрета и схему 5 сравнения с нулем с соответствующими связями. 4 ил.. 1 табл. г (Л со 05 ел о оо

ются на один разряд в сторону старщих 25 число нулевых разрядов равно п, то

разрядов. По сигналу С ., содержимое регистров 27 блоков 3 и 4 умножения переписывается в регистры 22.

В основе деления лежит алгоритм приведения делителя к единице.Пусть дано, что

Z - I - X

Тогда, умножая числитель и знаменатель на одни и те же числа, получают

X. /,.«(, ... с/„

Числа о(; выбирают так, что

Х-о/, ..(,, ... 1 .,

(1)

Допустим, что после первого умножения делитель стал равным X, X 1 1 J, где о( цифра, определяемая в блоке 18. Тогда, чтобы выполнить условие (1), следует взять о/, 1, d. Откуда

Х,о(, X,(1,dJ 1 -d , О d,(d,d;)(dida,)

1 О d , d в следующем шаге

,- 1.0 dи так далее, где d ; е{3,2,1,0,Т,2.

Таким образом, в каждом шаге необходимо знаменатель и числитель умножать на единицу и на первую знача0

на выходе счетчика 9 появляется сигнал переполнения, который прекращает выполнение операции. Остановимся на случае, когда число нулевых разрядов меньше п. Например, как для а/ . Toi-

5

0

да на выходе схемы 5 сравнения появится только один импульс. В следующем такте схема 5 сравнения выдает нуль (текущий разряд значащий), на выходе элемента 13 запрета возникает сигнал, по которому осуществляется запись цифры в регистр 6. Одновременно триггер 8 перебрасывается в нуль и схема 5 сравнения отключается. По окончании цикла сигналом С,, содержимое счетчика 9 переписывается в счетчик 10, а счетчик 9 сбрасывается в нуль.

В следующем цикле в первом такте из регистра 27 считывается старшая цифра, а из регистра 22 - нуль. Одновременно содержимое счетчика 10 уменьщается на единицу.

В следующем такте из счетчика Q вновь считывается единица, образуется сигнал заема, который перебрасывает триггер 11 в единицу. Элемент И 12 открывается, и на регистр

22 поступает серия С . Происходит

I

g умножение dj на единицу. Если переноса нет, т.е. d, цифра вспомогательного кодирования О,1,2,Т то d запоминается в регистре 25, выполняющем роль задержки на такт.

Если dj есть цифра основного кодирования С, 2, 3j, то она преобразуется в два разряда 11, 12, J. Старший первый разряд поступает на узел 26 памяти непосредственно, а второй - через регистр 25. Далее все протекает как при обычном умножении. Блоки 3 и 4 умножения идентичны и работают одинаково. Исключение составляет только то, что блок 3 преобразует делитель, а блок 4 - делимое.

Следует указать, что с выхода регистра 6 цифра вьщается с присвоением знака. Присвоение знака осуществляется в соответствии с таблицей.

Устройство для деления в избыточном последовательном коде, содержащее два блока умножения, блок синхронизации, блок памяти и шесть регистров, причем выход первого блока умножения соединен с информационным входом первого регистра, вход делителя устройства соединен с информационным входом первого регистра, выход которого соединен с информационным входом второго регистра, выход которого соединен с входом первого сомножителя первого блока умножения, выходы второго и третьего регистров соединены с адресным входом блока памяти, выход которого соединен с информационным входом четвертого регистра, вход делимого устройства сое

динен с информационным входом пятого регистра, выход которого соединен с информа1Ц1онным входом шестого регистра, выход которого соединен с входом первого слагаемого второго блока умножения, выходы разрядов, кроме старшего, четвертого регистра соединены с входами второго сомножителя первого и второго блоков умножения, вход Пуск устройства соединен с входом запуска блока синхронизации, первый выход которого соединен с первыми тактовыми входс1ми первого и второго

g блоков умножения, второй выход блока синхронизации соединен с входом разрешения записи четвертого регистра, отличающееся тем, что, с целью сокращенг1я количества оборудования, оно содержит два триггера, схему сравнения с нулем, два зле- мента РГ, элемент запрета и два счетчика, причем выход первого регистра соединен с входом второго сомножи5 теля первого блока умножения, выход которого соединен с входом схемы сравнения с нулем, выход которой соединен с первым входом первого элемента И, выход которого соединен с упQ равляю цим входом элемента запрета, с информационным входом первого триггера и со счетным входом первого счетчика, разрядный выход которого соединен с информационным входом второго счетчика, выход заема которого соединен с единичным входом второго триггера, выход которого соединен с первым входом второго элемента И, вы ход которого соединен с вторыми тактовыми входе1ми первого блока умножения и второго блока умножения,выход которого является выходом устройства, выход старшего разряда четвертого регистра и выход переноса первого счетчика соединены соответственно с входами режима блокировки блока синхронизации, третий выход которого соединен с третьими тактовыми входами первого и второго блоков умножения, с вторыми входами первого и второго элементов И, с вычитающим входом второго счетчика и с входом разрешения записи первого триггера, выход которого соединен с третьим входом первого элемента И и с информационным входом элемента запрета, выход которого соединен с входом разрешения записи первого регистра,, вход разрешения выдачи которого соединен

5

0

5

0

5

с четвертыми тактовыми входами первого и второго блоков умножения и с четвертым выходом блока синхронизации, пятый которых соединен с единичным входом первого триггера, шестой вькод блока синхронизации соединен с входом разрешения записи второго счетчика, с нулевым входом

650788

второго трип-ера и с входом сброса первого счетчика, седьмой выход блока синхронизации соединен с пятыми тактовыми входами первого и второго блоков умножения, с входами разрешения записи второго, третьего, пятого и шестого регистров и с входом сброса четвертого регистра,

5

фиг.г

| Авторское свидетельство СССР № 1206770, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Конвейерное устройство для деления интерационного типа | 1984 |

|

SU1179321A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гаврилов Ю.В., Пучков А.И | |||

| Арифметические устройства быстродействующих ЭЦВМ | |||

| - М.: Советское радио, 1970, с | |||

| Способ изготовления замочных ключей с отверстием для замочного шпенька из одной болванки с помощью штамповки и протяжки | 1922 |

|

SU221A1 |

Авторы

Даты

1988-01-07—Публикация

1986-07-02—Подача