рифмир ющего транзистора подключена к шине нулевого потенциала, п дополнительных логарифмирующих транзисторов и л дифференциальных операционных усилителей, эмиттер каждого i-то (, 2, ..., п-1) дополнительного логарифмирующего транзистора соединен с коллектором (i + )-ro дополнительного логарифмирующего транзистора и с неинвертирующим входом соответствующего дифференциального операционного усилителя, инвертирующий вход которого соединен с базой соответствующего дополнительного логарифмирующего транзистора и с выходом того же дифференциального операционного усилителя, коллектор первого дополнительного логарифмирующего транзистора подключен к эмиттеру основного логарифмирующего транзистора, а эмиттер ;г-го дополнительного логарифмирующего транзистора соединен с выходом операционного усилителя, дополнительио введен .сумматор, один вход которого соединен с выходом операционного усилителя, а другие входы - с выходами соответствующих дифференциальных операционных усилителей.

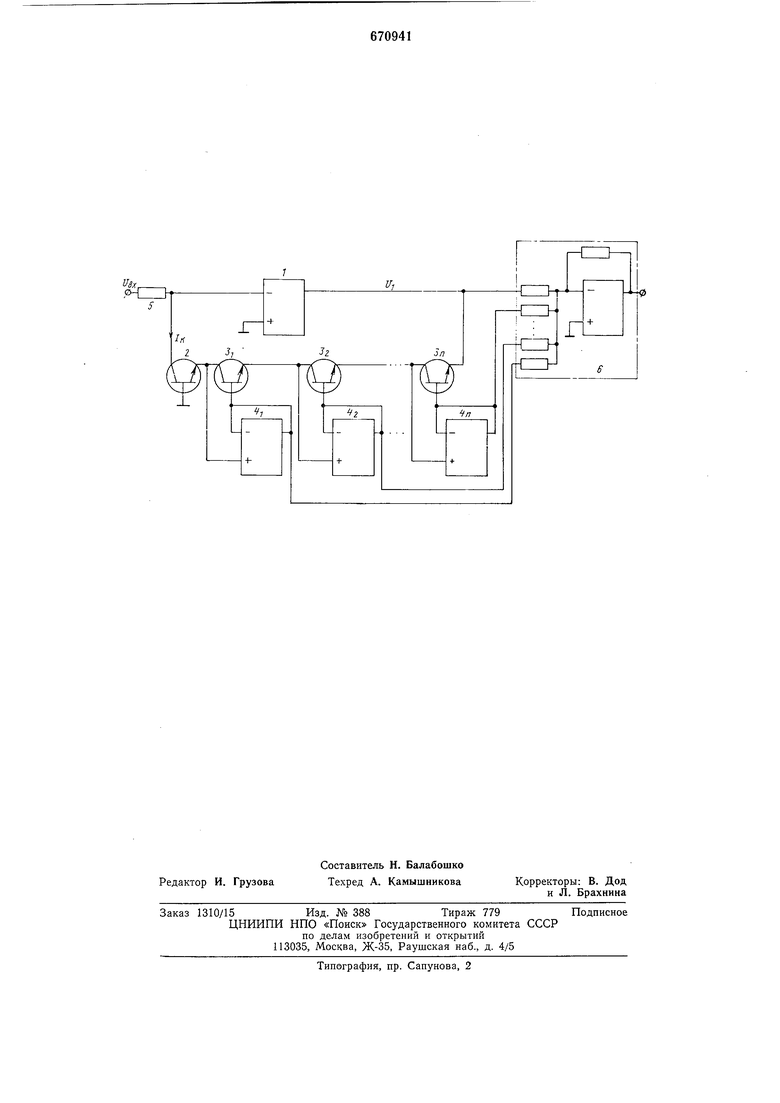

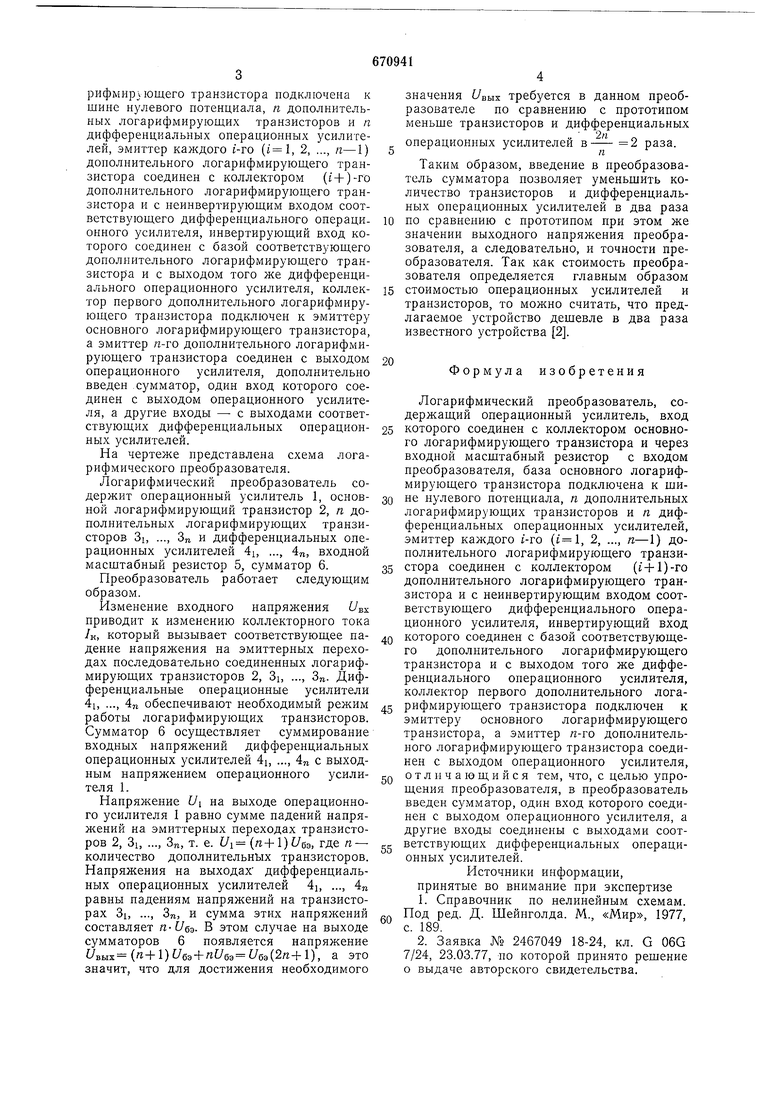

На чертеже представлена схема логарифмического преобразователя.

Логарифмический преобразователь содержит операционный усилитель 1, основной логарифмирующий транзистор 2, п дополнительных логарифмирующих транзисторов Зь ..., Зп и дифференциальных операционных усилителей 4i, ..., 4„, входной масштабный резистор 5, сумматор 6.

Преобразователь работает следующим образом.

Изменение входного напряжения УВХ приводит к изменению коллекторного тока /к, который вызывает соответствующее падение напряжения на эмиттерных переходах последовательно соединенных логарифмирующих транзисторов 2, Зь ..., Зтг- Дифференциальные операционные усилители 4i, ..., 4я обеспечивают необходимый режим работы логарифмирующих транзисторов. Сумматор 6 осуществляет суммирование входных напряжений дифференциальных операционных усилителей 4i, ..., 4„ с выходным напряжением операционного усилителя 1.

Напряжение f/i на выходе операционного усилителя 1 равно сумме падений напряжений на эмиттерных переходах транзисторов 2, Зь ..., 3„, т. е. f/i (rt-f l)f/63, где п - количество дополнительных транзисторов. Напряжения на выходах дифференциальных операционных усилителей 4ь ..., 4п равны падениям напряжений на транзисторах Зь -.., Зп, и сумма этих напряжений составляет n-f/бэ. В этом случае на выходе сумматоров 6 появляется напряжение вых(«+1)/бэ + (2п-М), а это значит, что для достижения необходимого

значения /вых требуется в данном преобразователе по сравнению с прототипом меньще транзисторов и дифференциальных

операционных усилителей раза.

п

Таким образом, введение в преобразователь сумматора позволяет уменьшить количество транзисторов и дифференциальных оиерационных усилителей в два раза

по сравнению с прототипом при этом же значении выходного напряжения преобразователя, а следовательно, и точности преобразователя. Так как стоимость преобразователя определяется главным образом

стоимостью операционных усилителей и траизисторов, то можно считать, что предлагаемое устройство дешевле в два раза известного устройства 2.

Формула изобретения

Логарифмический преобразователь, содержащий операционный усилитель, вход

которого соединен с коллектором основного логарифмирующего транзистора и через входной масштабный резистор с входом преобразователя, база основного логарифмирующего транзистора подключена к щине нулевого потенциала, п дополнительных логарифмирующих транзисторов и п дифференциальных операционных усилителей, эмиттер каждого t-ro (, 2, ..., п-1) дополнительного логарифмирующего транзистора соединен с коллектором (f+l)-ro дополнительного логарифмирующего транзистора и с неинвертирующим входом соответствующего дифференциального операционного усилителя, инвертирующий вход

которого соединен с базой соответствующего дополнительного логарифмирующего транзистора и с выходом того же дифференциального операционного усилителя, коллектор первого дополнительного логарифмирующего транзистора подключен к эмиттеру основного логарифмирующего транзистора, а эмиттер л-го дополнительного логарифмирующего транзистора соединен с выходом операционного усилителя,

отличающийся тем, что, с целью упрощения преобразователя, в преобразователь введен сумматор, один вход которого соединен с выходом операционного усилителя, а другие входы соединены с выходами соответствующих дифференциальных операционных усилителей.

Источники информации, принятые во внимание при экспертизе

1.Справочник по нелинейным схемам. Под ред. Д. Шейнголда. М., «Мир, 1977, с. 189.

2.Заявка № 2467049 18-24, кл. G 06G 7/24, 23.03.77, по которой принято рещение о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2252452C1 |

| ШИРОКОПОЛОСНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2419196C1 |

| Аналоговое логарифмическое вычислительное устройство | 1982 |

|

SU1095198A1 |

| Логарифмический преобразователь | 1983 |

|

SU1117660A1 |

| Логарифмический преобразователь | 1982 |

|

SU1064283A1 |

| Преобразователь напряжение-ток | 1984 |

|

SU1228023A1 |

| ЦИФРОУПРАВЛЯЕМЫЙ ЛОГАРИФМИЧЕСКИЙ УСИЛИТЕЛЬ | 2013 |

|

RU2568932C2 |

| Аналоговое логарифмическое вычислительное устройство | 1983 |

|

SU1137486A2 |

| Устройство усиления | 1989 |

|

SU1617629A1 |

| Логарифмический усилитель | 1979 |

|

SU840950A1 |

Авторы

Даты

1979-06-30—Публикация

1978-01-25—Подача