сигналов, инвертирующий вход второгоявляется вторым входом блока лога

операционного усилителя соединен срифмирования отношения сигналов,

первым выводом второго масштабноговыходом которого является выход перрезистора, второй вывод которогового операционного усилителя.

1064283

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1981 |

|

SU978159A1 |

| Вычислительное устройство и запоминающий масштабно-суммирующий блок | 1980 |

|

SU1043670A1 |

| Логарифмический преобразователь (его варианты) | 1982 |

|

SU1078442A1 |

| ЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2252452C1 |

| УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В СТЕПЕНЬ | 1999 |

|

RU2175147C2 |

| Логарифмический преобразователь | 1982 |

|

SU1043678A1 |

| Логарифмический преобразователь | 1979 |

|

SU830421A1 |

| Антилогарифмический преобразователь (его варианты) | 1982 |

|

SU1053116A1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Логарифмический аналого-цифровой преобразователь | 1981 |

|

SU947874A1 |

1. ЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий генератор управляющих импульсов, основной дифференциальный усилитель, основной элемент с управляемым коэффициентом передачи, отличающийся тем, что, с целью повышения быстродействия и точности, в него введены первый и второй блоки логарифмирования отношения сигналов, первый и второй модуляторы, дополнительные дифференциальный усилитель и элемент с управляемым коэффициентом передачи, первый и второй демодуляторы и сумматор, выход которого является выходом логарифмического преобразователя, входы первого и второго модуляторов являются соответственно первым и вторым входами логарифмического преобразователя, выход первого модулятора соединен с первым входом первого блока логарифмирования отношения сигналов, выход которого соединен с входом основного элемента с управляемым коэффициентом передачи, выход которого подключен к входу первого демодулятора и к первому входу сумматора, выход второго модулятора соединен с первым входом второго блока логарифмирования отношения сигналов,, выход которого соединен с входом дополнительного элемента с управляемым коэффициентом передачи, выход которого подключен к входу второго демодулятора и ко второму входу сумматора, выходы первого и второго демодуляторов соединены с первыми .входами основного и дополнительного дифференциальных усилителей, вторые входы которых соединены и являются третьим входом логарифмического преобразователя, четвертым и пятым входами которого являюгс.я вторые входы соответственного первого и второго блоков логарифмирования отношения сигналов, выход генератора управляющих импульсов подключен к управляющим входам первого л второго модуляторов и первого и второго демодуляторов . 2. Преобразователь по п. 1, о т-i л и ч а ю щ и и с я тем, что блок логарифмирования отношения сигналов содержит первый и второй операционные усилители и первый и второй логарифмирующие транзисторы, выход О5 первого операционного усилителя соединен с базой первого логарифмирую4 щего транзистора, эмиттер которого ГС соединен с эмиттером второго логарифмирующего транзистора и с первым 00 выводом развязывающего резистора, вта со рой вывод которого подключен к выходу второго операционного усилителя, коллекторы первого и второго . логарифмирующих транзисторов соеди нены с инвертирующими входами соответственно второго и первого операционных усилителей, неинвертирующие входы которых подключены к шине нулевого потенциала, инвертирующий вход первого операционного усилителя соединен с первым выводом первого масштабного резистора, второй вывод которого является первым входом блока логарифмирования отношения

1

Изобрете.ние относится к устройствам преобразования сигналов по логарифмическому закону и может быть использовано в аналоговых вычислительных машинах.

Известен логарифмический преобразователь, содержащий логарифматор, ключи, элемент с управляемым коэффициентом передачи, генератор управляющих импульсов, усилители ClJУказанное устройство ха,рактеризуется низким быстродействием.

Наиболее близким к предлагаемому является логарифмический преобразователь , содержащий первый и второй усилители, логарифмирующих и терг-локомпенсирующий транзисторы, источник образцового тока, дифференциальный усилитель, токовадающий и масштабный резисторы, источник опорного напряжения, ключевой элемент, накопительный конденсатор, элемент с управляемым коэффициентом передачи и генератор тактовых им-, пульсов, база логарифмирующего транзистора подключена к шине нулевого потенциала, а коллектор соединен с инвертирующим входом первого усилителя, выход которого присоединен к эмиттерам логарифмирующего и. термокомпенсируйщего транзисторов, выход источника образцового тока соединен с коллектором и базой термокомпенсирующего транзистора и с неинвертирующим входом второго усилителя, между инвертирующим входом и выходом которого включен масштабный резистор, инвертирующий вход второго усилителя через элемент с управляемым коэффициентом передачи соединен с шиной нулевого потенциала, выход второго усилителя является выходом и подключен к инвертирующему входу дифференциального усилителя, к неинвертирующему входу которого присоединен источник опорного напряжения, выход дифференциального усилителя через ключевой элемент соединен с первой обкладкой накопительного конденсатора, вторая обкладка которого подключена к шине нулевого потенциала, выход генератора тактовых импульсов присоединен к управляющему входу ключевого элемента, рдин вывод токозадающего резистора соединен с входом логарифмирующего устройства, иеинвертирующий вход первого усилителя подключен к шине нулевого потенциала 2j.

Недостатками известного устройства являются низкое быстродействие и точность, обусловленные необходимостью периодический коррекции логарифмического блока и его значительной мультипликативной ошиб0

Цель изобретения - повышение быстродействия и точности.

Поставленная цель достигается тем, что в логарифмический преобразователь, содержащий генератор управляющих импульсов, основной дифференциальный усилитель, основной элемент с управляемым коэффициентом передачи, введены первый и второй блоки логарифмирования отношения

0 сигналов, первый и второй модуляторы, дополнительные дифференциальный усилитель и элемент с управляемым коэффициентом передачи, первый и второй демодуляторы и сумматор, вы5 ход которого является выходом логарифмического преобразователя, входы первого и второго модуляторов являются соответственно первым и BTopfcOM входами логарифмического

0 преобразователя, выход первого модулятора соединен с первым входом первого блока логарифмирования отношения сигналов, выход которого соединен с входом основного элемен5 та с управляемым коэффициентом

передачи, выход которого подключен .к входу первого демодулятора и к первому входу сумматора, выход второго модулятора соединен с первым

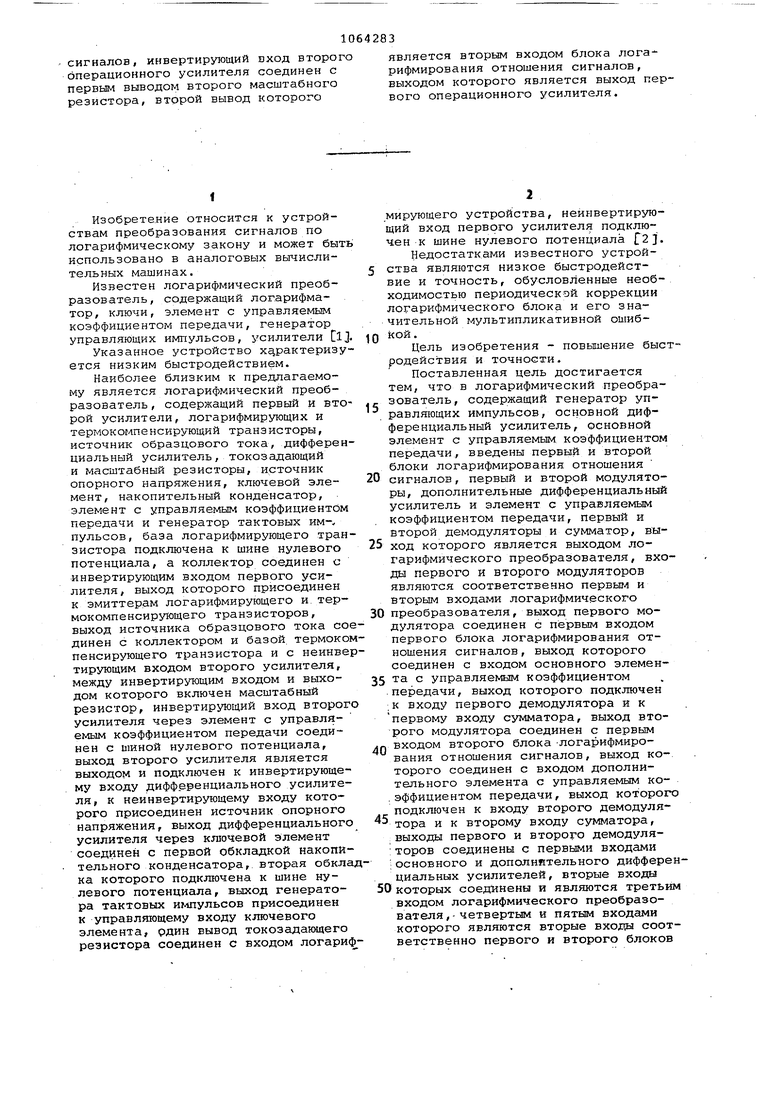

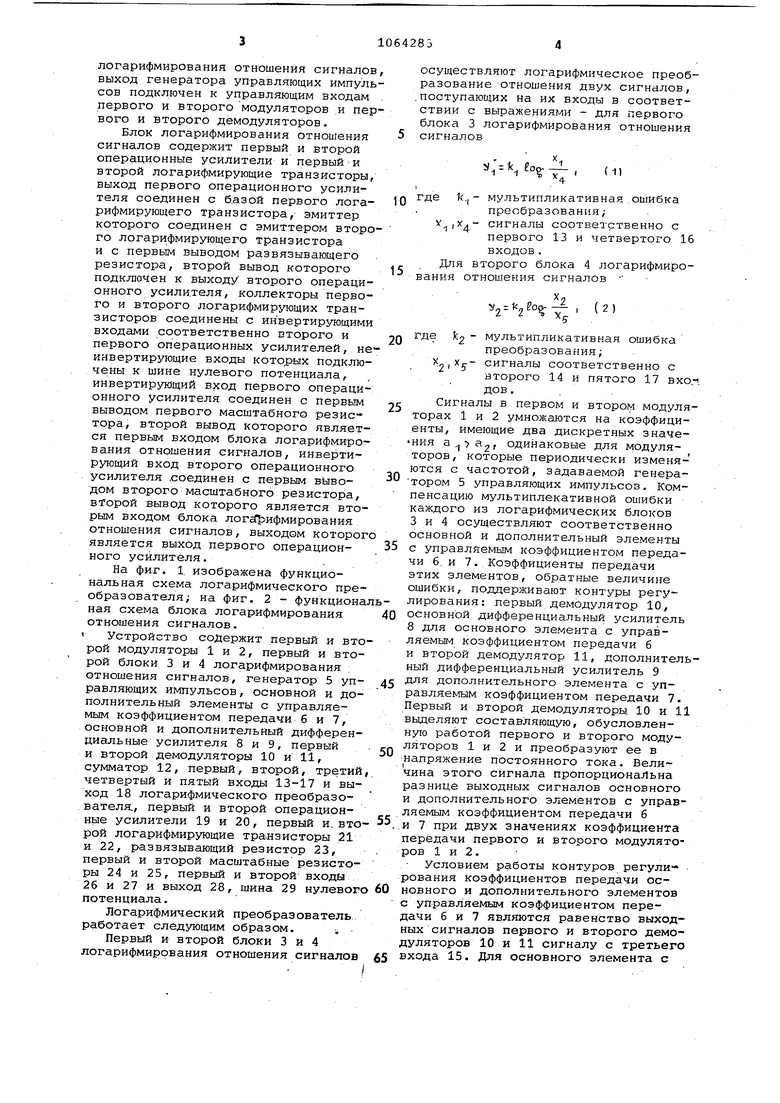

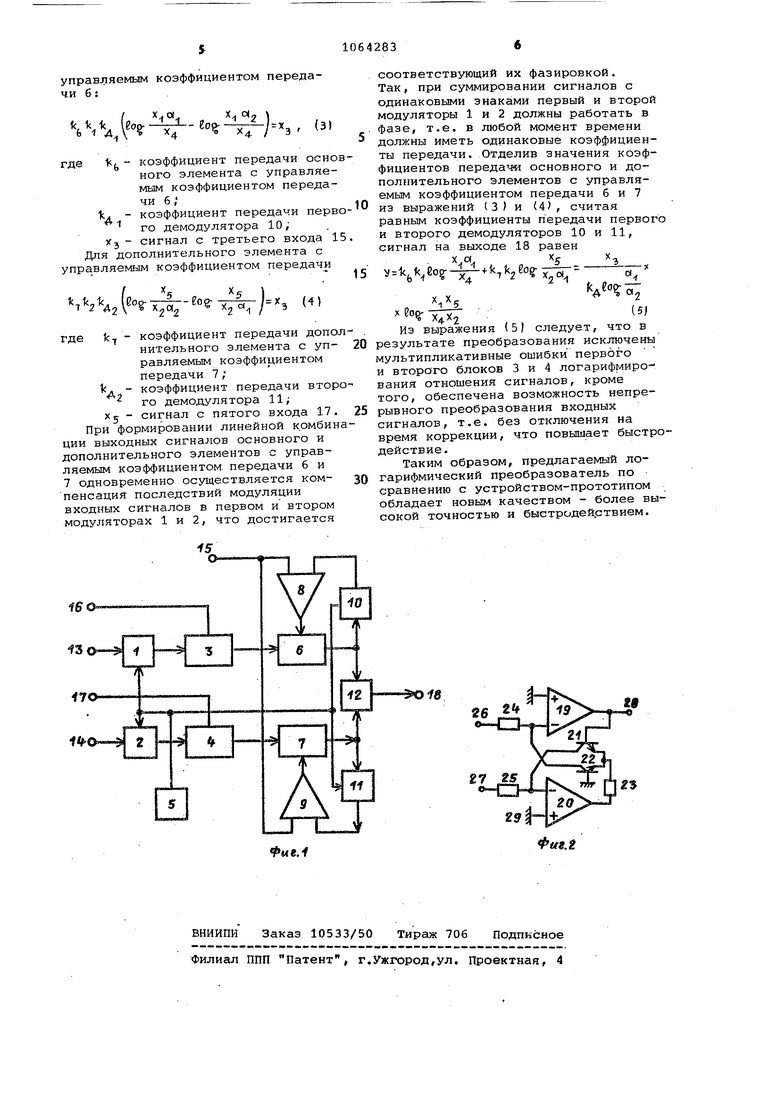

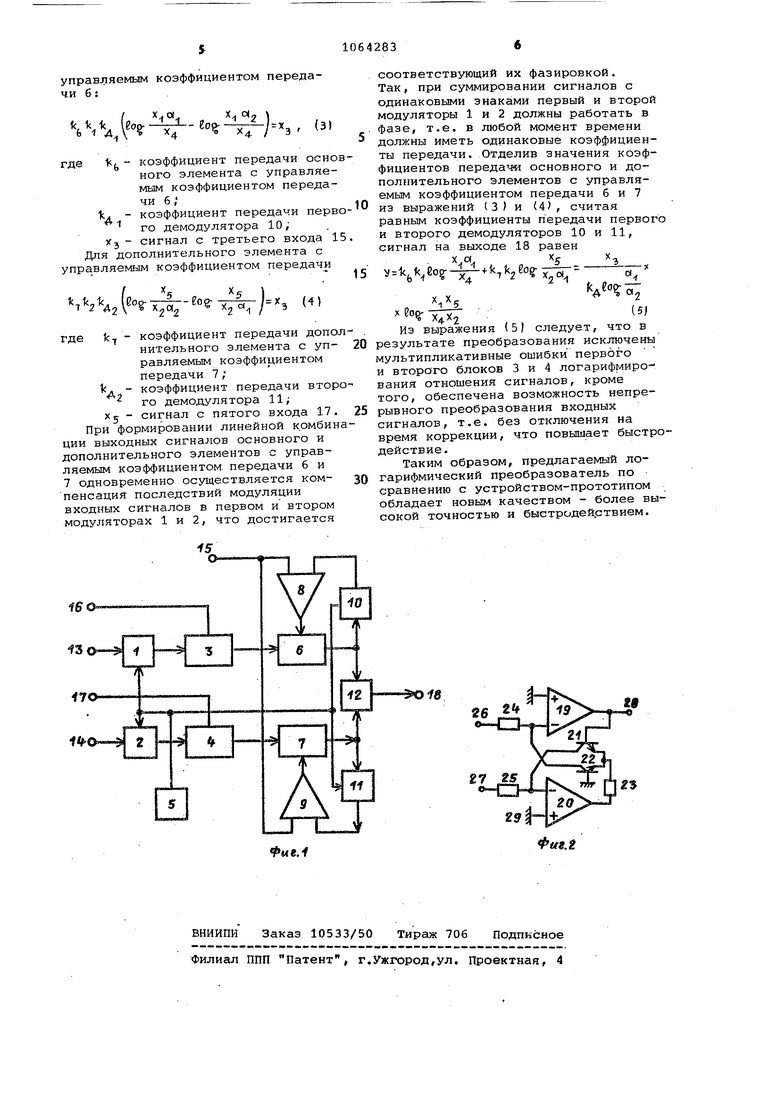

входом второго блока -логарифмирования отношения сигналов, выход которого соединен с входом дополнительного элемента с управляемым ко.эффициентом передачи, выход которого подключен к входу второго демодулятора и к второму входу сумматора, выходы первого и второго демодуля торов соединены с первыми входами :основного И дополнятельного дифференциальных усилителей, вторые входы 0 которых соед11нены и являются третьим входом логарифмического преобразователя,- четвертым и пятым входами которого являются вторые входы соответственно первого и второго блоков логарифмирования отношения сигналов выход генератора управляющих импуль сов подключен к управляющим входам первого и второго модуляторов и пер вого и второго демодуляторов. Блок логарифмирования отношения сигналов содержит первый и второй операционные усилители и первый-и второй логарифмирующие транзисторы выход первого операционного усилителя соединен с б.азой первого лога рифмирующего транзистора, эмиттер которого соединен с эмиттером втор го логарифмирующего транзистора и с первым выводом развязывающего резистора, второй вывод которого подключен к выходу второго операци онного усилителя, коллекторы перво го и второго логарифмирующих транзисторов соединены с инв ер тирующим входами соответственно второго и первого операционных усилителей, н инвертирующие входы которых подклю чены к щине нулевого потенциала, инвepтиps ciщий вход первого операци онного усилителя соединен с первым выводом первого масштабного резис тора, второй вывод которого является первым входом блока логарифмирования отношения сигналов, инвертирующий вход второго операционного усилителя .соединен с первым выводом второго масштабного резистора, второй вывод которого является вторым входом блока логфифмирования отношения сигналов, выходом которог является выход первого операционного усилителя. На фиг. 1. изображена функциональная схема логарифмического преобразователя; на фиг, 2 - функциона ная схема блока логарифмирования отношения сигналов. Устройство содержит первый и вто рой модуляторы 1 и 2, первый и второй блоки 3 и 4 логарифмирования ; отношения сигналов, генератор 5 управляющих импульсов, основной и дополнительный элементы с управляемым коэффициентом передачи б и 7, основной и дополнительный дифференциальные усилителя 8 и 9, первый и второй демодуляторы 10 и 11, сумматор 12, первый, второй, третий четвертый и пятый входы 13-17 и выход 18 логарифмического преобразователя., первый и второй операционные усилители 19 и 20, первый и.вто рой логарифмирующие транзисторы 21 и 22, развязывающий резистор 23, первый и второй масштабные резисторы 24 и 25, первый и второй входы 26 и 27 и выход 28, шина 29 нулевог потенциала. Логарифмический преобразователь работает следующим образом. Первый и второй блоки 3 и 4 логарифмирования отношения сигналов . осуществляют логарифмическое преобразование отношения двух сигналов, .поступающих на их входы в соответствии с выражениями - для первого блока 3 логарифмирования отноитения сигналов /.:fe 00- - Ч X, где 1., - мультипликативная .ошибка преобразования; у сигналы соответственно с первого 13 и четвертого 16 входов. Для второго блока 4 логарифмирования отношения сигналов где - мультипликативная ошибка преобразования; Х„ I Xg-- сигналы соответственно с второго 14 и пятого 17 вхол Сигналы в первом и втором модуляторах 1 и 2 умножаются на коэффициенты, имеющие два дискретных значения одинаковые для модуляторов, которые периодически изменяются с частотой, задаваемой геиератором 5 управляющих импульсов. Компенсацию мультиплекативной ошибки каждого из логарифмических блоков 3 и 4 осуществляют соответственно основной и дополнительный элементы с управляемым коэффициентом передачи 6. и 7. Коэффициенты передачи этих элементов, обратные величи }е ошибки, поддерживают контуры регулирования: .первый демодулятор 10, основной дифференциальный усилитель 8 для основного элемента с управляемым коэффициентом передачи 6 и второй демодулятор 11, дополнительный дифференциальный усилитель 9 для дополнительного элемента с управляемым коэффициентом передачи 7. Первый и второй демодуляторы. 10 и 11 выделяют составляющую, обусловленную работой первого и второго модуляторов 1 и 2 и преобразуют ее в напряжение постоянного тока. Величина этого сигнала пропорциональна разнице выходных сигналов основного и дополнительного элементов с управляемым коэффициентом передачи 6 и 7 при двух значениях коэффициента передачи первого и второго модуляторов 1 и 2. Условием работы контуров регулирования коэффициентов передачи основного и дополнительного элементов с управляемым коэффициентом передачи 6 и 7 являются равенство выходных сигналов первого и второго демодуляторов 10 и 11 сигналу с третьего входа 15. Для основного элемента с

fSO

fSo-

-fto

ue.i

26 2

Фие.г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для логарифмированияОТНОшЕНия дВуХ СигНАлОВ | 1979 |

|

SU822210A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Логарифмирующее устройство | 1979 |

|

SU809230A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-30—Публикация

1982-06-23—Подача