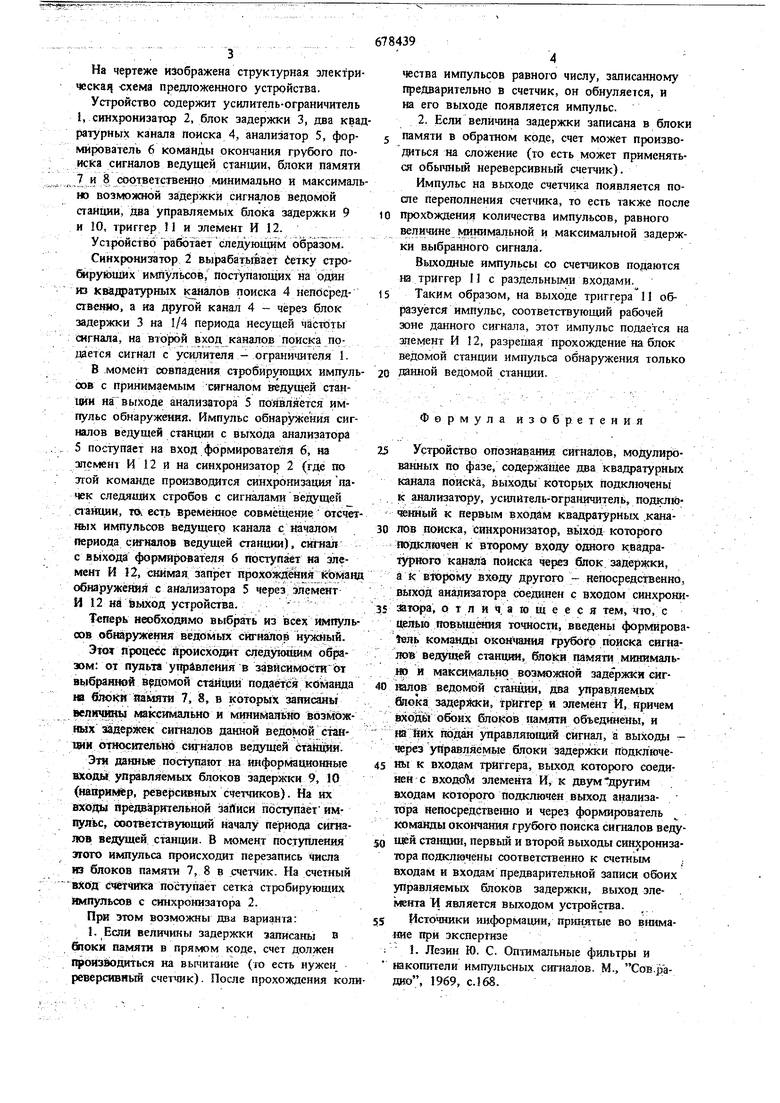

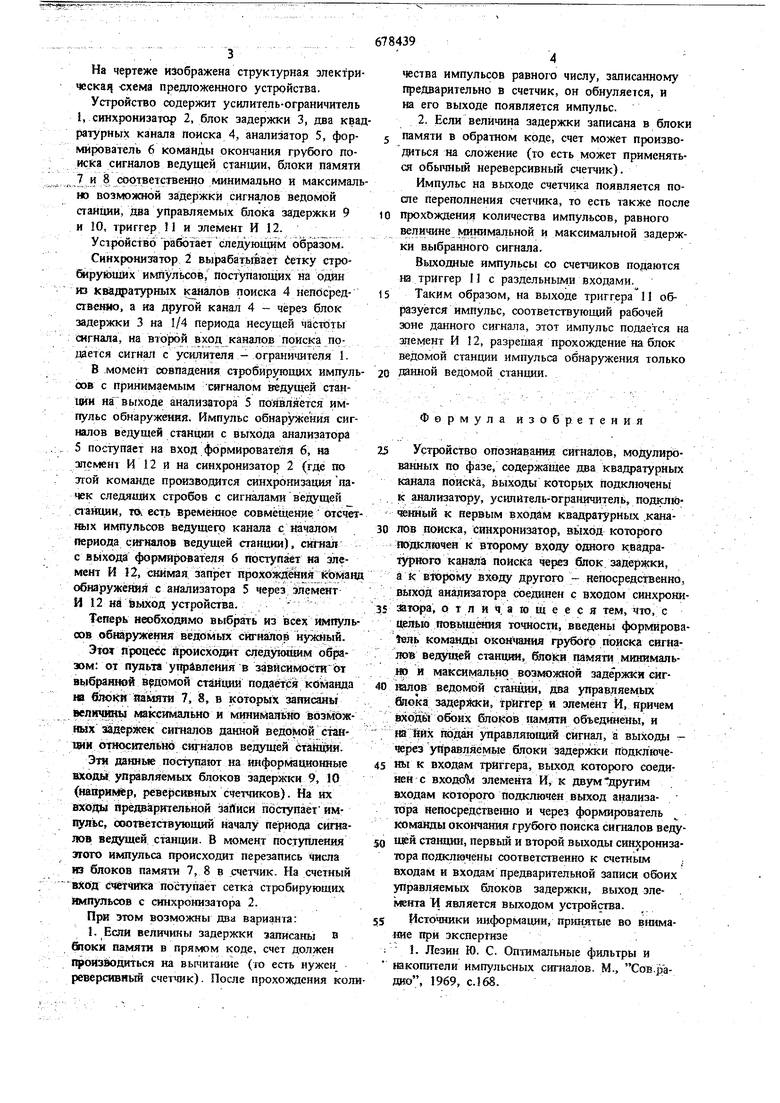

(54) УСТРОЙСТВО ОПОЗН Изобретение опюсится к радиотехнике и лдажет использоваться для обнаружения сигнало при определении местоположения подвижных объектов по импуяьсно-фазовой радионавигационной системе. Известно устройство опознавания сигналов, людулированных по фазе, содержащее два квадратурных канала поиска, выходы которых подключены к анализатору, усилитель-ограничитель, подключенный к первым входам квадратурных каналов поиска, синхронизатор, выход которого .подключен к второму входу одн го квадратурного канала поиска через блок за держки,, а к второму входу другого непосредшвенно, выход анализатора соединен с входом отнхронизатора 1 . Однако известное устройство имеет невысокую точность. Цель изобретения - повышение точности. Для этого в устройство опоз 1ава1шя сишалов, модулированнь Х по фазе, содержащее два квадра1урных канала поиска, выходы которых 1юдключены к анализатору, усилитель-ограничитель, иодключе1юь Й к первым входам квадПО Ф Я СИГНАЛОВ, МОДУЛИРОВАННЫХ ратурных каналов поиска, синхронизатор, выход которого подключен к второму входу одного квадратурного канала поиска через блок задержки, а к второму входу другого - не- посредственно, выход анализатора соединен с входом Синхронизатора, введены формирователь команды окончания грубого поиска сигналов ведущей станции, блоки памяти минимально и максимально возгуюжнрй задержки отгналов ведомой станции, два управляемых блок-а задержки, триггер и элемент И, причем входы обоих блоков памяти объединены, и на них ггодан управляющий сигнал, а выходы через управляемые блоки задержки подключены к входам триггера, выход которого соединен с входом элемента И, к двум лругим входам которого подключен выход анализатора непосредственно и через формирователь команды окончания грубого поиска сигналов ведущей станций, первый и второй выходы синхртнизатора подключены соответственно к счетным входам и входам предварительной записи обоих управляемых блоков задержки, выход -jjteMeirra И является выходом устройова. На чертеже изображена структурная электри ческщ -схема предложенного устройства. Устройство содержит усилитель-ограничитель 1, синхронизатор 2, блок задержки 3, два ква ратурных канала поиска 4, анализатор 5, формирователь 6 команды окончания грубого поиска сигналов ведущей станции, блоки памяти 7 и 8 соответственно минимально и максимал ю возможной задержки сигналов ведомой станции, два управляемых блока задержки 9 и 10, триггер 11 и элемент И 12. Устройство ра&таёт следующим оёразом. Синхронизатор 2 вырабать1вает Сетку стро1йиру1оишх и myльcoв, поступающих на один из квадратурных каналов поиска 4 непосредственно, а на другой канал 4 - через блок задержки 3 на 1/4 периода несущей частоты сигнала, на второй вход каналов поиска подается сигнал с усилителя - ограничителя 1. В .момент совпадения стро6ир5тощих импуль сов с принимаемым сигналом ведущей стандам на выходе анализатора 5 появляется иМпульс обнаружений. Импульс обнаружения сиггешов ведущей станвди с выхода анализатора 5 поступает на вход формирователя б, на зпеменг И 12 и на синхронизатор 2 (где по этой команде производатся синхронизация пачек следящих стробов с сигналами ведущей аанции, та есть временное совмещение отсчет iftix импульсов ведущего канала с началом периода сигналов ведущей станции), сигнал с выхода формирователя 6 поступггет на элемент И 12, снимая запрет прохожйёйия шшад обнаружёгшя с анализатора 5 через элемент И 12 ни выход устройства. Теперь необходамо выбрать из всех оов обнаружения ведомых сигналов . Этот процесс йроисходат следутащим образом: от пульта управления в зависимостиот выбрашюй ведомой стандан подаётся команда ш блоки яайяти 7, 8, в которых записаны величины максимально и минимально вдэшжных задержек сишапов данной ведомой стайвди относйтельнй сигналов ведущей ctaJni. Эти даннью поступают на информационные входы управляемых блоков задержки 9, Ю (HanpHN p, реверсивных счетчиков). На их ВХОДЫ ирёгшарктельной зайиси поступает , соответствующий началу периода сигналов ведшей стал ЦИК- В момент поступления этого импульса происходит перезапись числа ю блоков памяти 7, 8 в .счетчик. На счетный вход счётгчика поступает сетка стробирующих Импульсов с синхронизатора 2. III этом возможны два варианта: 1. Если величины задержки записаны в блоки памяти в прямом коде, счет должен пршзЁодиться на вычитание (го есть нужен реверсивный счетчик). После прохождения кол чества импульсов равного числу, записанному предварительно в счетчик, он обнуляется, и на его выходе появляется импульс. 2. Если величина задержки записана в блоки памяти в обратном коде, счет может производиться на сложение (то есть может применяться обьпшый нереверсивный счетчик). Импульс на выходе счетчика появляется после переполнения счетчика, то есть также после прохождения количества импульсов, равного величине минимальной и максимальной задержКи выбранного сигнала. Выходные импульсы со счетчиков подаются на триггер 11 с раздельными входами. Таким образом, на выходе триггера 11 образуется импульс, соответствующий рабочей зоне данного сигнала, этот импульс подается на элемент И 12, разрещая прохождение на блок ведомой станции импульса обнаружения только данной ведомой станции. Фермула изобретения Устройство опознавания сигналов, модулированных по фазе, содержащее два кващ)атурных канала пояска, выходы которых подключень к анализатору, усшйтель-ограгдаштель, подклйченный к первым вхОдйм квадратурных .кашлов поиска, синхронизатор, выход которого {юделючен к второму входу одного квадратурного канала поиска через блок задержки, а к второму входу другого - непосредственно, выход анализатора соединен с входом синхронизатора, отличающееся тем, что, с целью повышения точности, введены форлшрова11ель команды окончаюй грубого поиска сигналов ведущей стакцш, оки памяти мннимальш и максимально возможной задеряжи сигшлов ведомой станции, два управляемых &ioka задерАки, триггер и элемент И, причем входи обоих блокЬв памяти объединены, и ка;1|йх пбдан управляющий сигнал, а выходы чере:з управляемые блоки задержки пЬдключены к входам триггера, вьгход которого соединен с входо1й элемента И, к двум другим входам которого подключен выход анализатора непосредственно и через формирователь команды окончания грубого поиска сигналов ведушей сташщи, первый и второй выходы синхронизатора подклнзченьг соответственно к счетным : входам и входам предварительной записи обоих управляемых блоков задержки, выход элемента И является выходом устройства. Источники информации, принятые во внимание при экспертизе . Лезин Ю. С. Оптимальные фильтры и шкопители импульсных сигналов. М., CoB.jjaдио, 1969, С.168.

ffmnyatfrA Упра§/Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство опознавания сигналов, модулированных по фазе | 1988 |

|

SU1518810A2 |

| Устройство опознавания сигналов, модулированных по фазе | 1977 |

|

SU656003A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ В УСЛОВИЯХ ПОМЕХ | 1991 |

|

RU2030757C1 |

| Система синхронизации пространственно разнесенных часов | 1985 |

|

SU1299335A1 |

| Устройство для измерения временных интервалов в условиях помех | 1976 |

|

SU642655A2 |

| Устройство для зондирования ионосферы | 1990 |

|

SU1742762A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1979 |

|

SU1840444A1 |

| Многоканальный интерфейс | 1990 |

|

SU1751774A1 |

| ПРИЕМОПЕРЕДАЮЩАЯ АППАРАТУРА ШИРОКОПОЛОСНЫХ ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 1979 |

|

SU1840119A1 |

| ВЕДОМСТВЕННАЯ СИСТЕМА ДВУХСТОРОННЕЙ ВЫСОКОСКОРОСТНОЙ РАДИОСВЯЗИ С ЭФФЕКТИВНЫМ ИСПОЛЬЗОВАНИЕМ РАДИОЧАСТОТНОГО СПЕКТРА | 2016 |

|

RU2650191C1 |

Авторы

Даты

1979-08-05—Публикация

1977-12-29—Подача