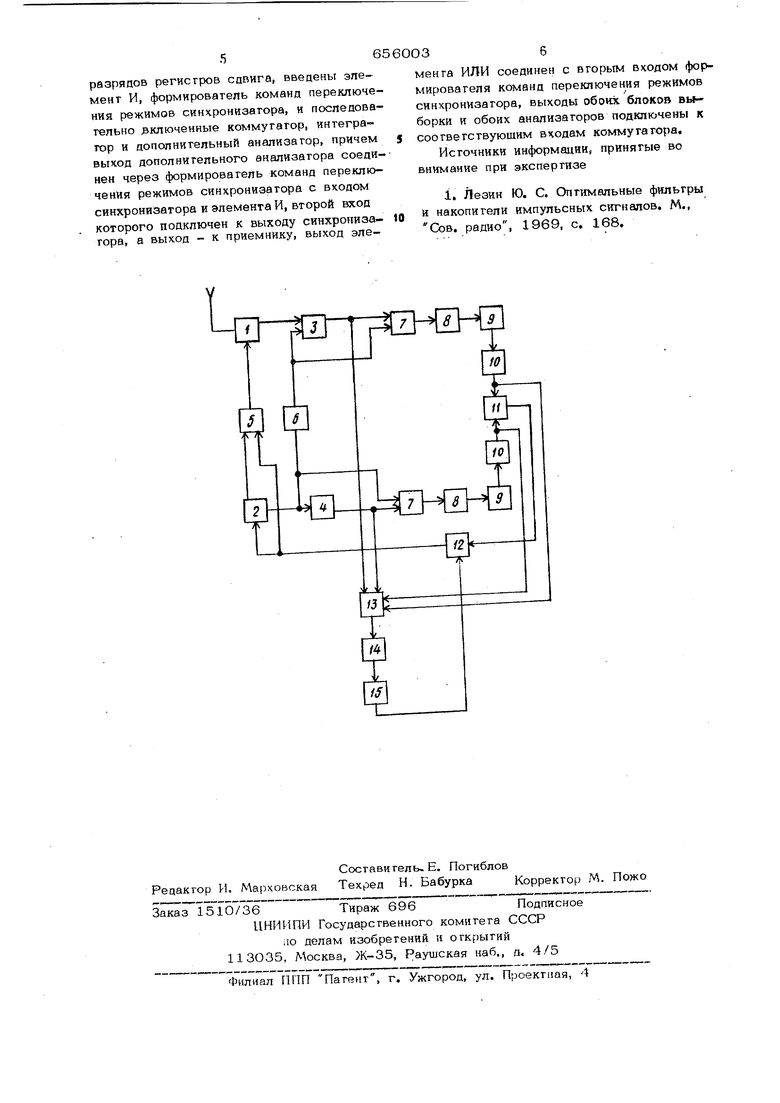

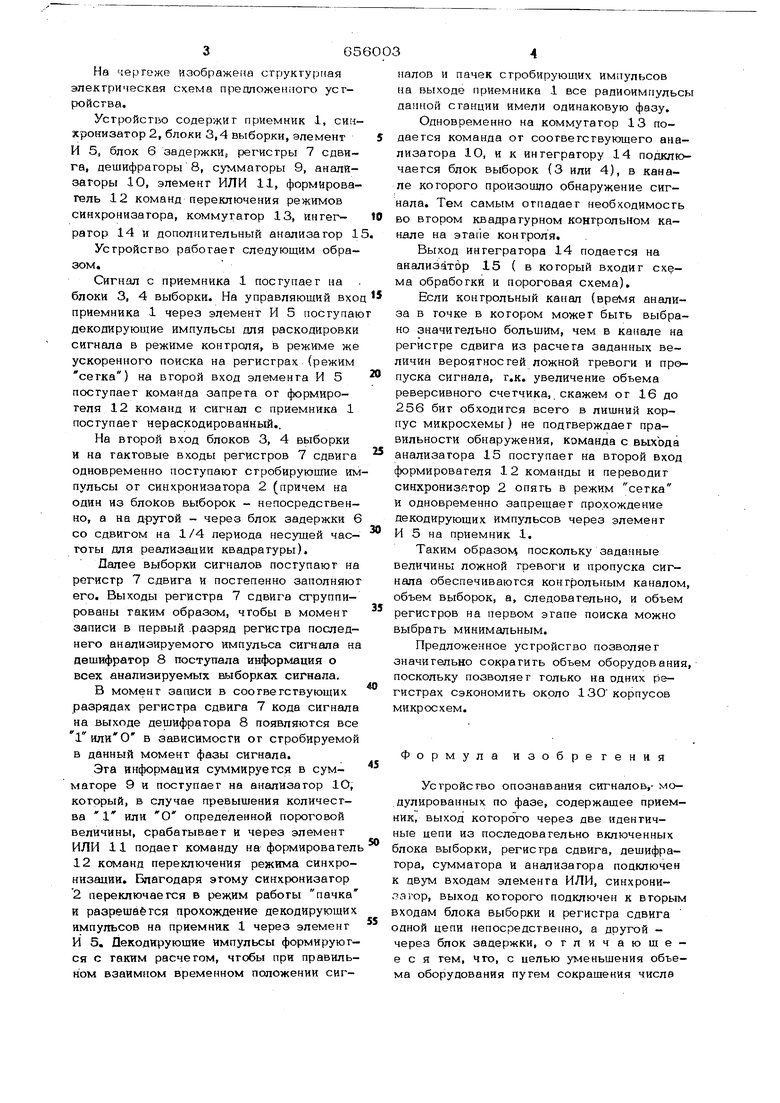

Изобретение относится к радиотехнике и можег использоваться для обнаружения сигналов при определении места положения подвижных, объектов. Известно устройство опознавания сигналов, модулированных по фазе, содержащее приемник, выход которого через две идентичные цепи из последовательно вклю ченных блока выборки, регистра сдвига, дешифратора, сумматора и анализатора подключен к двум входам элемента ИЛИ, синхронизатор, выход которого подключен к вторым входам блока выборки и регист ра сдвига одной цепи непосредственно, а друтхэй - через блок задержки ij . Однако это устройство имеет значительный объем оборудования. Цель изобретения - уменьшение объем оборудования путем сокращения числа раз рядов регистров сдбига Для этого в устройство опознавания сигналов, модулированных по фазе, содержащее приемник, выход которого через две идентичные цепи из последовательно включенных блока выборки, регистра сдвига, дешифратора, сумматора и ан 1лизато- ра подключен к двум входам элемента ИЛИ, синхронизатор, выход которого подключен к вторым входам блок выборки и регистра сдвига одной цепи непосредственно, а другой - через блок задержки, введены элемент И, формирователь команд переключения режимов синхронизатора и последовательно включенные коммутатор, интегратор и дополнительный анализатор, причем выход дополнительного анализатора соединен через формирователь команд переключения режимов синхронизатора с входом синхронизатора п элемента И, второй вход которого подключен к выходу синхронизатора, а выход - к приемнику, выход элемента ИЛИ соединен с вторым входом формирователя команд переключе-ния режимов синхронизатора, выходы обоих блоков выборки и обоих анализаторов подключены к соответствующим входам коммутатора. 365 На чертеже изображена струкгургсая электрическая схема препложениого усгройства. Устройство содержит приемник 1, синхронизатор 2, блоки 3,4 выборки, элемент И 5, блок 6 задержки, регистры 7 сдвига, дешифраторы 8, сумматоры 9, анализаторы 10, элемент ИЛИ 11, формирователь 12 команд переключения режимов синхронизатора, коммутатор 13, интегратор 14 и дополнительный анализатор 1 Устройство работает следующим образом. Сигнал с приемника 1 поступает на блоки 3, 4 выборки. На управляющий вхо приемника 1 через элемент И 5 поступаю декодирующие импульсы для раскодировки сигнала в режиме контроля, в режиме же ускоренного поиска на регистрах (режим сетка) на второй вход элемента И 5 поступает команда запрета от формиротеля 12 команд и сигнал с приемника 1 поступает нераскодированный.. На второй вход блоков 3, 4 выборки и на тактовые входы регистров 7 сдвига одновременно поступают стробирующие им пульсы от синхронизатора 2 (причем на один из блоков выборок - непосредственно, а на другой - через блок задержки 6 со сдвигом на 1/4 периода несущей частоты для реализации квадратуры). Палее выборки сигналов поступают на регистр 7 сдвига и постепенно заполняют его. Выходы регистра 7 сдвига сгруппированы таким образом, чтобы в момент записи в первый .разряд регистра последнего анализируемого импульса сигнала на дешифратор 8 поступала информация о всех анализируемых выборках сигнала. В момент записи в соответствующих разрядах регистра сдвига 7 кода сигнала на выходе дешифратора 8 появляются все 1или0 в зависимости от стробируемой в данный момент фазы сигнала. Эта информация суммируется в сумматоре 9 и поступает на анализатор Ю, который, в случае превышения количества I или О определенной пороговой величины, срабатывает и через элемент ИЛИ 11 подает команду на формировател 12 команд переключения режима синхронизации. Благодаря этому синхронизатор 2 переключается в режим работы пачка и разрешается прохождение декодирующих импульсов на приемник 1 через элемент И 5. Декодирующие импульсы формируются с таким расчетом, чтобы при правильном взаимном временном положении сигналов и пачек стробирующих импульсов на выходе приемника 1 все радиоимпульсы данной станции имели одинаковую фазу. Одновременно на коммутатор 13 подается команда от соответствующего анализатора Ю, и к интегратору 14 подключается блок выборок (3 или 4), в канале которого произошло обнаружение сигнала. Тем самым отпадает необходимость во втором квадратурном контрольном канале на этапе контроля. Выход интегратора 14 подается на анализатор 15 ( в который входит схема обработки и пороговая схема). Если контрольный канал (вреЫя анализа в точке в котором может быть выбрано значительно большим, чем в канале на регистре сдвига из расчета заданных величин вероятностей ложной тревоги и пропуска сигнала, т.к. увеличение объема реверсивного счетчика, скажем от 16 до 256 бит обходится всего в лишний корпус микросхемы) не подтверждает правильности обнаружения, команда с выхода анализатора 15 поступает на второй вход формирователя 12 команды и переводит синхронизятор 2 опять в режим сетка и одновременно запрещает прохождение декодирующих импульсов через элемент И 5 на приемник 1. Таким образом поскольку заданные величины ложной тревоги и пропуска сигнала обеспечиваются контрольным каналом, объем выборок, а, следовательно, и объем регистров на первом этапе поиска можно выбрать минимальным. Предложенное устройство позволяет значительно сократить объем оборудования, поскольку позволяет только на одних регистрах Сэкономить около 130корпусов микросхем. Формула изобретения Устройство опознавания сигналов,- модулированных по фазе, содержащее приемник, выход которого через две идентичные цепи из последовательно включенных блока выборки, регистра сдвига, дешифратора, сумматора и анализатора подключен к двум входам элемента ИЛИ, синхронизатор, выход которого подключен к вторым входам блока выборки и регистра сдвига одной цепи непосредственно, а другой через блок задержки, отличающееся тем, что, с целью y eньщeния объема оборудования путем сокращения числа разрядов регистров сцвига, введены элемент И, формирователь команд переключения режимов синкрониэатора, и последовательно включенные коммутатор, интегратор и дополнительный анализатор, причем выкод дополнительного анализатора соединен через формирователь команд переключения режимов синхронизатора с входом синхронизатора и элемента И, второй вход которого подключен к выходу синхронизатора, а выход - к приемнику, выход эле6036 мекга ИЛИ соединен с вторым входом формирователя команд переключения режимов синхронизатора, выходы обоих блоков выборки и обоих анализаторов подключены к соответствующим входам коммутатора. Источники информации, принятые во внимание при экспертизе 1. Лезин Ю. С. Оптимальные фильтры и накопители импульсных сигналов, М., Сов. радио, 1969, с. 168,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство опознавания сигналов, модулированных по фазе | 1988 |

|

SU1518810A2 |

| Устройство для пердачи и приема командных псевдослучайных последовательностей | 1977 |

|

SU655083A1 |

| Цифровая система связи с исправле-НиЕМ ОшибОК | 1979 |

|

SU818024A1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

| Система передачи и приема дискретной информации | 1983 |

|

SU1119184A1 |

| Устройство для коммутации каналов передачи данных | 1987 |

|

SU1434557A1 |

| УСТРОЙСТВО ДЛЯ ПУСКА РАКЕТ | 1981 |

|

RU2121647C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство опознавания подвижных объектов | 1985 |

|

SU1355985A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

Авторы

Даты

1979-04-05—Публикация

1977-11-28—Подача