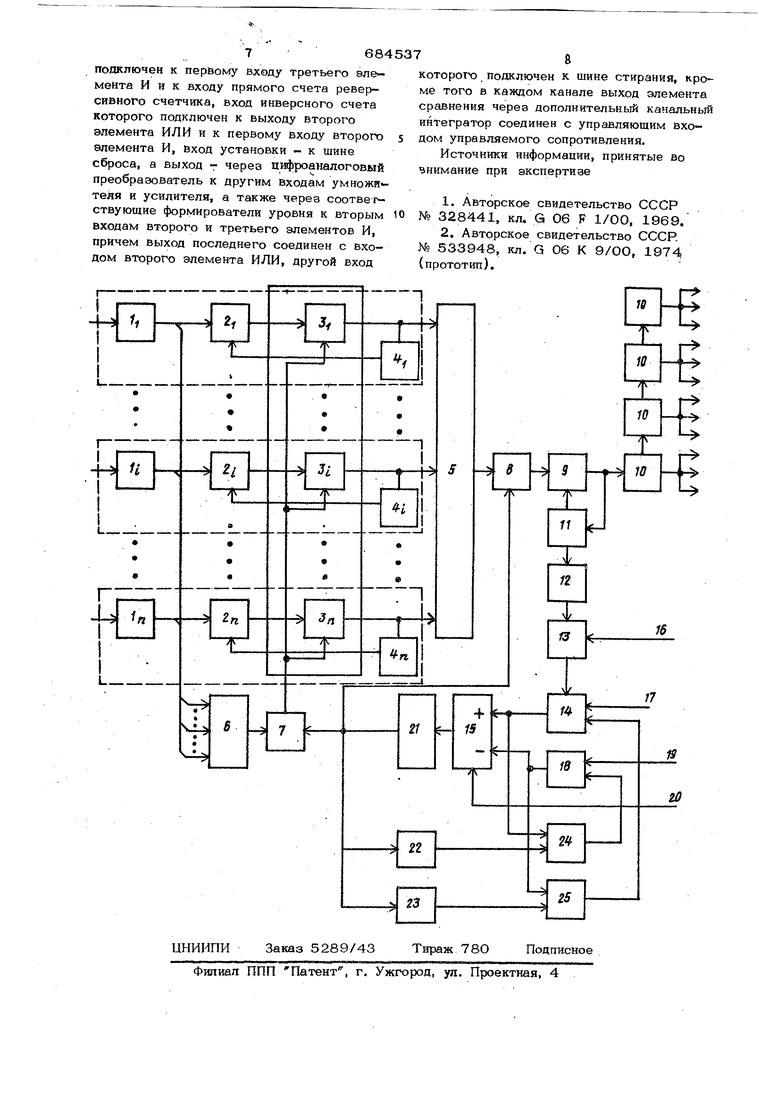

Изобретение касается автоматики и вычислительной техники и может быть при менено как элемент однородной вычислительной среды. Известна ячейка однородных настраиваемых структур, содержащая логический, элемент, блок памяти и адресный блок, в которой логический элемент может настраиваться на выполнение одной или нескольких функций из заданного набора логических функций 111 . Недостатком этой ячейки является то, что настройка ее Может быть осуществлена только с помощью внешних управляющих устройств, в частности 11ВМ или запоминающих устройств, что сужает функциональные возможности устройства. Известны также ячейки ассоциативной среды, содержащие каналы из соединенных последовательно канальных интеграторов, управляемых сопротивлений и элементов сравнения, а также сумматоры, логические элементы, счетчик, преобразователи, усилитель и умножитель 121 . Недостатками этих ячеек являются большое число внешних выводов из-за парности входных и выходных контактов, погрешности записанного значения аналоговой памяти из-за подверженности утечки заряда во времени, невозможность оперативного стирания записанной информации в памяти и невозможность, изменения динамического ди&пазона постоянных интегрирования. . Цель изобретения - уменьшение ввегиних выводов и расширение функциональных Боаможностей. Для этого в ячейке ассоциативной среды, содержащей сумматор, каждый иа входов которого соединен с соответствующей информационной входной шиной через канал, состодаций из последовательно соединенных канального интегратора, управляемого сопротивления и элемента сравнения, а выход сумматора подключен к входу умножителя, выход которого соединен с перым входом преобразователя напряжения в частоту, второй вход которого соединен с 36 выходом интегратора, а выход преобразователя напряжения в частоту через цепоч ку из последовательно соединенных форми рователей подключен к выходным шинам, выходы канальных интеграторов черва дополнителькый сумматор также подключены к одному из входов усилителя, выход которого соединен с другими входами элементов сравнения, и дополнительные канальные интеграторы, триггер Шмитта, тр элемента И, два элемента ИЛИ, два формирователя уровня, реверсивньй счетчик и оифро-аналоговый преобразователь, дру гой выход интегратора через триггер Шмитта соединен с первым входом перво Го элемента И, второй вход которого под ключен к шине записи, а выход - к первому входу первого элемента ИЛИ, второ вход которого соединен с шиной запоминания, а третий- с выходом второго элемента И. Выход первого элементаИЛИ подключен к первому входу третьего элемента И И к входу прямого счета реверсивного счетчика, вход инверсного счета которого подключен к выходу второго элемента ИЛИ и к первому входу второго элемента И, вход установки - к шине сброса, а выход - через цифро-аналоговый преобразователь, к другим входам -умножителя и усилителя, а также через соответствующие формирователи уровня ,к втормм входам второго и третьего элементов И, причем выходпослед него соединен с входом Второго элемента ИЛИ, другой вход которого подключен к шине стирания, кроме того, в каждом канале выход элемента сравнения через дополнительный канальньй интегратор соединен с управляющим входом управляемого сопротивления. На чертеже представлена структурная схема предложенного устройства. Каждый канал устройства срдержнт интегратор 1, управляемые сопротивления 2, элемент сравнения 3 и канальньй интегратор 4. Выходы элементов сравнения 3 подключены к сумматору 5, а выходы интеграторов 1 - к сумматору 6 и. через усилитель 7 - к соответствующим элемен там сравнения 3. Выход сумматора 5 под ключен к первому входу умножителя 8, который через преобразователь 9 напряжения в частоту соединен последователь йо цепочкой формирователей 10 выходных импульсов, каждый из которых соединен с выходными шинами. Выход интегратора 11 последовательно через триггер Шмитта 12, элемент И 13 и элемент ИЛИ 14 7 соединен с входом сложения реверсивного счетчика 15. Управляющий вход элемента И 13 подключен к шине Записи 16, а второй вход элемента ИЛИ 14 - к шине запоминания 17, Вычитающий вход реверсивного счетчика 15 соединен через элемент ИЛИ 18 с шиной стирания 19, а вход установки реверсивнрго счетчика 15 соединен с шиной сброса 20. Выход реверсивного счетчика 15 подключен к входу цифро-аналогового преобразователя 21, выход которого соединен с вторыми вхо- Цами умножителя 8 и усилителя 7, входами формирователей уровня 22 и 23. Входы элемента И 24 подключены к выходу фор мирователя уровня 2.2 и к выходуэлемента ИЛИ 14, а выход соединен с входом элемента ИЛИ 18. Выход формирователя уро&ня 23 через элемент И 25 подключен к входу элемента ИЛИ 14, а другой вход элемента И 25 соединен с выходом элемента ИЛИ 18. Работа ячейки происходит следующим образом. Входной поток импульсов поступает через канальные интеграторы 1, управляемые сопротивления 2 и элементы сравнения 3 На сумматор 5. Входные импульсы ; интегрируются с постоянной времени f в канальном интеграторе 1. В зависимости от интенсивности входного потока импульсов по какому-либо каналу накапливается постоянная составляющая в дополнительном интеграторе 4 при постоянной времени интегратора i являющейся в данном случае кратковременной памятью интенсивности сигнала по данному входу ячейки, которым управляется коэффициент передачи сигнала по этому входу, В допапнительномсу мматоре 6 с постоянной времени заряда и разряда t 4ii fj суммируются входшле сигналы со всех входбв ячей- . ки и через усилитель 7 поступают на все элементы сравнения 3, последними выделяются каналы с максимальными сигналами. Таким образом, в элементе сравнения 3 срезается по амплитуде (уровню интенсивности) входной сигнал по каждому каналу в зависимости от общей интенсивности входного потока на всех входах ячейки. На сумматор 5 поступают сигналы с входов, где произошло превышение сигнала относительно других входов. Про суммированный аналоговый сигнал с сумматора 5 с постоянной времени ступает в умножитель 8 и умножается на аналоговое значение напряжения, считываемого с цифро-аналогового преобра- зователя (ЦАП) 21, и далее поступает в преобразователь 9 напряжения в частоту Преобразование напряжения в частоту WMлульсов происходит с учетом обратной связи, поступающей от интегратора 11. Постоянная времени интегратора 11 TS Z . Эта отрицательная обратная связь формирует адаптацию по выходному сигналу. Импульсы с преобразователя 9 напряжения в частоту стандартизируются по амплитуде и длительности в формирователе 10 выходных импульсов, причем каждый последуюп1ий формирователь 10 в цепочке формирует импульсы, задержанны на величину длительности импульса. Задержки необходимы для учета эффективного действия ячеек в среде ко времени. Триггер Шмитта 12 формирует периоды наиболее интенсивной импульсации ячейки Сформированньй импульс с триггера Шми та 12 через элемент И 13 и элемент ИЛИ 14 поступает на прямой вход реверсивного счетчика 15. При наличии потенциального сигнала (разрешение на запись) На коммутирующей шине записи 16 этот имПульс проходит через элементы И 13 и ИЛИ 14 в реверсивный счетчик 15. В реверсивный счетчик 15 могут быть записаны импульсы также извне по шине запоминания 17 через элемент ИЛИ 14. Стирание значений .с реверсивного счетчика 15 в динамическом-режиме рабо ты происходит подачей импульсов стирания по шине стирания 19 через элемент ИЛИ 18 на инверсный вход реЕ ерсивного счетчика 15. :Количественные значения активной генерации ячейки записанные в реверсивном счетчике 15 преобразуются в аналоговую форму в ЦАП 21 и поступают в умножитель 8. Этим производится сопряжение характеристики преобразователя ячейки с предисторией его активностей. Аналоговое напряжение с ЦАП 21 постуЛает на второй вход усилителя 7 и управляет его коэффициентом усиления (для.уменьшений числа выделяемых каналов с максимальными интенсивностямя сигналов), а также поступают на формирователи уровня 22 и 23. Формирователи уровня 22 .и 23, а также элементы И 24 ,и 25 предназначены для предотвращения переполнения реверсивного счетчика 15 и предохранения от перестирания и потери информации. Формирователь уровня 22 срабатыв ает и выдает на выходе потенциал 1 при значении аналоговой величины на выходе ПАП 21, превышающей, например 95% от максимального его значения. При этом на элемент И 24 поступаегг разрешающий потенциал и импульсы с выхода элемента ИЛИ 14, поступающие на суммирующий вход реверсивного счетчика 15 и на вход элемента И 24, с выхода его через элемент ИЛИ 18 Поступают на инверсный вход реверсивного счетчика 15. Формирователь уровня 23 срабатывает при значении аналоговой величины напряжения на выходе ЦАП 21 меньшем 5% от его максимального значения. с выхода формирователя уровня 23 на элемент И 25 поступает разрешающий . потенциал .1 и с выхода элемента ИЛИ 18 импульсы через элементы И 25 и ИЛИ 14, поступают напрямой вход реверсивного счетчика 15. Таким образом в предложенной ячейке оперативно управляется npduecc,еаписи и стирания в реверсивньй счетчик 15 однородной срецы в процессе функционирования. Формула изобретения Ячейка ассоциативной среды, содержащая сумматор, каждый из входов которого соединен с соответствующей информационной входной ШИНОЙ через канал, состоящий из последовательно соединенных канального интегратора, управляемого сопротивления и элемента сравнения, а выходы сумматора подключены к входу умножителя, выход которого соединен с перзым входом преобразователя напряжения в Частоту, второй вход которого соединен с выходом интегратора, а выход преобразователя напряжения в частоту через цепочку из последовательно соединенных формирователей подключен к выходным шинам, выходы канальных интеграторов через дополнительный сумматор также подключены к одному из входов усилителя, выход которого соединен с другими входами элементов сравнения, и дополнительные каналы интеграторы, триггер Шмитта, три элемента И, два элемента ИЛИ, два формирователя уровня, реверсивньй счетчик и цифро-аналоговьй преобразователь, о т л и ч а ю щ а я с я тем, что, с целью уменьшения внешних выводов и расширения функциональных возможностей, другой выход интегратора черев триггер Шмитта соединен с первым входом первого элемента И, второй вход которого подключен к шине записи, а выход к первому входу первого элемента ИЛИ, второй вход которого соединен с , шиной запоминания, а третий - с выходом второго элемента И, при этом выход первого элемента ИЛИ подключен к первому входу третьего элемента И и к входу прямого счета реверсивного счетчика, вход инверсного счета которого подключен к выходу второго элемента ИЛИ и к первому входу второго элемента И, вход установки - к шине сброса, а выход - через цифроаналоговый преобразователь к другим входам умножи теля и усилителя, а также через соотвег- ствующие формирователи уровня к вторым входам второго и третьего элементов И, причем выход последнего соединен с входом второго элемента ИЛИ, другой вход 684 которого подключен к шине стирания, кроме того в каждом канале выход элемента сравнения через дополнительный канальный интегратор соединен с управляюшим входом управляемого сопротивления. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР J-. ло1и л--ло« ииидетельство С.ииЬ № 328441, кл. G 06 F 1/00 1969 2. Авторское свидетельство СССР. № 533948, кл. Q Об К 9/00, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Устройство сравнения мощности случайных сигналов | 1989 |

|

SU1707550A2 |

| Устройство для считывания графической информации | 1987 |

|

SU1564661A1 |

| Программируемый трансверсальный фильтр | 1988 |

|

SU1651354A1 |

| Устройство для измерения частоты | 1979 |

|

SU813291A1 |

| Устройство для приема сигналов, закодированных с избыточностью | 1988 |

|

SU1605275A2 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛЫ ВРЕМЕНИ | 2014 |

|

RU2552605C1 |

| Частотно-импульсное устройство преобразования сигнала с мостового датчика | 1986 |

|

SU1383474A1 |

| Устройство для определения частоты основного резонанса головки громкоговорителя | 1985 |

|

SU1415471A1 |

Авторы

Даты

1979-09-05—Публикация

1976-01-29—Подача