Изобретение относится к технике связи, может быть- использовано в системах передачи данных и является усовершенствованием устройства по авт.св. № 1265827.

Цель изобретения - повышение достоверности приема информации за счет двухкратного повторения передаваемой информации и более полного использования избыточности сообщений

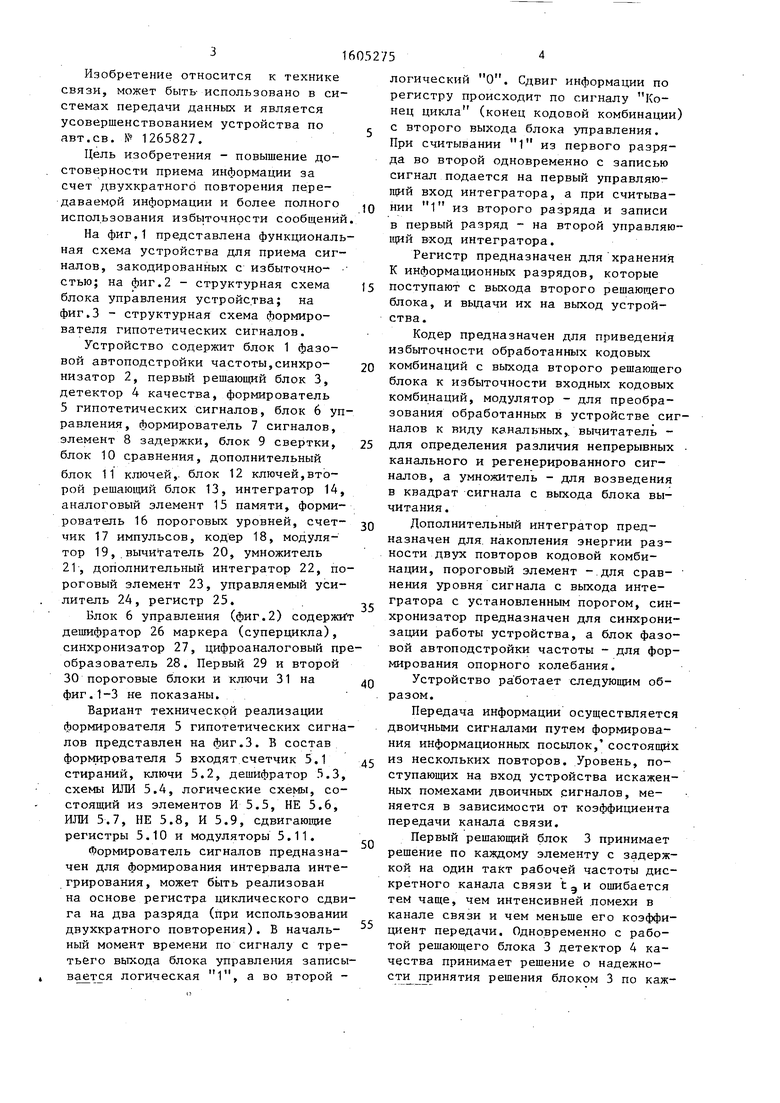

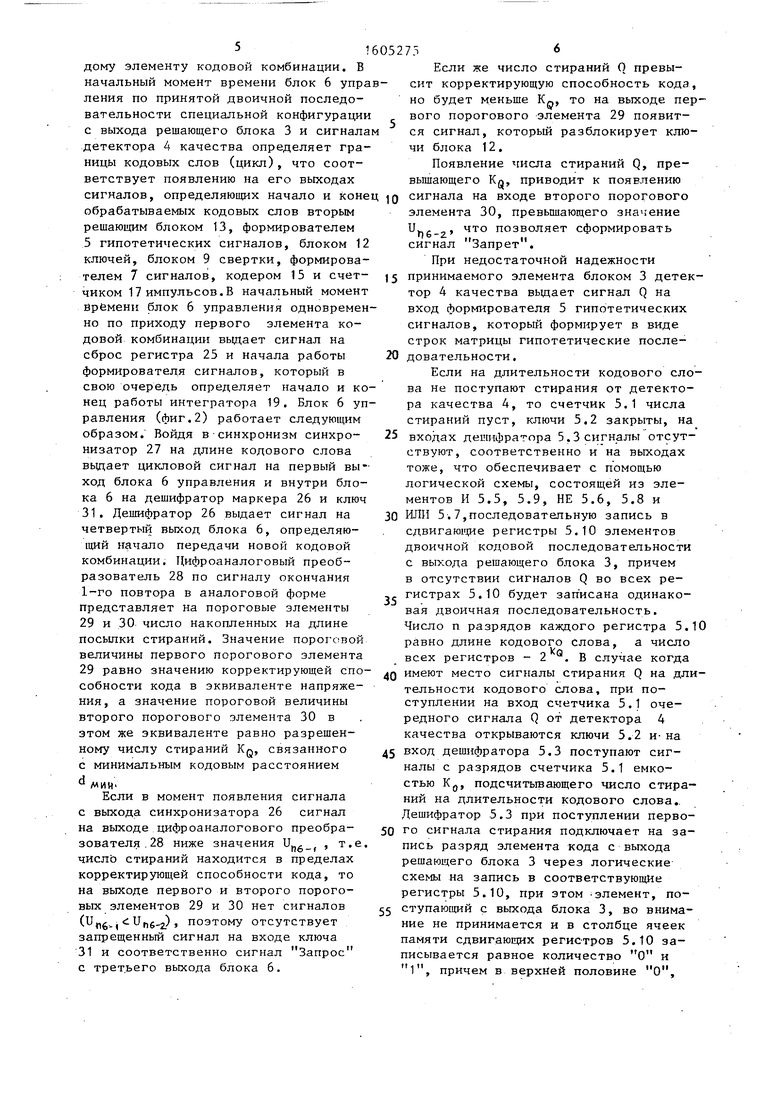

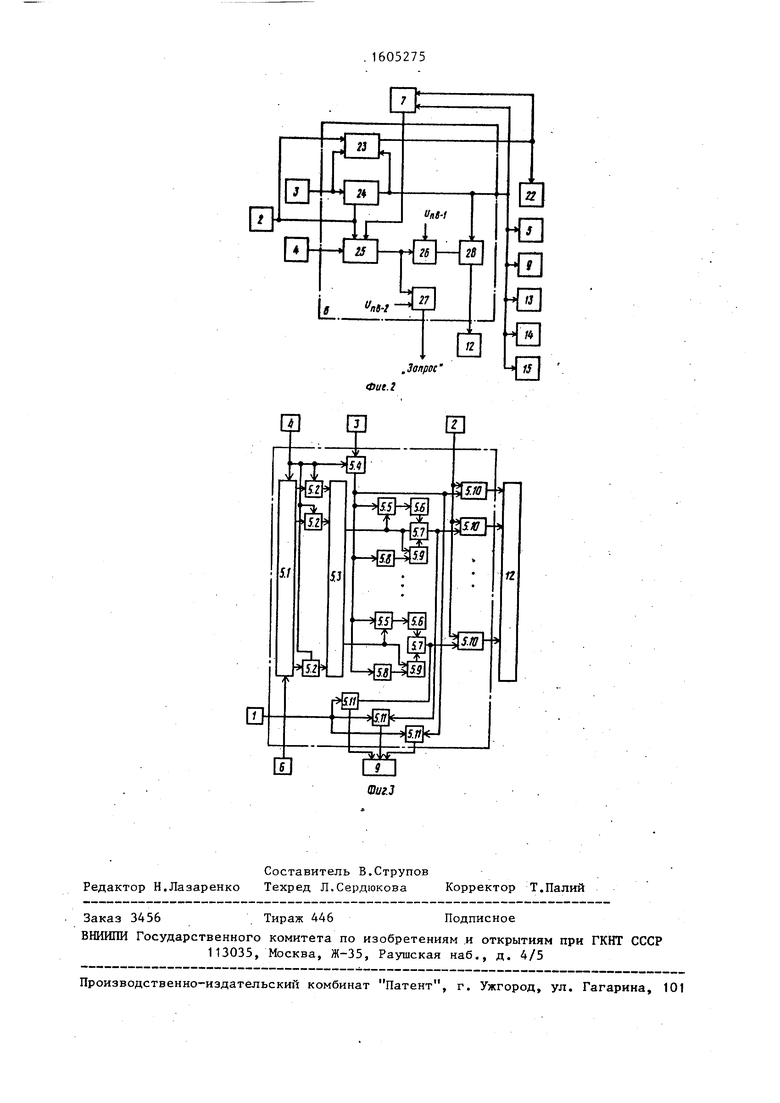

На фиг,1 представлена функциональная схема устройства для приема сигналов, закодированных с избыточно- стью; на фиг.2 - структурная схема блока управления устройства; на фиг.З - структурная схема формирователя гипотетических сигналов.

Устройство содержит блок 1 фазовой автоподстройки частоты,синхро- низатор 2, первый решающий блок 3, детектор 4 качества, формирователь 5 гипотетических сигналов, блок 6 управления, формирователь 7 сигналов, элемент 8 задержки, блок 9 свертки, блок 10 сравнения, дополнительный блок 11 ключей,, блок 12 ключей,второй решающий блок 13, интегратор 14, аналоговый элемент 15 памяти, формирователь 16 пороговых уровней, счет- чик 17 импульсов, кодер 18, модулятор 19,.вычитатель 20, умножитель 21, дополнительный интегратор 22, пороговый элемент 23, управляемый усилитель 24, регистр 25.

Блок 6 управления (фиг.2) содержиГ дешифратор 26 маркера (суперцикла), синхронизатор 27, цифроаналоговый пробразователь 28. Первый 29 и второй 30 пороговые блоки и ключи 31 на фиг.1-3 не показаны.

Вариант технической реализации формирователя 5 гипотетических сигналов представлен на фиг.З. В состав формирователя 5 входят счетчик 5.1 стираний, ключи 5.2, дешифратор 5.3, схемы ИЛИ 5.4, логические схемы, состоящий из элементов И 5.5, НЕ 5.6, ИЛИ 5.7, НЕ 5.8, И 5.9, сдвигающие регистры 5.10 и модуляторы 5.11.

Формирователь сигналов предназначен для формирования интервала интегрирования, может быть реализован на основе регистра циклического сдвига на два разряда (при использовании двухкратного повторения). В началь- ный момент времени по сигналу с третьего выхода блока управления записы логическая 1, а во второй

Q

5

0 5 п

Q .

5

0

754

логический О. Сдвиг информации по регистру происходит по сигналу Конец цикла (конец кодовой комбинации) с второго выхода блока управления. При считывании 1 из первого разряда во второй одновременно с записью сигнал подается на первый управляющий вход интегратора, а при считывании 1 из второго разряда и записи в первый разряд - на второй управляющий вход интегратора.

Регистр предназначен для хранени)ч К информационных разрядов, которые поступают с выхода второго решающего блока, и выдачи их на выход устройства.

Кодер предназначен для приведения избыточности обработанных кодовых комбинаций с выхода второго решающего блока к избыточности входных кодовых комбинаций, модулятор - для преобразования обработанных в устройстве сигналов к виду канальных,, вычитатель - для определения различия непрерывных - канального и регенерированного сигналов, а умножитель - для возведения в квадрат сигнала с выхода блока вычитания .

Дополнительный интегратор предназначен для. накопления энергии разности двух повторов кодовой комбинации, пороговый элемент -.для срав- нения уровня сигнала с выхода интегратора с установленным порогом, синхронизатор предназначен для синхронизации работы устройства, а блок фазовой автоподстройки частоты - для формирования опорного колебания.

Устройство ра ботает следующим образом.

Передача информации осуществляется двоичными сигналами путем формирования информационных посылок, состоящих из нескольких повторов. Уровень, поступающих на вход устройства искаженных помехами двоичных .сигналов, меняется в зависимости от коэффициента передачи канала связи.

Первый решающий блок 3 принимает решение по каждому элементу с задержкой на один такт рабочей частоты дискретного канала связи и ошибается тем чаще, чем интенсивней .помехи в канале связи и чем меньше его коэффициент передачи. Одновременно с работой решающего блока 3 детектор 4 качества принимает решение о надежности принятия решения блоком 3 по каж5160

дому элементу кодовой комбинации, В начальный момент времени блок 6 управления по принятой двоичной последовательности специальной конфигурации с выхода решающего блока 3 и сигналам детектора 4 качества определяет границы кодовых слов (цикл), что соответствует появлению на его выходах

сигналов, определяющих начало и конец д сигнала на входе второго порогового

обрабатываемых кодовых слов вторым решающим блоком 13, формирователем 5 гипотетических сигналов, блоком 12 ключей, блоком 9 свертки, формирователем 7 сигналов, кодером 15 и счетчиком 17 импульсов,В начальный момент Времени блок 6 управления одновременно по приходу первого элемента кодовой комбинации вьщает сигнал на сброс регистра 25 и начала работы формирователя сигналов, который в свою очередь определяет начало и конец работы интегратора 19, Блок 6 управления (фиг,2) работает следующим образом. Войдя в синхронизм синхронизатор 27 на длине кодового слова вьщает цикловой сигнал на первый ход блока 6 управления и внутри блока 6 на дешифратор маркера 26 и ключ 31, Дешифратор 26 выдает сигнал на четвертый выход блока 6, определяющий начало передачи новой кодовой комбинации. Цифроаналоговый преобразователь 28 по сигналу окончания 1-го повтора в аналоговой форме представляет на пороговые элементы 29 и 30 число накопленных на длине посылки стираний. Значение пороговой величины первого порогового элемента

элемента 30, превьш1ающего значение и. , что позволяет сформировать сигнал Запрет.

При недостаточной надежности

15 принимаемого элемента блоком 3 детек тор 4 качества вьщает сигнал Q на вход формирователя 5 гипотетических сигналов, который формирует в виде строк матрицы гипотетические после20 довательности,

Если на длительности кодового сло ва не поступают стирания от детектора качества 4, то счетчик 5,1 числа стираний пуст, ключи 5,2 закрыты, на входах дешифратора 5,3 сигналы отсутствуют, соответственно и на выходах тоже, что обеспечивает с помощью логической схемы, состоящей из элементов И 5,5, 5,9, НЕ 5,6, 5,8 и

30 ИЛИ 5, 7,последовательную запись в сдвигаюидие регистры 5,10 элементов двоичной кодовой последовательности с выхода решающего блока 3, причем в отсутствии сигналов Q во всех регистрах 5,10 будет записана одинаковая двоичная последовательность. Число п разрядов каждого регистра 5,1 равно длине кодового слова, а число всех регистров - 2 , В случае когда

25

35

30 ИЛИ 5, 7,последовательную запис сдвигаюидие регистры 5,10 элеме двоичной кодовой последовател с выхода решающего блока 3, пр в отсутствии сигналов Q во все гистрах 5,10 будет записана од вая двоичная последовательност Число п разрядов каждого регис равно длине кодового слова, а всех регистров - 2 , В случае

29 равно значению корректирующей спо- Q имеют место сигналы стирания Q собности кода в эквиваленте напряжетельности кодового слова, при п ступлении на вход счетчика 5,1 редного сигнала Q от детектора качества открываются ключи 5,2

ния, а знач-ение пороговой величины второго порогового элемента 30 в этом же эквиваленте равно разрешенному числу стираний KQ, связанного с минимальным кодовым расстоянием

минЕсли в момент появления сигнала

с выхода синхронизатора 26 сигнал на выходе цифроаналогового преобраПб-f

т,

зователя.28 ниже значения U, число стираний находится в пределах корректирующей способности кода, то на выходе первого и второго пороговых элементов 29 и 30 нет сигналов (иflg,., .) J поэтому отсутствует запрещенный сигнал на входе ключа 31 и соответственно сигнал Запрос с третьего выхода блока 6.

Если же число стираний О превысит корректирующую способность кода, но будет меньше К, то на выходе первого порогового элемента 29 появится сигнал, который разблокирует ключи блока 12,

Появление числа стираний Q, пре- вьш1ающего KQ, приводит к появлению

элемента 30, превьш1ающего значение и. , что позволяет сформировать сигнал Запрет.

При недостаточной надежности

принимаемого элемента блоком 3 детектор 4 качества вьщает сигнал Q на вход формирователя 5 гипотетических сигналов, который формирует в виде строк матрицы гипотетические последовательности,

Если на длительности кодового слова не поступают стирания от детектора качества 4, то счетчик 5,1 числа стираний пуст, ключи 5,2 закрыты, на входах дешифратора 5,3 сигналы отсутствуют, соответственно и на выходах тоже, что обеспечивает с помощью логической схемы, состоящей из элементов И 5,5, 5,9, НЕ 5,6, 5,8 и

ИЛИ 5, 7,последовательную запись в сдвигаюидие регистры 5,10 элементов воичной кодовой последовательности с выхода решающего блока 3, причем в отсутствии сигналов Q во всех регистрах 5,10 будет записана одинаковая двоичная последовательность. исло п разрядов каждого регистра 5,10 авно длине кодового слова, а число сех регистров - 2 , В случае когда

меют место сигналы стирания Q

имеют место сигналы стирания Q

на длительности кодового слова, при поступлении на вход счетчика 5,1 очередного сигнала Q от детектора 4 качества открываются ключи 5,2 и- на

вход дешифратора 5,3 поступают сигналы с разрядов счетчика 5,1 емкостью KQ, подсчитывающего число стираний на длительности кодового слова.. Дешифратор 5,3 при поступлении первого сигнала стирания подключает на запись разряд элемента кода с выхода решающего блока 3 через логические схемы на запись в соответствующие регистры 5,10, при этом элемент, поступающий с выхода блока 3, во внимание не принимается и в столбце ячеек амяти сдвигающих регистров 5,10

и

исывается равное количество

1, причем в верхней половине О

а в нижней 1. При поступлении на длине той же кодовой комбинации еще одного сигнала стирания в счетчик 5. записывается еще один сигнал Q, при этом в очередном столбце ячеек памяти сдвигаюг лх регистров 5.10 записываются в кажцдой из половинок строк, разбитых пополам, в Ьерхней части О, а в нижней 1. Таким образом, происходит каждый раз формирование очередного столбца разрядов регистра с приходом сигнала Q на длительности кодового слова до разрешенного числа -стираний Кп, связанного с минимальным кодовым расстоянием d|

соотношением

Q мин

определяющим размер матрицы гипотетических последовательностей - пх2 .

На уровне двоичной последовательности это можно представить для одной из кодовых последовательностей циклического (п,К)-кода с парамет- раьш п 7, К 4, d,K 3, исправляющая способность С 1.

Пусть передавалась последовательность 1110100, тогда при отсутствии сигналов О в регистрах 5,10 записывается

Г 1 1

1 1

О

о о о

о о о о

о о о о

5

0

5

0

сверток поступают в блок 10 сравнения, где входу с максимальным результатом свертки на выходе в соответствии ставится выходной сигнал 1 (а всем остальным О), разрешающий считывание с соответствующей строки матрицы формирователя 5 (соответствующего сдвигающего регистра 5.10) последовательности во второй решающий блок 13.

Выход детектора 4 качества, как отмечалось выше, соединен также с входом блока 6 управления, который подсчитывает число сигналов Q на длительности каждого кодового слова.Если их количество не превьш1ает корректирующей способности используемого для передачи сообщения кода, то блок 8

открывает первый ключ блока 12 ключей, блокируя остальные ключи, и элементы первой строки матрицы памяти поступают в решающий блок 13, рабд- тающий в режиме исправления ошибок. В противном случае сигналом соответствующей строки матрицы памяти открывается тот ключ дополнительного блока 11 ключей, на вход которого поступает сигнал, соответствующий максимальному результату сверток на длине j-го,кодового слова

Г

А1акс р Ес

м

n(t)-Sj(t) dt.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема сигналов, закодированных с избыточностью | 1987 |

|

SU1501297A1 |

| Устройство для приема сигналов,закодированных с избыточностью | 1985 |

|

SU1265827A2 |

| Устройство для статистического обнаружения дискретных сигналов в каналах связи с межсимвольной интерференцией | 1986 |

|

SU1363485A2 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2013 |

|

RU2534221C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ | 2010 |

|

RU2431919C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2010 |

|

RU2450445C2 |

| Устройство для передачи и приема информации | 1986 |

|

SU1399797A1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1449989A1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ АДАПТИВНОГО СИГНАЛА СТИРАНИЯ | 2005 |

|

RU2309553C2 |

Изобретение относится к технике и может быть использовано в системах передачи информации. Цель изобретения - повышение достоверности приема информации. Устройство содержит блок 1 фазовой автоподстройки, синхронизатор 2, первый 3 и второй 13 решающие блоки, детектор 4 качества, формирователь 5 гипотетических сигналов, блок 6 управления, формирователь 7 сигналов, элемент 8 задержки, блок 9 свертки, блок 10 сравнения, блоки 11, 12 ключей, интеграторы 14, 22, аналоговый элемент 15 памяти, формирователь 16 пороговых уровней, счетчик 17 импульсов, кодер 18, модулятор 19, вычитатель 20, умножитель 21, пороговый элемент, управляемый усилитель, регистр. Устройство позволяет обрабатывать двукратные повторы передаваемой информации и оценивать результат работы декодирования. 1 з.п. ф-лы, 3 ил.

При появлении сигналов стирания Q в первом и пятом разрядах последовательности получаем

Каждый очередной сигнал, поступающий в регистры 5.10 на запись, ступает на соответствующий модулятор 5.11, с помощью которых производится к виду канальных сигналов S (t).

имеющих место по входу устройства.

Полученные таким, образом гипотетические сигналы S- (t) с выхода формирователя 5 одновременно с входным сигналом Y(t) |M(t) S (t) + n(t), задержанным в элементе 8 задержки, поступают .в блок 9 свертки, где осуществляется их свертка в целом на длине кодовой комбинации. Результатыгде

mi:

40

Е„

Sj(t-)

Sj(t) dt

Сигналы максимальных.результатов свертки с выхода дополнительного блока 11 ключей поступают на вход счетчика 17 и далее через интегратор 14, элемент 15 памяти на формирователь 16, которьй формирует пороговые сигналы детектора 4 качества. Пороговые сигналы формируются с учетом изменения коэффициента передачи канала связи по энергетике, накапливаемой на длительности 1. кодовых слов

С

Данное выражение можно записать

через значение уровня сигнала V..

с

я 1т

|Ц-1.Е

fbl . -

2Z

1

t.

Уровни порогов пороговых схем используемого детектора 4 качества являются частью значения Vj. . Поэтому формирователь 16 вырабатывает два пороговых сигнала детектора 4 качества, равных:

m

2Z

t. n-1

Yf-Jfi

m

и

fzz -t ГпТТ

где m ,, и nij, - постоянные коэффициенты деления, необходимые для обеспечения нормальной работы пороговых схем детектора 4 качества. Предполагается, что значение величины 1, характеризующей интервал локальной стационарности канала связи, известно.

С выхода второго решающего блока 13 кодовые последовательности длиной 2п элементов поступают в регистр 25 и в кодер 18, где в результате кодирования преобразуются в комбинацию из п элементов. Модулятор 19 приводит кодовые комбинации к виду канальных сигналов S(t), имеющих место по входу устройства. С выхода .модулятора 19 данные сигналы подаются на второй вход вычитателя 20, на первый вход которого подаются элементы второго повтора кодовой комбинации. Разностный сигнал с выхода вычитателя 20 через умножитель 21, выполняющий роль квадратора, поступает в интегратор 22, где накапливается на длительности одного повтора энергия разности входного сигнала и регенерированного. Этот сигнал, характеризующий уровень помех в канале и работу второ- го рещающего блока 13, поступает на вход порогового элемента 23. Уровень

60527510

порога данного элемента блока выставляется управляемым усилителем 24.Данный порог уточняется через интервал времени n-l-t, характеризуюцргй интервал локальной стационарности канала связи путем определения среднего коэффициента передачи канала связи |U блоком 14. Таким образом, fO уровень порога элемента 23 будет равен V , где коэффициент усиления усилителя 24, пропорциональный корректирующей способности кода. Интервал интегрирования интегратора 22 формирует блок 7 формирования сигналов, который вьщает два управля- ющих сигнала на управляющие входы интегратора 22. Первый сигнал, определяющий начало интегрирования, пода- 2Q ется После первого повтора кодовой комбинации, а второй - для считывания накопленной энергии после второго повтора. Таким образом устраняется возможность сравнения двух различ- 25 ных кодовых комбинаций.

Если уровень сигнала с выхода интегратора будет превьппать уровень по- рога элемента 23, то формируется сигнал Запрос, и происходит сброс ин- 30 формации в регистре 25. Если сигнал на выходе порогового элемента 23 отсутствует, то происходит считывание информации на выход устройства с регистра 25. Синхронизацию работы уст- ройства осуществляет синхронизатор 2. Устройство позволяет обрабатывать двухкратные повторы передаваемой информации и оценивать результат работы декодирования.

40 Изобретение повьтгает достоверность принимаемой информации за счет умножения вероятности.ощибки при обработке сигналов более чем на порядок.

45 Формула изобретения

0

мента задержки, к выходу которого подключен первый-вход вычитателя, выход которого подключен к первому и второму входу умножителя, выход которого подключен к первому входу дополнительного интегратора, выход которого подключен к первому входу порогового элемента,, выход блока фазрвой автоподстройки частоты подключен к управляющему входу первого решающего блока, четвертому входу формирователя гипотетических сигналов и первому входу модулятора, выход последнего подключен к второму входу вычитателя, выход синхронизатора подключен к тактовым входам первого и второго решающего блока,регистра, детектора качества, кодера, формирователя гипотетических сигналов и блока управления, первый вход формирователя сигналов, объединенный с управляюизим входом кодера, подключен к первому выходу блока управления, четвертый выход которого подключен к первому входу регистра и второму входу формирователя сигнала, первый и второй выходы которого подключены соответственно к второму входу дополнительного интегратора и объединенным третьим -входам интегратора и блока управления, регистр подключен между выходом второго решающего блока и первым вьпсодом устрой- ства соответственно своим вторым входом и выходом, выход .второго решаю- - щего блока подключен к информационному входу кодера, выход которого подключен к второму входу модулятора

выход аналогового элемента памяти че

рез управляемый усилитель подключен

к второму входу порогового элемента.

0

5

0

5

0

0

выход которого, объединенный с третьим выходом блока управления,подключен к третьему входу регистра.

, Запрос

Фие.2

Авторы

Даты

1990-11-07—Публикация

1988-12-26—Подача