1

Изобретение относится к вычислительной технике и может быть иснользовано при моделировании случайных ироцессов, а также в стохастических вычислительных машинах ири вводе и преобразовании информадии.

Известен автоматический вероятностный элемент. Он имеет триггер, в котором один из резисторов выполнен переменным и кинематически связан с реверсивным исполнительным механизмом следящей системы, содержащей частотомер, задатчик и регулятор. Устройство обеспечивает автоматическую стабилизацию выходной вероятности, но оно относительно сложно 1.

Известен также генератор случайной иоследовательности импульсов, который содержит бистабильный элемент, элелмент НЕ

2.

Однако этот генератор не позволяет регулкровать вероятность выходного сигнала.

Цель изобретения - расщирение функциональных возможностей генератора путем регулирования вероятности выходных сигналов.

Поставленная цель достигается тем, что в генератор случайной последовательности импульсов, содержащий управляемый бистабильный элемент, вход которого через элемент НЕ соединен с входом тактовых

импульсов, введены блок согласования и интегратор, первый вход которого является входом генератора. Второй вход интегратора соединен с выходом управляемого бистабильного элемент, а выход через блок согласования - с управляющим входом управляемого бистабильного элемента.

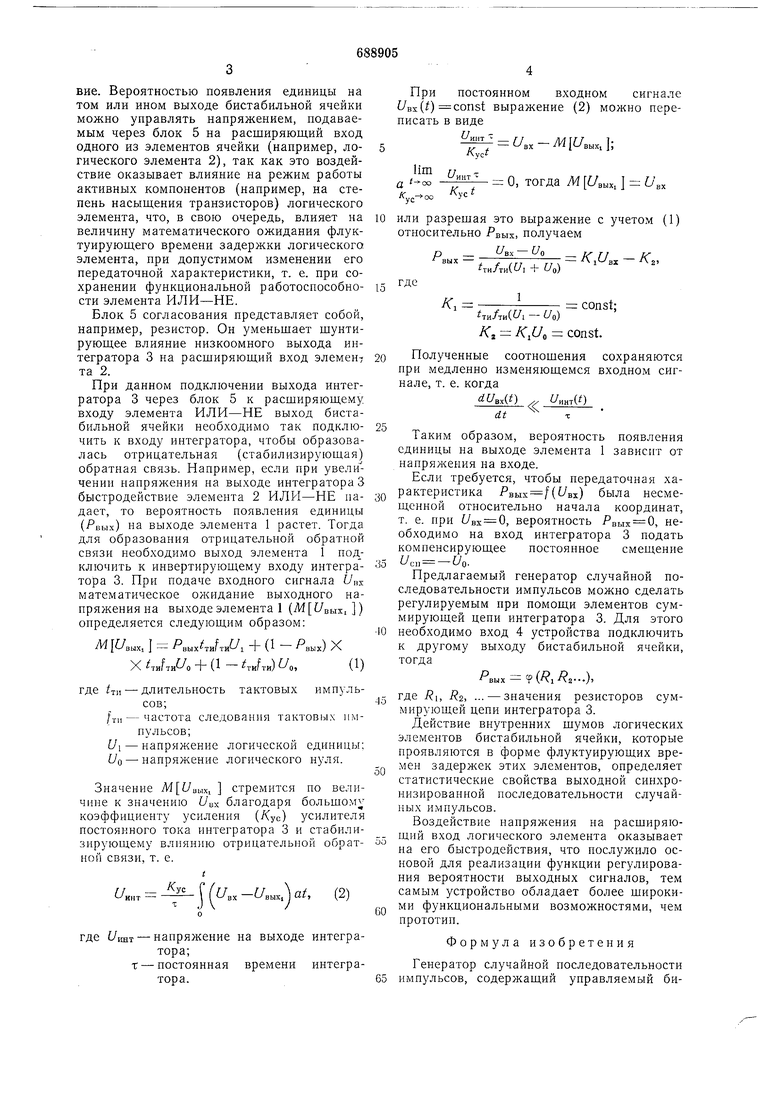

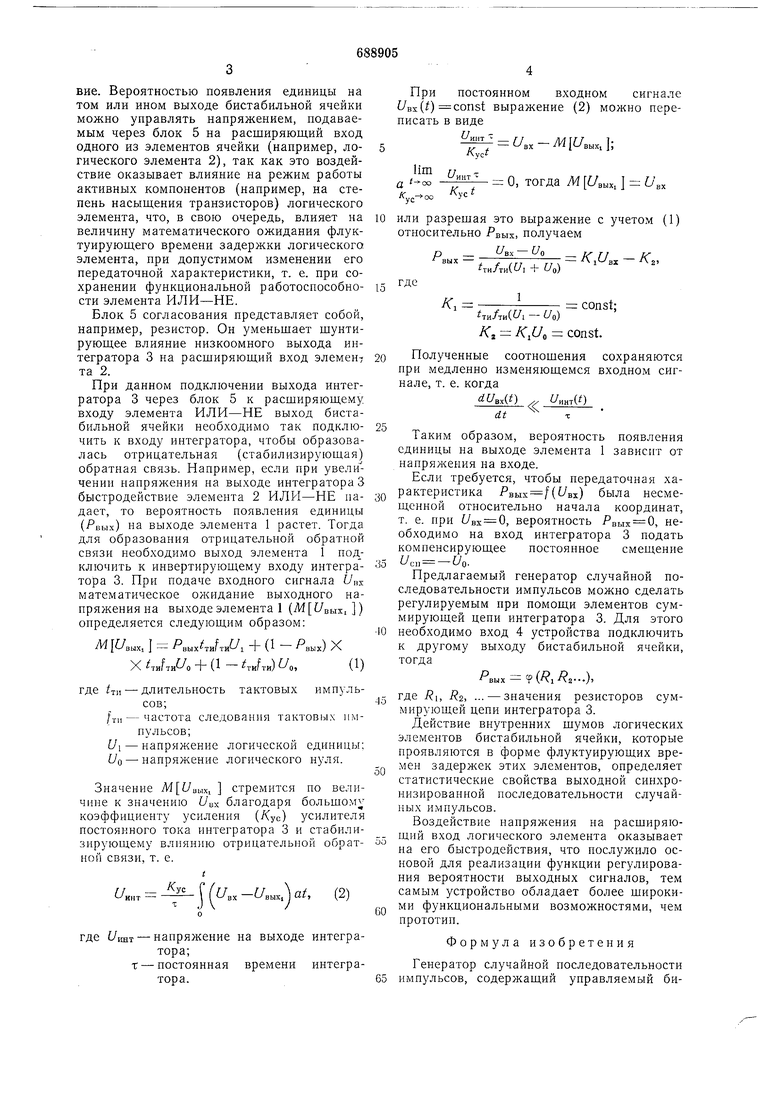

На чертеже представлена схема генератора.

Он содержит первый 1 и второй 2 двухвходовые элементы ИЛИ-НЕ, интегратор 3, один вход которого является входом 4 генератора, блок 5 согласования и элемент НЕ 6, вход которого является входом 7 тактовых импульсов.

Логические элементы 1 и 2 со своими взаимными связями образуют управляемый бистабильный элемент, оба входа которого соединены вместе и через элемент НЕ 6, подключены к входу 7 тактовых импульсов. При отсутствии тактовых имнульсов бистабильный элемент находится в транзитном состоянии и на обоих его выходах формируются логические уровни нуля. При каждом тактовом импульсе бистабильный элемент случайно устанавливается в одно из устойчивых состояний. Логический уровень единицы устанавливается на выходе того элемента ИЛИ-НЕ, который в данный момент времени имеет больщее быстродействне. Вероятностью появления единицы на том или ином выходе бистабильной ячейки можно управлять напряжением, подаваемым через блок 5 на расширяющий вход одного из элементов ячейки (например, логического элемента 2), так как это воздействие оказывает влияние на режим работы активных компонентов (например, на степень насыщения транзисторов) логического элемента, что, в свою очередь, влияет на величину математического ожидания флуктуирующего времени задержки логического элемента, при допустимом изменении его передаточной характеристики, т. е. при сохранении функциональной работоспособности элемента ИЛИ-НЕ. Блок 5 согласования представляет собой, например, резистор. Он уменьшает шунтирующее влияние низкоомного выхода иптегратора 3 па расширяющий вход элемент та 2. При данном подключении выхода интегратора 3 через блок 5 к расщиряющему входу элемента ИЛИ-НЕ выход бистабильной ячейки необходимо так подключить к входу интегратора, чтобы образовалась отрицательная (стабилизирующая) обратная связь. Например, если при увели чении напряжения на выходе интегратора 3 быстродействие элемента 2 ИЛИ-НЕ падает, то вероятность появления единицы (-Рвых) па выходе элемента 1 растет. Тогда для образования отрицательной обратной связи необходимо выход элемента 1 под ключить к инвертирующему входу интегратора 3. Ири подаче входного сигнала t/nx математическое ожидание выходного напряжения на выходе элемента 1 (Л1 /7вых, ) определяется следующим образом: . , -4- (1 - РЗЫХ) X X тиГти о + (1 - тиГти) 0,(1) где ти - длительность тактовых импульсов;/.„ - частота следования тактовых импульсов;f/i - напряжение логической единицы; VQ - напряжение логического пуля. Значение стремится по величине к значению f/ux благодаря большом коэффициенту усиления (/Сус) усилителя постоянного тока иптегратора 3 и стабилизируюпд,ему влиянию отрицательной обратной связи, т. е. .)а/, (2) -инт - где t/HHT - напряжение на выходе интегратора;т - постоянная времени интегратора. При постоянном входном сигнале (0 const выражение (2) можно переписать в виде .,.,; lim rj t Hiii 0, тогда Ж зых. : и,, или разрешая это выражение с учетом ( относительно РВЫХ, получаем f/Bx - f/o /С,з. - К,, - - - 1 г ти/ти(1 + f/o) const; ти/ти(/1 - t/o) Kt - - const. Полученные соотиощения сохраняются при медленно изменяющемся входном сигнале, т. е. когда ) U,(i) Таким образом, вероятность появления единицы на выходе элемента 1 зависит от напряжения на входе. Если требуется, чтобы передаточная характеристика (Ьвх) была несмещенной относительно начала координат, т. е. при , вероятность Рвых 0, необходимо на вход интегратора 3 подать компенсирующее постоянное смещение . Предлагаемый генератор случайной последовательности импульсов можно сделать регулируемым при помощи элементов суммирующей цепи интегратора 3. Для этого необходимо вход 4 устройства подключить к другому выходу бистабильной ячейки, тогда ,х (...) где jRi, Rz, - значения резисторов суммирующей цепи интегратора 3. Действие внутренних щумов логических элементов бпстабильной ячейки, которые проявляются в форме флуктуирующих времен задержек этих элементов, определяет статистические свойства выходной синхронизированной последовательности случайных импульсов. Воздействие папряжения на расширяющий вход логического элемента оказывает на его быстродействия, что послужило основой для реализации функции регулирования вероятности выходных сигналов, тем самым устройство обладает более широкими функциональными возможностями, чем прототип. Формула изобретения Генератор случайной носледовательности импульсов, содержащий управляемый бистабильный элемент, вход которого через элемент НЕ соединен с входом тактовых импульсов, отличающийся тем, что, с целью расширения функциональных возможностей генератора путем регулирования вероятности выходных сигналов, он содержит блок согласования и интегратор, первый вход которого является входом генератора, второй вход интегратора соединен с выходом управляемого бистабильного элемента, а выход интегратора через блок

согласования соединен с управляющим входом управляемого бистабильного элемента.

Источники информации, принятые во внимание при экспертизе

1.Утеуш Э. В., Утеуш 3. В. Введение в кибернетическое моделирование. М., 1971, с. 159-160.

2.Акчурин Р. М. Способы выравнивания вероятностей появления 1 и О в двоичном разряде случайного числа. «Автоматика и вычислительная техника, 1974, N° 1, с. 67, рис. 2-6 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Датчик равновероятных двоичных символов | 1978 |

|

SU752306A1 |

| Генератор случайных чисел | 1981 |

|

SU962932A1 |

| Генератор равновероятной двоичной цифры | 1981 |

|

SU1005044A1 |

| АППАРАТУРА МЕТЕОРНОЙ СВЯЗИ | 2019 |

|

RU2710286C1 |

| Генератор случайной последовательности импульсов | 1973 |

|

SU458821A1 |

| Генератор случайных двоичных символов | 1978 |

|

SU752308A1 |

| Стохастический функциональный преобразователь | 1975 |

|

SU526872A1 |

| Генератор случайных сигналов | 1982 |

|

SU1072246A1 |

| Генератор случайной последовательности | 1979 |

|

SU1040486A1 |

| Генератор случайных чисел | 1977 |

|

SU664185A1 |

Авторы

Даты

1979-09-30—Публикация

1978-05-03—Подача