Изобретение относится к вычислительной технике и может быть исполь зовано при статистическом моделировании систем автоматического управл ния, а также при создании моделей систем массового обслуживания. Известен генератор случайных собы тий, содержащий блок управления, би стабильный элемент, интегратор и блок согласования. Принцип действия данного устройства основан на том, что вероятность одного из двух состояний на выходе бистабильного элеме мента определяется величиной входно го управляющего воздействия. Стабилизация вероятности появления на вы ходе устройства двоичного символа (например, логической единицы) за каждый такт достигается путем введе ния ртрицательной обратной связи 1 Недостатком данного генератора является низкая стабильность характеристик и сложность настройки, вызванные наличием в схеме аналоговых элементов. Известен также генератор событий содержащий генератор случайных равномерно распределенных двоичных и чисел и лагическую схему сравнения, выход которой является выходом устройства. При этом выходы генератора случайных двоичных чисел соединены с первой группой входов логической схемы, а вторая группа входов логической схемы соединена с управляющими входами устройства 2. Недостатком данного генератора является его сложность, вызванная большим объемом и громоздкостью логической схемы сравнения, особенно при числе большой разрядности. Наиболее близким техническим решением к изобретению является генератор случайных чисел, содержащий генератор тактовых импульсов, выход которого соединен с входом генератора равномерно распределенных случайных чисел, выходы которого соединены с входом блока памяти 3. Однако в этом генераторе нет средств для изменения вероятностей формируемых чисел, что ограничивает его функциональные возможности. Цель изобретения - расширение функциональных возможностей генератора за счет регулирования вероятностей формируемых чисел. Для достижения поставленной цели в генератор случайных чисел, содержащий генератор тактовых импульсов, выход которого соединен с входом генератора равномерно распределенных случайных чисел, разрядные выходы которого соединены с соответствующими адресными входами блока памяти., введен управляемый дели тель частоты, выход;) которого соединен с информационным входом блока памяти, управляющий вход которого соединен с выходами -генератора тактовых импульсов и с входом управляемого делителя частоты, управляющие входы которого образуют группу входов генератора.

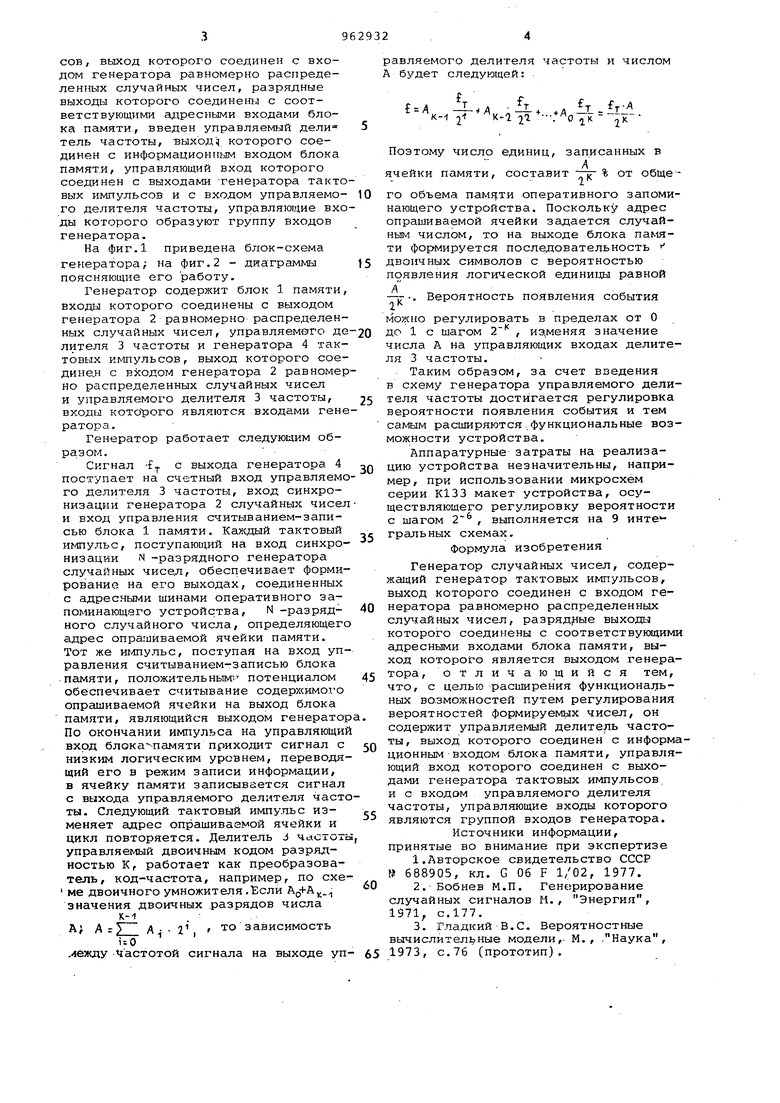

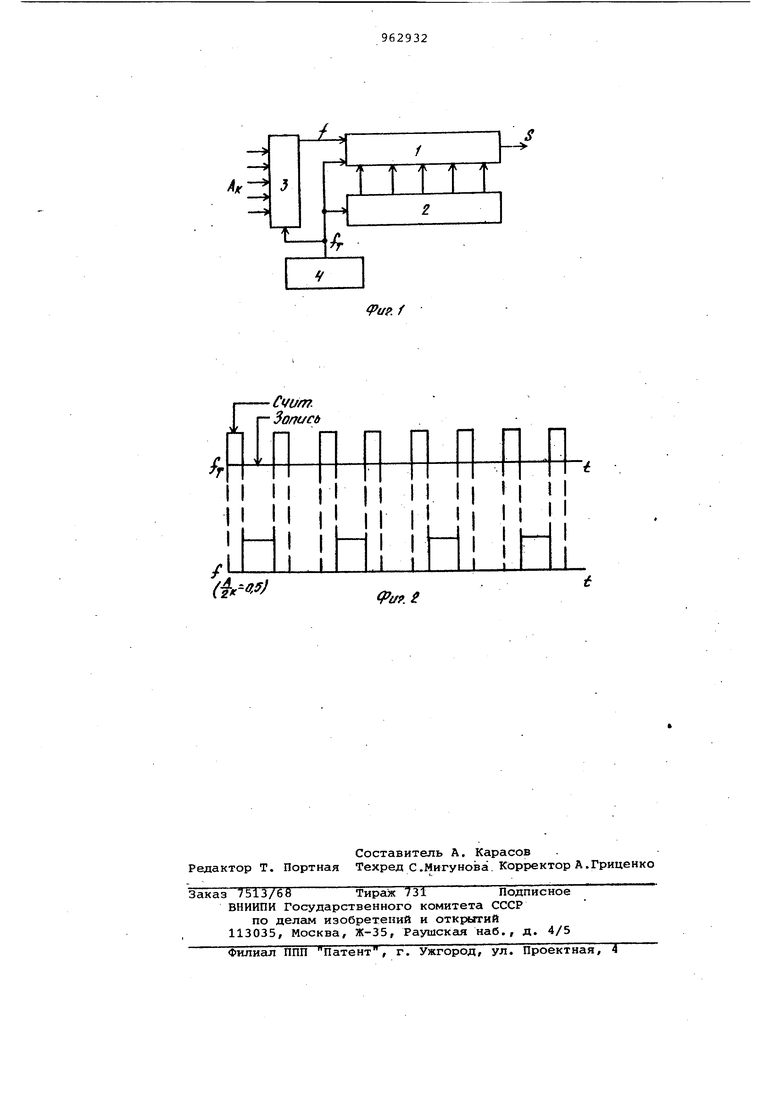

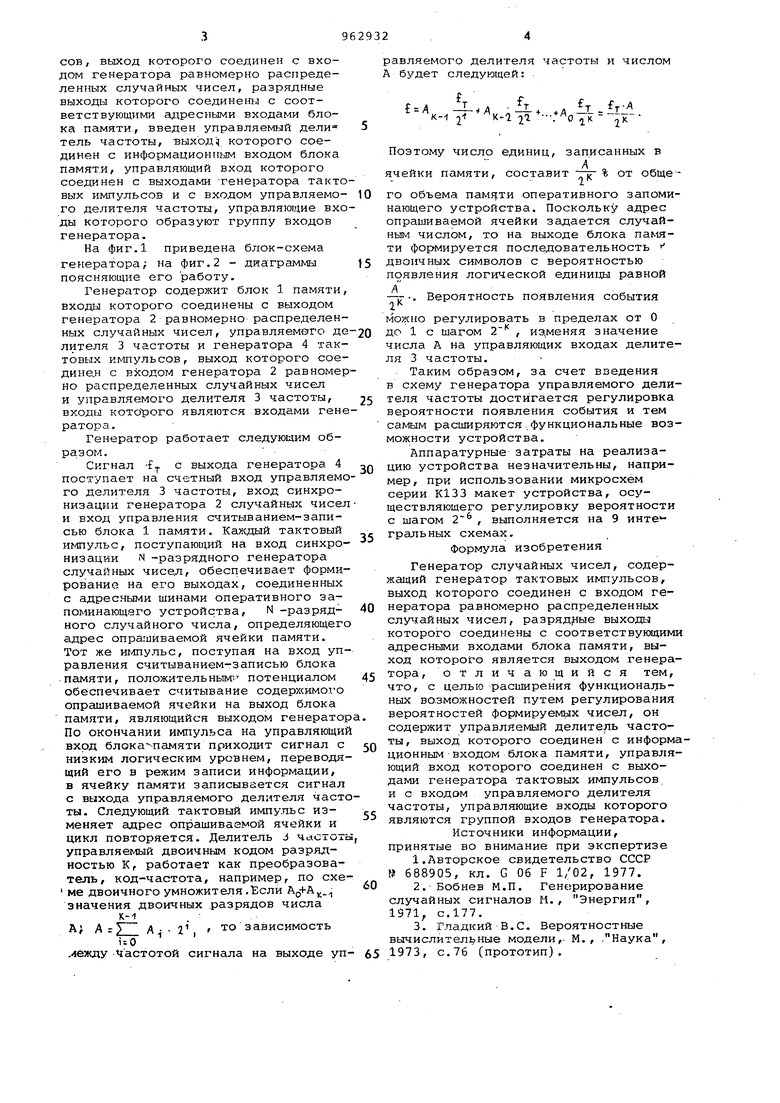

На фиг.1 приведена блок-схема генератора; на фиг.2 - диаграммы поясняющие его работу.

Генератор содержит блок 1 памяти, входы которого соединены с выходом генератора 2 равномерно распределенных случайных чисел, управляемого де лителя 3 частоты и генератора 4 тактовых и 1пyльcoв, выход которого соедине,н с входом генератора 2 равномерно распределенных случайных чисел и управляемого делителя 3 частоты, входы которого являются входами генератора.

Генератор работает следукядим обра.зом

„ „л

Сигнал -f, с выхода генератора 4

поступает на счетный вход управляемого делителя 3 частоты, вход синхронизации генератора 2 случайных чисел и вход управления считыванием-записью блока 1 памяти. Кахсцый тактовый

и lпyльc, поступающий на вход синхронизации N -разрядного генератора случайных чиселf обеспечивает формирование на его выходах, соединенных с адресными шинами оперативного запоминающего устройства, N -разрядного случайного числа, определяющего адрес опрашиваемой ячейки памяти. Тот же ш шульс, поступая на вход управления считыванием-записью блока памяти, положительным потенциалом обеспечивает считывание содерхшмохо опргиииваемой ячейки на выход блока памяти, являющийся выходом генератор По окончании импульса на управляющий вход блокаж-памяти приходит сигнал с низким логическим уровнем, переводящий его в режим записи информации, в ячейку памяти записывается сигнал с выхода управляемого делителя частоты. Следующий тактовый импульс изменяет адрес опрашиваемой ячейки и цикл повторяется. Делитель 3 частоты управляемый двоичным кодом разрядностью К, работает как преобразователь, код-частота, например, по схеме двоичного умножителя .Если . значения двоичных разрядов числа

к А А А 2 то зависимость

ЬО .4ежду 1астотой сигнала на выходе управляемого делителя частоты и числом А будет следующей:

л

-;гМк-.4-.А 1Ьf,-A К

Поэтому число единиц, записанных в

д

ячейки памяти, составит % от общего объема памяти оперативного запоминающего устройства. Поскольку адрес опрашиваемой ячейки задается случайным числом, то на выходе блока памяти формируется последовательность двоичных символов с вероятностью появления логической единицы равной

л „

-у-. Вероятность появления события

можно регулировать в пределах от О

до 1 с шагом 2 , изменяя значение числа А на управляющих входах делителя 3 частоты.

Таким образом, за счет введения в схему генератора управляемого делителя частоты достигается регулировка вероятности появления события и тем самым расширяются,функциональные возможности устройства.

Аппаратурные затраты на реализацию устройства незначительны, например, при использовании микросхем серии К133 макет устройства, осуществляющего регулировку вероятности с шагом 2 , выполняется на 9 инте гральных схемах.

Формула изобретения

Генератор случайных чисел, содержащий генератор тактовых импульсов, выход которого соединен с входом генератора равномерно распределенных случайных чисел, разрядные выходы которого соединены с соответствующим адресными входами блока памяти, выход которого является выходом генератора, отличающийся тем, что, с целью расширения функционаг1ьных возможностей путем регулирования вероятностей формируемых чисел, он содержит управляемый делитель частоты, выход которого соединен с информционным входом блока памяти, управляющий вход которого соединен с выходами генератора тактовых импульсов и с входом управляемого делителя частоты, управляющие входы которого являются группой входов генератора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 688905, кл. G Об F 1/02, 1977.

2.Бобнев М.П. Генефирование случайных сигналов П., Энергия, 1971, с.177.

3.Гладкий B.C. Вероятностные вычислительные модели,- М. , /Наука, 1973, с.76 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестов | 1984 |

|

SU1226472A1 |

| Генератор случайных сигналов с заданным дискретным законом распределения амплитуд | 1989 |

|

SU1735847A1 |

| Устройство для моделирования радиотелеграфного канала связи | 1981 |

|

SU1034053A1 |

| Генератор случайного марковского процесса | 1985 |

|

SU1278842A1 |

| Генератор случайного Марковского процесса | 1982 |

|

SU1070548A1 |

| Цифровой имитатор случайных сигналов | 2019 |

|

RU2722001C1 |

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

| ЦИФРОВОЙ ИМИТАТОР СЛУЧАЙНЫХ СИГНАЛОВ | 2019 |

|

RU2718417C1 |

| Генератор случайных чисел | 1987 |

|

SU1524048A1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 2009 |

|

RU2416157C1 |

ICvum.

г- Зописд

Авторы

Даты

1982-09-30—Публикация

1981-02-18—Подача