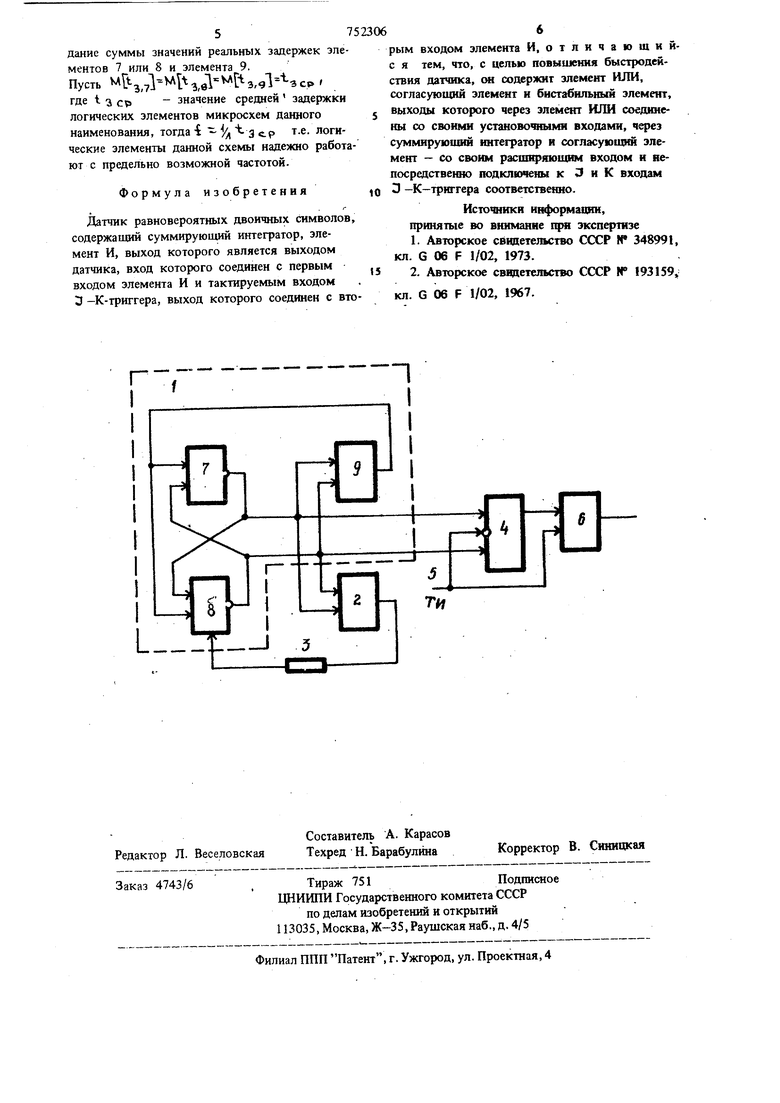

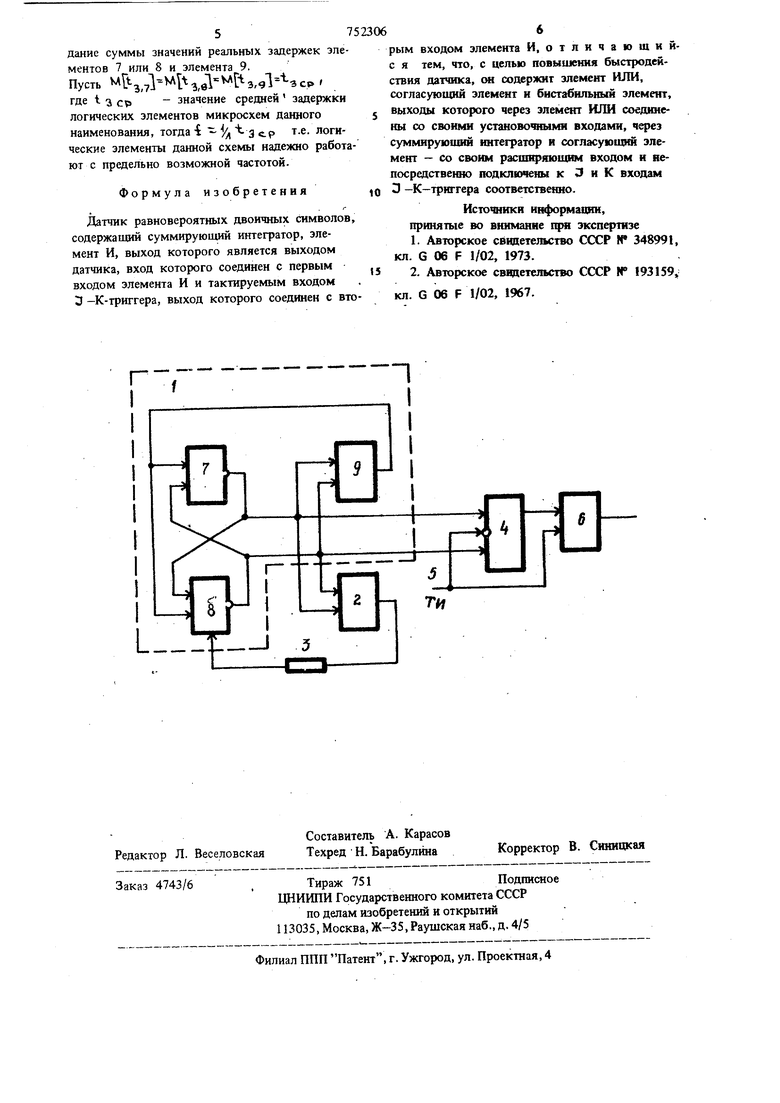

Изобретение относится к вычислительной технике, технике измерения и связи и может быть использовано при моделировании слзд айных процессов, при построении генераторов случайных чисел для цифровых вычислительны машин, имитаторов помех при испытании различной аппаратуры связи. Известен датчик равновероятностных двоичных цифр, содержащий источник шума, усилитель, формирователь, два вентиля, триггер и интегрирующую схему, включенную в цепь обратной связи с выхода датчика на источник щума 1. Известен также датчик равномерно распределенных случайных чисел, содержащий собственно датчик случайных чисел, регулятор по рога срабатывания, счетчик тактовых импульсов и выходной вентиль 2. Работа его основана на использовании стабвдизирующей обратной связи, а отбор символов осуществляется через некоторое 4i:cno тактов работы датчика. Известный датчик не в полной мере использует быстродействие составляющих его элементов. Цель изобретения -- повышение быстродействия датчика. Для достижения поставленной цели в известный датчик равновероятных двоичных символов, содержащий суммирующий интегратор, элемент И, выход которого является выходом датчика, вход которого соединен с первым входом элемента И и с тактируемым входом 3 -К-триггера, выход которого соединен с вторым входом элемента И, введены элемент ИЛИ, согласующий элемент и бистабильный элемент, выходы которого через элемент ИЛИ соединены со своими установочными входами, через суммирующий интегратор и согласующий элемент - со своим расширяющим входом и непосредственно подключены к 3 и К входам3-К -триггера соответственно. На чертеже приведена блок-схема датчика. Датчик равновероятных двоичных символов содержит генератор 1 случайной последовательности импульсов, зуммирутоишй интегратор 2, согласующий элемент 3, tJ-К-триггер 4, вход синхронизации которого является входом 5 тактовых импульсов (ТИ) и элемент 6 И, причем, генератор 1 еостоит из двух элементов 7 и 8 ИЛИ-НЕ и элемента 9 ИЛИ. Элементы 7 и 8 ИЛИ-НЕ со своими взагаяными связями образуют бистабильный элемент, оба входа которого соединены вместе ш подключены к выходу элемента 9. При установлении бистабильного элемента в транзитное состояние 00 (по выходам элеме тов 7 и 8 соответственно) элемент 9 ИЛИ стремится перевести его в устойчивое состояние 01 или 10 и наоборот, при формир вании того или иного устойчивого состояния бистабильного элемента , элемент 9 ИЛИ стре мится перевести его в транзитное состояние. В момент появления с выхода элемента 9 сигнала О бистабильный элемент переходит в одно из устойчивых состояний и сигнал 1 устанавливается на выходе того элемента 7 или 8, скорость срабатывания которого в данный момент большая. После установления одного из устойчивых СОСТОЯНИЙ бнстабильного элемента элемент 9 ИЛИ вновь переводит его в транзитное состояние, затем он случайным образом снова устанавливается в одно из устойчивых состояний и тд. Таким образом, элементы 7, 8 и 9 образуют неустойчивую систему (генератор 1 случайной последователь ности импульсов), которая все время находит ся в режиме генерации. Скорость переходных процессов, происходящих в генераторе 1, мак симально возможная и определяется реальными значениями времен задержки составляющи его элементов. Эти задержки вследствие влия ния внутренних шумов являются случайными величинами. Они определяют случайность значений периода-следования и длительности импульсов, а также случайность присутствия сиг нала 1 в данном периоде импульсной после довательности генератора 1. Вероятностью появления сигнала 1 можно утгравлять напряжением, снимаемым с выхода суммирующего интегратора 2 и подаваемым через согласующ элемент 3 на расщиряющий вход одного иэ элементов 7 или 8ч Это воздействие оказывае влияние на режим работы активных компонен тов, например на степень насыщения транзисторов, логического элемента, что в свою очередь влияет на величину математического ожи дания флуктуирующего времени задержки логического элемента, при допустимом изме нении его передаточной характеристики, т.е. при сохранении функциональной работоспособ ности логического элемента. Элемент 3 уменьшает шунтирующее влияние низкоомного выхода интегратора 2 на расщиряющий вход логического элемента. Выходы бистабильного элемента, т.е. выходы элементов 7 и 8, являются выходами генератора 1 случайной последовательности импульсов. Йыходы суммирующего интегратора 2, при данном соединении выхода его с расширяющим входом логического элемента, должны быть подключены к выходам генератора 1 так, чтобы образовалась отрицательная обратная связь, например, если при увеличении напряжения с выхода интегратора 2, подаваемого через резистор 3 на расщиряющий вход логического элемента 8, быстродействие этого элемента падает, следовательно, вероятность появления сигнала 1 на выходе логического элемента 7 растет. Для образования отрицательной обратной связи выход элемента 7 необходимо подключить к инвертирующему входу суммирующего интегратора 2, а выход элемента 8 - к неинвертирующему входу этого интегратора. Считывание информации осуществляется с помощью И -К триггера 4 и элемента 6 И. При отсутствии тактового импульса, т.е. при ТИ - О, на триггер 4 действуют сигналы бистабильной ячейки. Если бистабильный элемент находится в устойчивом состоянии, то триггер 4 работает как R-S-триггер, а при транзитном состоянии бистабильной ячейки 4 работает как счетный триггер. С приходом тактового импульса формируется случайный символ на выходе датчика за счет случайного состояния триггера 4, которое определяется как результат многократного суммирования и по модулю два сигналов с генератора 1 случайной последовательности импульсов. При этом триггер 4 не реагирует на сигналы генератора 1 в течение действия Ш - 1. Наличие триггера 4 в устройстве считывания информации с датчика устраняет возникновение ложных сигналов в момент действия ТИ-1, которые могут возникнуть вследствие независимости частоты тактовых импульсов и Частоты работы генератора I, а также устраняет влияние транзитных состояний бистабильной ячейки на формирование выходных символов. Частота f следования сигналов 1 с выходов генератора 1 случайной последовательности импульсов определяется как .А 37,,91raeMlt - ij.-rl математическое ожидание суммы значений реальных задержек элементов 7 или 8 и элемента 9. Пусть Mtt y-M t VK-t3,1-1,,

где 1 3 СР - значение средней задержки логических элементов микросхем данного наименования, тогда-4 .p т.е. логические элементы данной схемы надежно работают с предельно возможной частотой.

Формула изобретения

Датчик равновероятных двоичных символов, содержащий суммируюицш интегратор, элемент И, выход которого является выходом датчика, вход которого соединен с первым входом элемента И и тактируемым входом 3 -К-триггера, выход которого соединен с вторым входом элемента И, отличающийс я тем, что, с целью повышення быстродействия датчика, ая содержит элемент ИЛИ, согласующий элемент и бистабнпьный элемент, выходы которого через элемент ИЛИ соедннены со своими установочными входами, через суммирующий интегратор и согласующий элемент - со своим расш1фяющ|1м входом и непосредственно нодключены к О и К входам 3 -К-трнггера соответственно.

Источники информации, принятые во вннманне при экспертизе

1.Авторское свидетельство СССР Н 348991, кл. G 06 F 1/02, 1973.

2.Авторское свидетельство СССР № 193159 кл. G 06 F 1/02, 1967.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайной последовательности импульсов | 1978 |

|

SU688905A1 |

| Генератор равновероятной двоичной цифры | 1981 |

|

SU1005044A1 |

| Генератор случайной последовательности | 1983 |

|

SU1109747A1 |

| Датчик случайных двоичных сигналов | 1974 |

|

SU526871A1 |

| Генератор случайных двоичных символов | 1978 |

|

SU752308A1 |

| Генератор случайных двоичных сигналов | 1982 |

|

SU1056189A1 |

| Генератор случайной последовательности | 1983 |

|

SU1275434A1 |

| АДАПТИВНАЯ РАДИОЛИНИЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1991 |

|

RU2010430C1 |

| СИГМА-ДЕЛЬТА-АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1998 |

|

RU2145149C1 |

| УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ТАКТОВОГО КОЛЕБАНИЯ | 1991 |

|

RU2007881C1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-10—Подача