(54) ВЕРОЯТНОСТНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый вероятностный двоичный элемент | 1985 |

|

SU1283757A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1388886A1 |

| Устройство для сопряжения дискретных датчиков с электронной вычислительной машиной | 1982 |

|

SU1024898A2 |

| Устройство для контроля монтажа | 1985 |

|

SU1352505A1 |

| Многоканальное устройство обегающего контроля | 1982 |

|

SU1087964A1 |

| Голографическое постоянное запоминающее устройство | 1990 |

|

SU1725258A1 |

| Система для передачи хронометрической информации | 1984 |

|

SU1251152A1 |

| Генератор случайного процесса | 1983 |

|

SU1124295A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

1

Изобретение относится к вычислительной технике и может использоваться в системах для статистического моделирования.

Известны вероятностные распределители импульсов, позволяющие осуществлять простра нственное разделение импульсов по выходным шинам с заданной вероятностью, т. е. реализовывать полную группу несовместных событий.

Известен вероятностный распределитель импульсов, содержащий равновероятностный (1,К)-полюсник и электронный коммутатор выходов 1.

Применение его для реализации полной группы несовместных событий требует ровно () данных схем, что обуславливает значительный объем оборудования.

Известен также вероятностный распределитель импульсов, вьгполненный на многоэлектродном разряднике 2.

Этот распределитель импульсов прост по исполнению, однако, отмечается низкая точность и нестабильность.

Наиболее близким по техническому решению -является вероятностный распределитель, импульсов; содержащий генератор импульсов, блок памяти, датчик случайных чисел, вход опроса которого соединен с выходом первого элемента ИЛИ, дешифратор, выходы которого с:оедиНёнъг С Первьши входами первого блока элементов И соответственно, выходы KOTopiax являЮтся вь1ходами

вероятностного распределителя импульсов, а вторые входы подключены к выходу первого элемента И, первый вход которого является первым входом вероятностного распределителя импульсов 3.

Недостатком распределителя является

сложность схемного решения при достижении уровня быстродействия, свойственного параллельным схемам формирования случайных сигналов.

Целью изобретения является упрощение распределителя при сохранении высокого быстродействия.

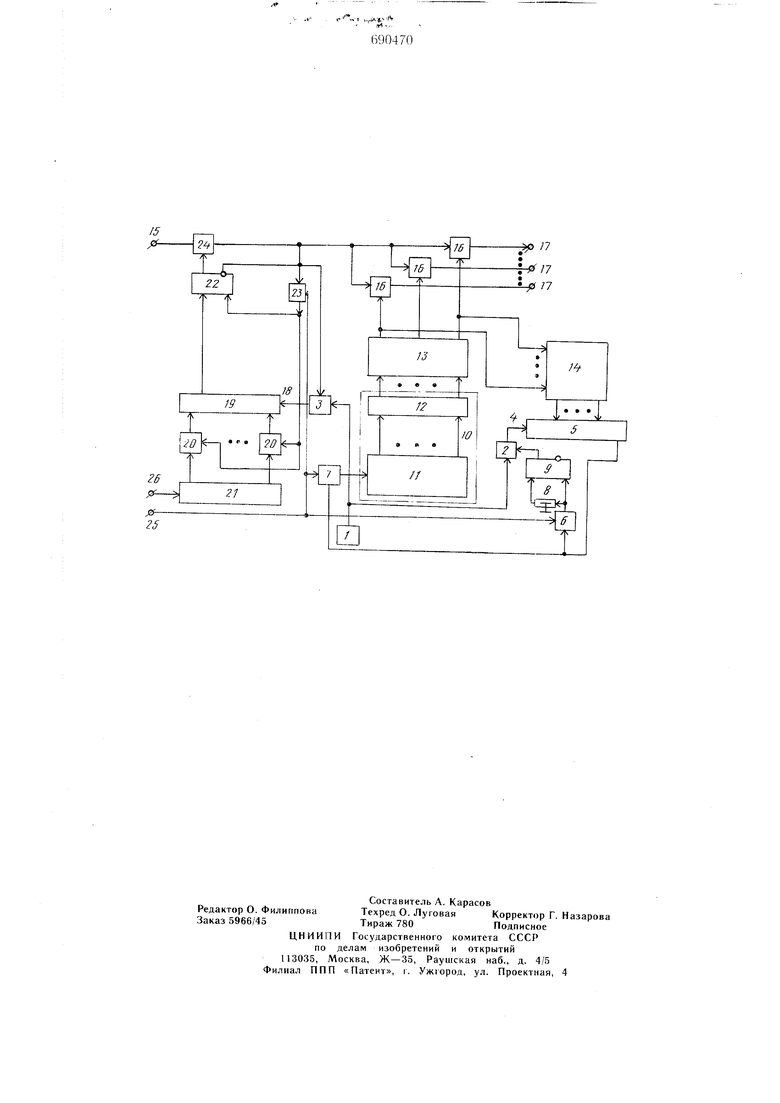

Для этого преобразователь содержит счетчик времени, счетчик задержки, второй блок элементов И, второй и третий элементы ИЛИ, второй и третий элементы И, элемент задержки, первый и второй триггеры и регистр задержки, вход которого является вторым входом вероятностного распределителя импульсов, а выходы соединены с первыми входами второго блока элементов И соответственно, выходы которых подключены к разрядным входам счетчика задержки, а вторые входы соединены с выходом второго элемента ИЛИ и нулевым входом первого триггера, нулевой, выход которого аодключен к первому входу второго элемента И, выход которого соединен со входом счетчика задержки, выход старшего разряда которого подключен к единичному входу первого триггера, единичный выход которого подключен ко второму входу первого элемента И, третий вход вероятностного распределителя импульсов подключен к первым входам первого, второго и третьего элементов ИЛИ, вторые входы которых подключены соответственно к выходу первого элемента И и выходу счетчика времени, разрядные входы которого подключены к выходам блока памяти, входы которого соединены с выходами дешифратора соответственно, выход генератора импульсов соединен со вторым входом второго элемента И и с первым входом третьего элемента И, выход которого подключен ко входу счетчика времени, а второй вход - к выходу второго триггера, единичный вход которого через элемент задержки, а нулевой вход непосредственно подключены к выходу третьего элемента ИЛИ. На чертеже представлена блок-схема вероятностного распределителя импульсов. Распределитель содержит генератор 1 импульсов, выход которого соединен с первым входом элемента И 2 и первым входом элемента И 3. Выход элемент.а И 2 подключен ко входу 4 вычитания счетчика 5 времени. Выход старшего разряда счетчика 5 времени соединен с первым входом элемента ИЛИ 6 и первым входом элемента ИЛИ 7. Выход элемента ИЛИ б соединен со входом элемента задержки 8 и с нулевым входом триггера 9. Выход элемента задержки 8 связан с единичным входом триггера 9, единичный выход которого соединен со вторым входом элемента И 2. Выход элемента ИЛИ 7 соединен со входом опроса датчика 10 случайных чисел, состояш,его из блока генераторов шума 11 , выходы которых соединены с уста новочными входами регистра кода 12. Выходы регистра кода 12 подключены ко входам дешифратора 13. Выходы дешифратора 13 соединены со входами блока памяти 14. Входом опроса распределителя является шина 15. Выходы первого блока элементов И 16 являются выходами 17 вероятностного распределителя импульсов. Выход элемента И 3 соединен со входом вычитания 18 счетчика задержки 19, разрядные входы которого через второй блок элементов И 20 соединены с выходами регистра задержки 21. Вторые входы элементов И 20 объединены и подключены к нулевому входу триггера 22 и выходу элемента ИЛИ 23. Нулевой выход, триггера 22 соединен со вторым входом элемента И 3, а его единичный выход подключен к первому входу элемента И 24, выход которого соединен с первым входом элемента ИЛИ 23 и вторыми входами элементов И 16. Шина 25 установки распределителя в исходном состоянии соединена со вторыми входами элементов ИЛИ 6, 7 и 23. Вход 26 установки задержки подключен к соответстВУЮШ.ИМ установочным входам регистра задержки 21. Вероятностный распределитель импульсов работает следуюшим образом. В исходном состоянии в блок памяти 14 записываются коды временных интервалов TI , Ti ... Т„, величина которых пропорциональна переходным вероятностям распределителя. В регистр задержки 21 по входу 26 установки задержки записывается величина максимальной задержки, сложенная с величиной интервала времени, необходимого для извлечения кода из блока памяти 14. После этого подается сигнал но шине 25 установки распределителя в исходное состояние, который одновременно попадает на вторые входы элементов ИЛИ 6, 7 и 23. Сигнал с выхода элемента ИЛИ 6 подается на нулевой вход триггера 9 и вход элемента задержки 8, время задержки которого выбирается равным времени выборки кода из блока памяти 14, сложенным с временем переключения элементов соответствуюш,ей цепочки передачи. Одновременно подается сигнал на вход опроса блока генераторов шума 11 с выхода элемента ИЛИ 7, а сигнал с выхода элемента ИЛИ 23 устанавливает триггер опроса 22 в нулевое состояние и разрешает передачу кода из регистра задержки 21 через элементы И 20 на вход счетчика задержки 19. После установки триггера 22 в нулевое состояние и ввода кода задержки в счетчик 19 разрешается подача синхроимпульсов с генератора 1 на вход вычитания 18 счетчика задержки 19. При установлении нулевого кода на счетчике 19 вырабатывается сигнал переноса из старшего разряда счетчика 19, устанавливающий триггер 22 в единичное состояние. При этом прекращается подача синхроимпульсов на вход вычитания 18 счетчика задержки 19 и разрешается подача сигналЬв по входу 15 опроса распределителя. Данное состояние элементов сохраняется до прихода сигнала по этому входу. При появлении сигнала по входу 15 и единичном состоянии триггера 22 этот сигнал поступает на вторые входы элементов И 16, один из которых должен быть открыт с соответствуюш.его выхода дешифратора 13. Причем вероятность появления сигнала на выходе i-ro элемента И 16 определяется временем нахождения дешифратора 13 в i-M состоянии. Таким образом, сигнал на выходе 17 распределителя появляется с заданной вероятностью Pj. Для уменьшения времени возврата устройства в исходное состояние (увеличения быстродействия) пос ле предыдущего сигнала опроса по входу 15, определяемого максимальной величиной Pi (i 1,2, ..,п), т. е. времени вычитания кода из счетчика 19, в устройство могут быть введены мно овходовые элементы ИЛИ (на чертеже не показаны), соединенные входами с соответствующими выходами дешифратора 13 и управляющие теми элементами И 16, сигнал на выходе которых появляется с большими по величине вероятностями. Число входов элемента ИЛИ, управляющего входом i-ro элемента. И 16, выбирается из условия, чтобы суммарное время нахождения дешифратора 13 в состояниях, соответствующих входам этого элемента ИЛИ, было пропорционально вероятности (больщой по величине) появления импульса на i-ом вь1ходе устройства. Одновременно с поступлением сигнала на вторые входы элементов И 16 он подается на вход элемента ИЛИ 23 и производит действия, аналогичные описанным выше при появлении сигнала с выхода 25 установки схемы в исходное состояние на втором входе элемента ИЛИ 23. Сигнал опроса блока генераторов щума i1 может появиться: при установке исходного состояния распределителя путем подачи сигнала по щине 25 на первый вход элемента ИЛИ 7; после установки распределителя в исходное состояние при возникновении сигнала переноса из старшего разряда счетчика 5, поступающего на второй вход элемента ИЛИ 7. В результате опроса блока генераторов шума 11 код подается на регистр кода 12, с которого данный код передается на дешифратор 13. После дешифрации возбуждается один из выходов дешифратора 13 и выбирается код временной задержки по соответствующему адресу блока памяти 14. Выбранный код задержки поступает на счетчик 5 времени. Одновременно с установкой временного интервала триггер 9 устанавливается в единичное состояние с вь1хода элемента задержки 8 и разрешается подача синхроимпульсов с генератора 1 через элемент И 2 на вход вычитания 4 счетчика 5. По окончании считывания временного интервала вырабатывается сигнал переноса единицы старшего разряда счетчика 5, устанавливающий через элемент ИЛИ 6 триггер 9 в нулевое состояние и проходящий через элемент ИЛИ 7 на вход опроса блока генераторов щума 11. После поступления сигнала опроса на вход блока генераторов шума 11 вновь повторяется описанная последовательность выработки сигналов и смеиы состояний элементов. Конструкция вероятностного р спределителя импульсов за счет моделирования -вероятностей появления импульсов на его выходах временными интервалами позволяет избежать большого числа многоразрядных схем сравнения, фиксирующих интервалы распределения и составляющих значительный объем оборудования. Формула изобретения Вероятностный распределитель импульсов, содержащий генератор импульсов, блок памяти, датчик случайных чисел, вход опроса которого соединен с выходом первого элемента ИЛИ, дешифратор, выходы которого соединены с первыми входами элементов И первого блока соответственно, выходы которых являются выходами вероятностного распределителя импульсов, а вторые входы подключены к выходу первого элемента И, первый вход которого является первым входом вероятностного распределителя импульсов, отличающийся тем, что, с целью упрощения вероятностного распределителя импульсов, он содержит счетчик времени, счетчик задержки, второй блок элементов И, второй и третий элементы ИЛИ, второй и третий элементы И, элемент задержки, перчый и второй триггеры и регистр задержки, вход которого является вторым входом вероятностного распределителя импульсов, а выходы соединены с первыми входами элементов И второго блока соответственно, выходы которых подключены к разрядным входам счетчика задержки, а вторые входы соединены с выходом второго элемента ИЛИ и нулевым входом первого триггера, нулевой выход которого подключен к первому входу второго элемента И, выход которого соединен со входом счетчика задержки, выход старшего разряда которого подключен к единичному входу первого триггера, единичный выход которого подключен ко второму входу первого элемента И, третий вход вероятностного распределителя импульсов подключен к первым входам первого, второго и третьего элементов ИЛИ, вторые входы которых подключены соответственно к выходу первого элемента И и к выходу счетчика времени, разрядные входы которого подключены к выходам блока памяти, входы которого соединены с выходами дешифратора соответственно, выход генератора импульсов соединен со вторым входом второго элемента И и с первым входом третьего элемента И, выход которого подключен ко входу счетчика времени, а второй вход - к выходу второго триггера, единичный вход которого через элемент задержки, а нулевой вход непосредственно подключены к выходу третьего элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 209046, кл. G 06 F 1/02, 1966. 2.Авторское свидетельство СССР № 317077, кл. G 06 F 1/02, 1969. 3.Авторское свидетельство СССР № 213424, кл. G 06 F 1/02, 1968,

Авторы

Даты

1979-10-05—Публикация

1974-10-17—Подача