первой группы, выходы которых подключены к третьим входам соответствующих элементов И четвертой группы, выходы котфрых соединены с тре ей группой выходов блока и группой входов первого элемента ИЛИ,входом подключенного к выходу соответствующего элемента И первой группы.

3, Устройство по п. 1, о т л ич а ю щ е е с я тем, что узел управления содержит шесть элементов И, реверсивный счетчик, генератор тактовых импульсов, счетчикf три дешифратора, три триггера, элемент ИЛИ и элемент задержки, лрйчем нулевой вход первого триггера соединен с третьим входом узла, единичный вход - с четвертым входом узла и прямым входом первого элемента И,/ а нулевой выход - с первым входом элемента ИЛИ, пятым входом узла и через элемент задержки с инверсным входом первого элемента И, выходом подключенного к нулевому входу второго триггера, единичный вход которого соединен через первый дешифратор с выходом счетчика, выход элемента ПЛИ подключен к инверсному входу второго элемента И, а второй вход - к нулевому выходу второго триггера и первому входу третьего элемента И, выходом соединенного с четвертым выходом узла и входом счетчика,а вторым входом - с выходом генератора тактовых импульсов, первым npHNMM входом второго элемента И, вторым входом соединенного с вторым выходом узла и нулевым выходом :третьего триггера, а выходом - с

третьим выходом узла и первым входом реверсивного счетчика, второй вход которбго подключен к второму входу узла, третий вход - к выходу пятого элемента И, а выход через второй даиифратор к единичному входу третьего триггера, единичным выходом соединенного с вторым прямым входом второго элемента И, выход которого является первым выходом узла, выход шестого элемента И соединен с нулевым входом третьего триггера, первый вход - с первьм входом узла и инверсным входом пятого элемента И, а второй вход - с прямым входом пятого элемента И и выходом третьего доиифратора, группа входов которого является группой 9хо;цов узла.

4. Устройство по п. 1, о т л ич а ю и е е с я тем, что блок декодирования содержит распределитель импульсов, генератор импульсов, два триггера, группы элементов И и элемент ИЛИ, причем первые входы элементов И группы соединены с группой входов блока, вторые вхЬды - с группой выходов распределителя гошульсов, а выходы - с группой входов эле-мента ИЛИ, выход которого подключен к счетному входу первого триггера, выходом соединенного с выходом блока, а установочньвл входом - с входом блока и единичным входом второ- го триггера, выход которого через генератор шлпульсов подключен к распределителю имйульсов, а нулевой илход К соответствующему выходу группы выходов распределителя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с общей магистралью | 1988 |

|

SU1532939A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1462336A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1265777A1 |

| Вычислительное устройство для формирования маршрута сообщения | 1982 |

|

SU1037269A1 |

| Устройство для сопряжения группы каналов ЭВМ с группой периферийных устройств | 1987 |

|

SU1520529A1 |

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ДИСКРЕТНЫХ ДАТЧИКОВ С ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНОЙ по авт.с 824185, о т ли ч а ю щ е е с я тем, что, с целью повышения достоверности передачи сообщений, в устройство введены группа регистров, блок контроля блок декодирования, сумматор, группа элементов ИЛИ,вторая, третья и четвертая группы элем тов И, причем информационные входы регистров группы соединены с группой информационных входов устройства, управляющие входа - с четвертым выходом узла управления, третий вход которого соединен с входом синхронизации устройства, а четвертый вход и пятый выход - соответственно с первыми выходом и входом блока контроля, вторые вход и выход которого соединены соответствен но с выходом и входом блок;а декодирования, группой входов подключенного к группе выходов сумматора, группы выходов регистров группы сое динены с первыми входами элементов И второй и третьей групп и соответствующими входами элементов ИЛИ гру пы, выходы которых соединены с груп пой информационных входов кс 1мутато ра, выходы регистров группы подклю чены к первым входам элементов И че вертой группы, выходы элементов И второй и четвертой групп являются соответственно первой и второй груп пами информационных выходов устрой- ства, вторые входы элементов И второй, третьей и четвертой групп соединены соответственно с первой, второй и третией группами выходов блока контроля, выходы элементов И третьей группы соединены с группой выходов сумматора. 2. Устройство по п. 1, о т л игчающееся тем, что блок контроля содержит четыре группы элементов И дешифратор, две группы триггеров, два элемента ИЛИ, распределитель импульсов, элемент задержки, генератор тактовой частоты и триггер, причем единичный вход триггера соединен с первым входом блока, нулевой вход - с выходом первого элемента ИЛИ, первым выходом блока и нулевыми входами триггеров первой групгш, а выход - через генератор тактовой частоты с входом распределителя импульсов и входом элемента задержки, выход которого является вторым выходом блока, первые входы элементов И первойf второй, третьей и четвертой групп соединены с вторым входом блока, вторые входы - соответственно с первым, вторым, третьим и четвертым выходами распределителя импульсов, а выходы - соответственно с первой, второй,третьей и четвертой группами входов дешифратора, первая и вторая группы выходов которого подключены сботЬетственно к первой и второй группам выходив блока;, а вход - к первому входу блока, выходы элементов И второй группы соединены с единичными входами триггеров второй группы, нулевые выходыкоторых соединены с выходом второго элемента ИЛИ, а выходы с вторьши входами соответствующих элементен И третьей группы, выходы которых соединены с группой входов второго элемента ИЛИ и единичными входами соответствующих триггеров

1

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для сопряжения ЭВМ с дискретными датчиками и/или каналами связи.

По основйому авт.св.9 824185 известно устройство для сопряжения, содержеияее коммутатор, rpynjia информационных вхбдов которогосоединена с группой ииформационяых входов ycTpottcfaa, группа адресных входов - с группой выходов дешифратора адреса группа входов которого подключена к группе шходов счетчика адреса и груп пе входов узла управления,первый,второй и третн:й выходы которого соединены соответственно с входами счетчика адреса, регистра и памяти адресов, группа выходов счетчика

адреса соединена с первыми входами эл кентов и группы, вторыми входами соединенных с выходом кс 4мутатора, а ва11ходами - с группами входов памяти адресов и счетчика текущего состояния датчиков, группы выходов которого подключена к группе входов регистра и первой группе входов схемы (равнения, вторая группа входов которой соединена с группой выхокоз регистра, а выход - с первым входом узла управления, вторым входе подключенного к выходу к эт4мутатора, выуХод памяти адресов соединен через д ешифратор адреса с а;феснУм выходом устройства (JLJ .

Недостаток этого устройства состоит в визкой достоверности передачи сообщений.

Целью изобретения является повышение достоверности передачи сообщений, . . .

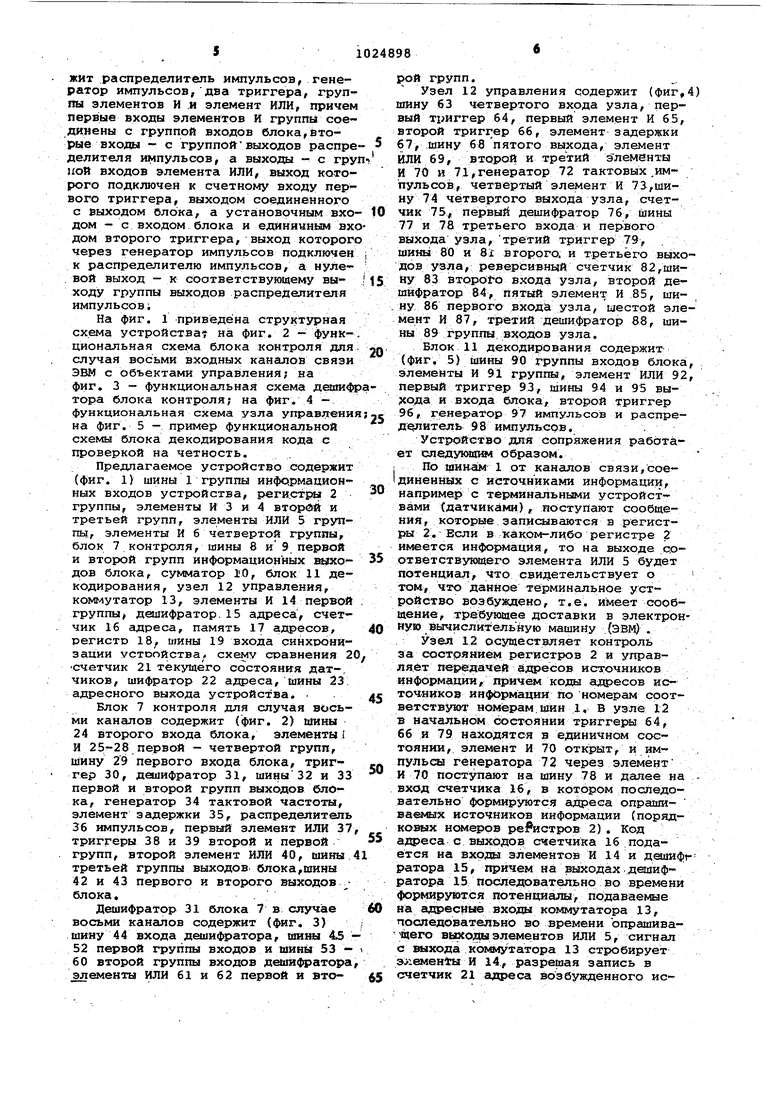

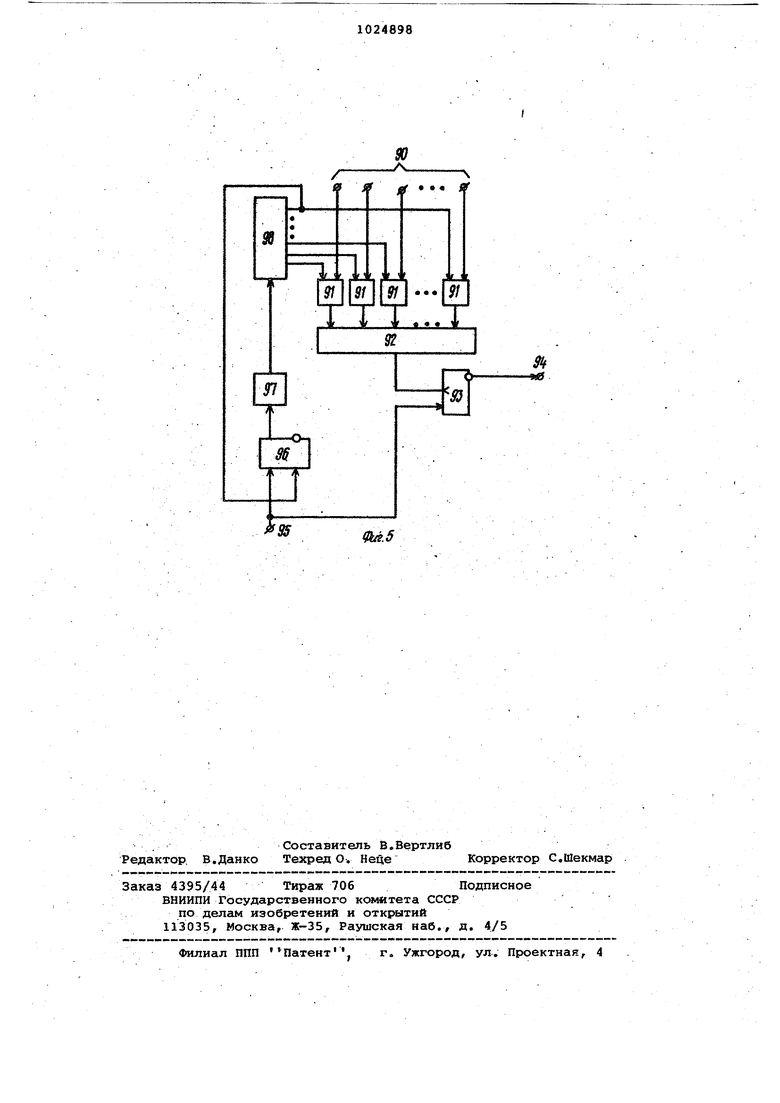

Поставленная цель достигается тем что в устройство введены .группа регистров, блок контроля, блок дёкодиро.вания, сумматор ц группа элементов ИЛИ, вторая, третья и четвертая группы элементов Иfпричем информацирлные входы регистров группы соединены с группой информационных входов устрой ства управляюшие входы - с четвер тым выходом узла управления, третий вход которого соединен с входом синхрониэации устройства/ а четвертый вход и пятый выход - роответст венно с первыми выходом и входом блока кантррЛ;Я f BToptae вхЬд и выход которого соединены соо тввтственно с выходо и входом блрка декодирования, группРЙ вхряов прдключенного к группе вы хрдрв суммат о| а / группы выходов регист рода г)руЬпы соединень с первыми входами элементо1в И, вторрй и,третьей груп и срртйететвукщИми входами элементрв ИЛИ группы, выходы котррых соедилены с ГРУППОЙ йнформа ционных входов коммутатрра, вьгхрдЫ; регистррв группы под;ключ ны к nepBifciM входам элементов И четвертой груп-пы,.выхояы элементов И и ;четвёртрй групп являются сос т-ветственнр дерврй и втррр;й группа 1и.информационных; выхрдов устройстйа. вторйаё входы элементов И второй, третьей и: четвертой групп срединены оойтвет-стйедно с первой, второй и.. третьей г5 |у;Ппами;выхрдов блока конт:ррля, выходы элементов И третьей :группы :сРединёны.с группой внходрв . .сумматора. , ;. : ; При этом, блок контроля соДержит четмре грулшл элет ентов И, дешифратор, две группы тр иггеров, два элемента ИЛИ, распределитель импульсрв, элемент 3адержки , генератор тактовой ча.стртй и триггер, причем единичный вход триггера соединен с перВШ4 ВХОДО.М :блрка, нулевой вход - е выходрм первого элемента ИЛИ, первым выхрдоМблрка .и нулевыми входами триггеров перврй группы, а выхрд - через генератор тактовой частоты с входом распределителя иштульсов и входом элемента з адержки, ВЫ.ХРД котррогр является ртррым выхрдрм блока, первые входы элементов. И первой, второй, третьей и четвертой групп соединены с вторым вхрдом блока, вторые входы - соответcTBiSHHO с первым, вторым, третьим и четвертым выходами распределителя импульсов, а выходы т соответственно с перврй, второй, третьей и Четвертой группами входов дешифж атора|г первая и втррая группы выходов крторого пРдключены соответственно ic первой и второй группам выходов блока,а вход-к первому входу блока,

выходы элементов И второй груп.пы соединены- с единичными входами триггеров второй группы, нулевые выходы которых соединены с выходом вторрго элемента ИЛИ, а выходы с втррыми входами соответствующих элементов И третьей группы, выходы которых соединены с группой входов второго элемента ИЛИ и единичными ,входами соответствующих триггеров первой группы, выходы которых подключены к третьим входам соответствющих элементов И четвертой группы, выходы крторых/ соединены с третьей группой выходов блока и группой вхо дов первого элемента ИЛИ, входом подключенного к соответствующего элемента И первой группы,

Кроме того, узел управления соде жит шесть элементов И,реверсивный счетчик, генератор тактрвых импульсов, счетчик, три дешифра1трра, три триггера, элемент ИЛИ и элемент задержки, причем нулевой вход первого триггера соединен с третьим входом .узла, единичный вход - с четвертым вхРдом узла и прямым входом первого элемента И, а нулевой выход - с первым входом элемента ИЛИ, п:тым входом узла и через элемент задержки с инверсньш входом первого элемеНта И, выходсял подключенного К; нулевому ВХОДУ втррого триггера, единичный вход которого соединен через первый дешифратор с выходом счетчика, выход элемента ИЛИ подключен к инверсному входу второго И, а второй вход - к-иуЛевому выходу второго триггера и первому входу третьего элемента И, вьисрдрм соединенного с четвертым выхрдом узла и входом счетчика,а вторым входом - с выходом генера,тора та ктовых импульсов, первым пря Мдм входом втррогр элемента И, вторым входом соединенного с вторым выходом узла и нулевым выходом третьего триггера, а выходом.- с третьим выходом узла и первым вхог дом реверсивного счетчика, второй вход кЬторюго прдклю чен к второму входу узла, третий вход - к выходу пятого .элемента И,, а выход - через втррой дешифратор к единичному вход третьего триггера, единичным выходсял срединенного с вторьм прямым входом второго элемента И, выход KOlTPporo является первым выходом узла, вызсод шестого элемента И соединен с нулевым входом третьего тригера, первый вхрд - с первым входом узла и инверсным входом пятого элемента И, а второй вход - с прямым входом пятого элемента И и выходом т4 етьего дешифратора, группа входов , которого является группой входов узла, ; Причем блок декодирования содержит распределитель импульсов, генератор импульсов,два триггера, группы элементов И .и элемент ИЛИ, причем первые входы элементов И группы соединены с группой входов блока,ВТОрые входы - с группойвыходов распре делителя импульсов, а выходы - с гру иой входов элемента ИЛИ, выход которого подключен к счетному входу первого триггера, выходом соединенного с выходом олока, а установочным вхо дом - с входом блока и единичным вх дом второго триггера, выход которог через генератор импульсов подключен к распределителю импульсов, а нулевой выход - к соответствующему вы ходу группы выходов распределителя импульсов; На фиг. 1 приведена структурная сх.ема устройства на фиг. 2 - функциональная схема блока контроля для случая восьми входных каналов связи ЭВМ с объектами управления; на фиг. 3 - функциональная схема я&акф тора блока контроля; на фиг. 4 - функционашьная схема узла управя-ени на фиг. 5 - пример функциональной схемы блока декодирования кода с проверкой на четность. . Предлагаемое устройство содержит (фиг. 1) шины 1 группы информационных входов устройства, регистры 2 группы, элементы И 3 и 4 второй и третьей групп, элементы ИЛИ 5 группы, элементы И 6 четвертой группы, блок 7 контроля, шины 8 и§ первой и второй групп информационных mjxoдов блока, сумматор 10, блок 11 декодирования, узел 12 управления, коммутатор 13, элементы И 14 первой группы, дешифратор. 15 адреса , счетчик 16 адреса, память 17 адресов, регистр 18, шины 19 входа синхронизации устройства.4 схему сравнения 2 счетчик 21 текущего состояния дат-, чиков, шифратор 22 адреса, шины 23: адресного выхода устройства. . Блок 7 контроля для случая восьми каналов содержит {фиг. 2) шины 24 второго входа блока, элементы И 25-28 первой - четвертой групп, шину 29 первого входа блока, триггер 30, дешифратор 31, шины 32 и 33 первой и второй групп выходов блока, генератор 34 тактовой частоты, элемент згшержки 35, распределитель 36 импульсов, первый элемент ИЛИ 37 триггеры 38 и 39 второй и первой групп, второй элемент ИЛИ 40, шины третьей группы выходов блока,шины 42 и 43 первого и второго выходов блока. Дешифратор 31 блока 7 в случае восьми каналов содержит (фиг. 3) шину 44 входа дешифратора, шины 45 52 первой группы входов и шины 53 60 второй группы входов дешифратора элементы ИЛИ 61 и 62 первой и втоой групп. Узел 12 управления содержит (фиг,4) ину 63 четвертого входа узла, первый триггер 64, первый элемент И 65, второй триггер 66, элемент задержки 67, шину 68 пятого выхода, элемент ИЛИ 69, второй и третий элементы И 70 и 71,генератор 72 тактовых .импульсов, четвертый элемент И 73,шину 74 четвертого выхода узла, счетчик 75, первый дешифратор 76, шины 77 и 78 третьего входа и первого выхода узла,третий триггер 79, шияь 80 и 8i второго, и третьего выходов узла,: реверсивный счетчик 82,шину 83 BTppoto входа узла, второй дешифратор 84, пятый элемент И .85, шиНУ 86 первого входа узла, шестой элемент И 87, третий дешифратор 88, шины 89 группы входов узла. Блоки декодирования содержит (фиг, 5) шины 90 группы входов блока, элементы И 91 группы, элемент ИЛИ 92, первый триггер 93, шины 94 и 95 выХРда и входа блока, второй триггер 96, генератор 97 импульсов и распре- деятель 98 импульсов. . Устройство для сопряжения работает следукяйши Образом. По шинам 1 от каналов связи,соединенных с источниками информации, например с терминальными устройствами (датчиками), поступают сообщения, которые записываются в регистры 2. Если в каком-либо регистре 2 имеется информация, то на выходе с,оответствукицего элемента ИЛИ 5 будет потенцисШ, что свидетельствует о том, что данное терминальное устройство возбуждено, т.е. имеет сообщение, требующее доставки в электронную вычислительную Машину .(ЭВМ) . Узел 12 осуществляет контроль за состоянием регистров 2 и управляет передачей источников информации, причем кода агв)есов источников информации по номерам соответствуют номерам шин 1, В узле 12 в начальном «зостояНИИ триггеры 64, 66 и 79 находятся в единичном состоянии, элемент И 70 открыт, и им- . пульсы генератора 72 через элемент и 70 поступают на шину 78 и далее на вход счетчика 16, в котором последовательно формируются аДрееа опрашиваемых источников информации (порядковых номеров регистров 2). Код адреса с выходов счетчика 16 подается на входы элементов И 14 и дааифг ратора 15, причем на выходах .дешифратора 15 последовательно во времени формируются потенциалы, подаваемые на адресные входы коммутатора 13, последовательно во времени опрашива tsero вьЕКодыэлементов ИЛИ 5, сигнал с выхода коммутатора 13 стробирует элементы И 14, разрешая запись в счетчик 21 гихреса возбужденного источника информации, причем этот адрес одновременно записывается в память 17, а сигнал с шины 83 заносит в реверсивний счетчик 82 очередную -единицу. В течение цикла опроса состояний элементов ИЛИ 5, которые отражают СОСТОЯНИЯ регистров 2 адреса возбужденных нсточниковпросуммируются в счетчике 21 и последовательно запишутся в память 17. Как только в счетчике 16 сформируется адрес по- . следнего источника , сработает дешифратор 88 и выдаст сигнал в схему сравнения 20 для сравнения кода записанного в счетчике 21, и кода хегистра 18, хранящего состояние источников на предыдущем цикле опроса В случае несовпадения кодов схема ср нения 20 выдаёт сигнал, указыванндий что в данном цикле опроса состояний источников информации , по меньшей ме ре,- один из них изменил состояние, и есть необходимость передачи адр1есо возбужденных источников в ЭВМ. При сов падении кодов нулевой сигн1ал с выхода схемысравнения 20 подается на шине S6 открывает элемент И 85.и сбрасывает рвеверсивнйй счетчик 82 в нулевое состояние, после чего узел 12 начина еледувэдйй цикл опроса состояний исто -НИКОВ информации. .Если же на шину 86 подается едйнич-, ный сигнал tкоды не равны), то элемент И 85 будет заперт, а через элемент И 87 триггер 79 перебросится в нулевое состояние. При этом элемент И 70 будет заперт, но будет открыт элемент И 73, кроме того, сигнал с нулевого выхода триггера 79 поступ;ает через шину 80 на вход регистра 18 разрешая запись кода счетчика 21 в peiHCTp 18 с. одновременнЕлм стиранием предыдущей информации. Импульеял гене ратора 72 поступают через открытий элемент И 73 и шину 81 на вычитающий вхЬд реверсивного счетчика 82 и йа вход памяти 17, с выхода которого ад состояний возбужденных источников информации считываются через шифратор 22 по шине 23 в ЭВМ. Когд:а будет считан последний адрес, в реверсивном счетчике 82 будет также считана последняя единица, так число единиц в счетчике 82 будет равно числу адресов в памяти 17,При нулевом состоянии реверсивного счетчика 82 на выходе дешифратора 84 появляется сигнал, по которсжу триггер 79 перебрас лвается в исходное единичное состояние, после чего узел 12 оказывается подготовлен к очередирму циклу опроса состояний источников информации. ЭВМ, получив по шине 23 информа. дш) о наличии сообщений выдает по шине 19 запас на передачу сообщений из регистров 2 в ЭВМ. Импульс запроса по шине 19 поступает на шину 77 и перебрасывает триггер 64 в нулевое состояние. Через элемент ИЛИ 69 элемент И 70 запирается и тем самьв прекращает цикл опроса; при этом по шине 68 на шину 29 блока 7 подается сигнал, переб асывакоций триггер 30 в единичное состояние (фиг. 2). Блок 7 осуществляет управление проверкой на достоверность принятых слов сообщений в регистрах 2, передачей слов без искажений в ЭВМ и передачей слов с искажением обратно в ЭН. Пусть слово сообщения передается кодам с проверкой на четность. Число первых входных шин,например равно восьми. При перебросе триггера 30 в единичное состояние начинает работать генератор 34, импульсы с выхода которого подаются на вход распределителя 36 и на вход элемента задержки 35 времени.. Кроме того, импульс поступает по шинам 29 и 44 ца соответствукаций вход дешифратора 31, сигналы на выходных шинах 33 которого разрешают перепись информации регистров 2 через элементы И 4 в сумматор 10, в котсфом формируется сумма этих кодов.. Сумма кодов подается в блок 11 по шинам 90 (фиг. 5). Импульс генератора 34 через элемент задержки 35 (задержка осутествляется на время формирования сумк&2 и декодирования) по шине 43 поступает на шину 95 блока 11, в котором триггер 96 перебрасывается в единичное состояние и запускает генератор 97. Импульсы генератора 97 подаются на вход распределителя 98, импульсы с выходов которого последовательно опрашивают шины 90, позволяя триггеру 93 осуществлять подсчет единиц. Если число единиц четное, т.е. нет ошибок, то на шине 94 блока 11 будет нулевой потенциал, а если число единиц нечетное; т.е. какая-то кодовая комбинация имеет ошибку, то на шине 94 будет единичный потенциал. Сигнал .с последнего выхода распределителя 98 сбрасывает триггер 96 в Исходное нулевое состояние и останавливает генератор 97. Если кодовые комбинации регистров 2 не содержат схиибок, -то. с шины 94 нулевой потенциал подается на шину 24 блока 7. При этом на первом выходе распределителя 36 будет потенциал f отк «шаювдай первый элемен т И 25 ,и на шину -45 дооифратора 31 подается потенциал, разрешающий выдачу на ишны 32 потенциалов для по дачи сообщений из регистров 2 через соответствующие элементы И 3 на шины 8 в ЭВМ Крсте того, потенциал с выхода первого эле данта и 25-f через элемент ИЛИ 37 сбрасывает триггер 30 в нулевое состояние и по шине 42 подается на шину 63 узла 12. Если среди кодовых комбинаций регистров 2 имеется ошибочная, то с шины 94 блока 11 единичный потенциал подается на шину 24 блока 7. При этом на первом выходе распределител 36 будет потенциал, следовательно второй элемент И 252 УД открыт, и потенциал с его выхода поступает по шине 46 на вход дешифратора 31. На шинах 33 блока 7 будут потенциалы., разрешающие запись кодов из регистров 24. через элементы И 4 в сумматор 10. Сумма сумматора 10 подается в блок 11, на шину 95 котор го подается второй импульс генератора 34 , задержанный элементом задержки 35. Если ошибки в данных кодовых комбинациях нет, то на шину 24 блока 7 подается ч нулевой потенциал с выход блока 11. В этом случае срабатывает первый элемент И 26 / так как на его входе будет разрешающий потенциал с второго выхода распр делителя Зб. По тенциал с выхода первого элемента И 26 перебросит первый триггер 38 единичное состояние и поступит по ши 47 на вход дешифратора 31. Так как нет ошибок в -словах первых четырех : регистров 2f- 2 , то они могут быт переданы в ЭВМ, а слова пятого - во мого регистров; 2 - 2g должйы быть проанализированы. В этом случае потенциалы будут на шинах 3,24-322 и шинах 335- 33 блока 7, т.е. коды регистров 2v(- 2 через элементы ИЗ подаются в ЭВМ через шины 8 , а коды регистров 25 - 2 подаются через элементы И 4 в сумматорЮ. Если же в одном из регистров находится сообщение с ошибкой, то на шине 24 единичный сигнал с выхода блока 11 открывает элемент И 26,сигнал с выхода которого перек чает триггер 382 1В единичное положе ние и поступает по шине 48 на вход дешифратора 31. В предложении, что ошибка может быть в одной кодовой комбинации, в регистрах 25- 2g хранятся коды без ошибок, и эти :коды можно переслать В ЭВМ, а коды регистров 2 еледует дальше анёшизировать. Поэтому на шинах 325- 32 и шина 33i- 332 блока 7 формируются сигналы Чтобы выдать коды регистров через элементы И 3 на шины 8 и для передачи в ЭВМ, а коды регистров 2ч через элементы И 4 подаются в сумматор 10.Из сумматора 10 сумма двух кодов подается в блок 11 на шину 95 которого подан в это вре мя задержанный третий импульс ге- нератора 34 блока 7. Если, например сяйибка имеется в кодовой комбинации J содержащейся в регистре 2 з г то с выхода блока 11 подается на шину 24 нулевой потенциал. Учитывай, что триггер 382 нахор,нт:ся в единичном состоянии, то импульс на третьем выходе распределителя 36 открывает элемент И 2k, с выхода которого сигнал на шине 51 через дешифратор 31 перебрасывает триггер 39 в единичное состояние и через элемент ИЛИ 40 сбрасывает триггер 382 в нулевое состояние, Сигнсшы на шинах 32;j и 322 и шине 33 разрешают передачу верных кодовых комбинаций регистров 2 и 2/2 через элементы И 3 и шины 8 и 8г в ЭВМ, а кодовая комбинация регистра Zj через элементы И 4 подается в сум(МаторЮ. Код регистра 2 из суммаJTopa 10 подается в блок 11, на шину. 95 которого в это время подается {четвертый потенциал генератора 34 блока-7. Если код регистра 2 имеет ошибку, то на шину 24 блока 7 подают единичный потенциал, и срабатывает элемент И .28g. Потенциал с его выхода ; подают на шину 58 дешифратора 31 и на шину 41з блока 7, На шине 32 блока 7 будет потенциал, который разрешает передачу кода регистра 24 черезэлементы ИЗ и шину 84 в ЭВМ. Потенциал с шины 41з открывает элемен.т И 6,кроме того,потенциал с выхода элемента И 28 через элемент ИЛИ 37 сбрасывает триггеры ЗЭ и 30 в нулевое состояние, и поступает на шину 42 и останавливает поиск блоком 7 ошибочной комбинации. Потенциал на шине 42 с выхода блока 7 поступает на шину 63 уэла 12 и установит триггер 64 висходное . единичное- состояние. Так элемент задержки 67 времени задержзгвает фронт потенциала, снимаемого с нулевого выхода триггера 64 на время, равное длительности периода следова- V ния импульсов, генератора 34, то элемент И 65 сработает, перебросит триггер 66, и -импульс с нулевого выхода триггера 66 откроет элемент и 71. Импульсы от генератора 72 через элемент И 71 подаются на шину:74 .узла . 12 и на вход счетчика 75. Счетчик 75 отсчитывает число тактовых импульсов необходимых для считывания искаженной КОДОВОЙ комбинации, из рбгистра 2з через элемент И 6 и возбуждает шину 90 , Затем срабатывает дешифратор 76, и триггер 66 сбрасывается в исходное .единичное состояние. На выходе элемента ИЛИ 69 будет нулевой потенциал,элемент И 70 будет открыт, и узел 12 заново начинает опрашивать состояния регистр ров 2. Считанная по тактовым импульсгиу, подаваемым ho шине 74, из регистра

2j ошибочная комбинация передается по шине 9д к-источнику информации, где после корректировки возможна последующая ее передача к устройству для сопряжения с ЭВМ.

Л 8i 8я 9л а 0 0 J

I

Таким образом, предложенное устройство обеспечивает опрос состоя-НИИ и вывод информации от источников информации в ЭВМ с более .высокой по сравнению с известным достоверностью. Vb ад i ii i ,/,« //«/,«/./, Зг Хг Jfj з; J2ff Jf Х7 }2в JJf 33t Лз Х- Т г Т Т f . Т Т т Л JJj Д JWr Д) т т т

S5

Ш.5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сопряжения | 1979 |

|

SU824185A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-06-23—Публикация

1982-01-25—Подача