I

Изобретение относится к аналоговым cpcjj,ствам автоматики и вычислительной техники и может быть использовано в электронных Моделирующих устройствах и системах автоматического управления, например, движущимися объектами, когда требуется определить значение периодической функции по скорости изменения ее аргумента, а в некоторых случаях и номер периода, в котором находится значение этого аргумента.

Известны интегрирующие устройства, содержащие два одинаковых интегрирующих конденсатора, один из которых включает в НС-цепь рещающего усилителя, в то время как другой с помощью дополнительно введенного сумматора разряжают до нуля или до граничного напряжения U . Каждый раз, когда выходной сигнал усилителя достигает любой из указанных границ (О или УН ), конденсаторы меняют местами при помощи схемы управлЙ1идинтегрирующего устройства. Тем самым обеспечивается скачкообразное изменение выходного сигнала интегрирующего устройства 1.

Основными недостатками таких устройств являются уменьшение возможного масштаба выходного сигнала, сложность схемы управле1гая а.также необходимость в двух прецизионных конденсаторах, что увеличивает вес и габариты устройства. Кроме того, различие в фактических отклонениях елгкостей двух конденсаторов от номинала может вызвать дополнительные погрешности интегрирования, поскольку эта отклонения не могут быть скомпенсированы подстройкой сопротивления резистора RC-цепи; этот недостаток можно устранить лииа за счет еще большего усложнения схемы - введения второго входного резистора и элементов переключения входных резисторе.

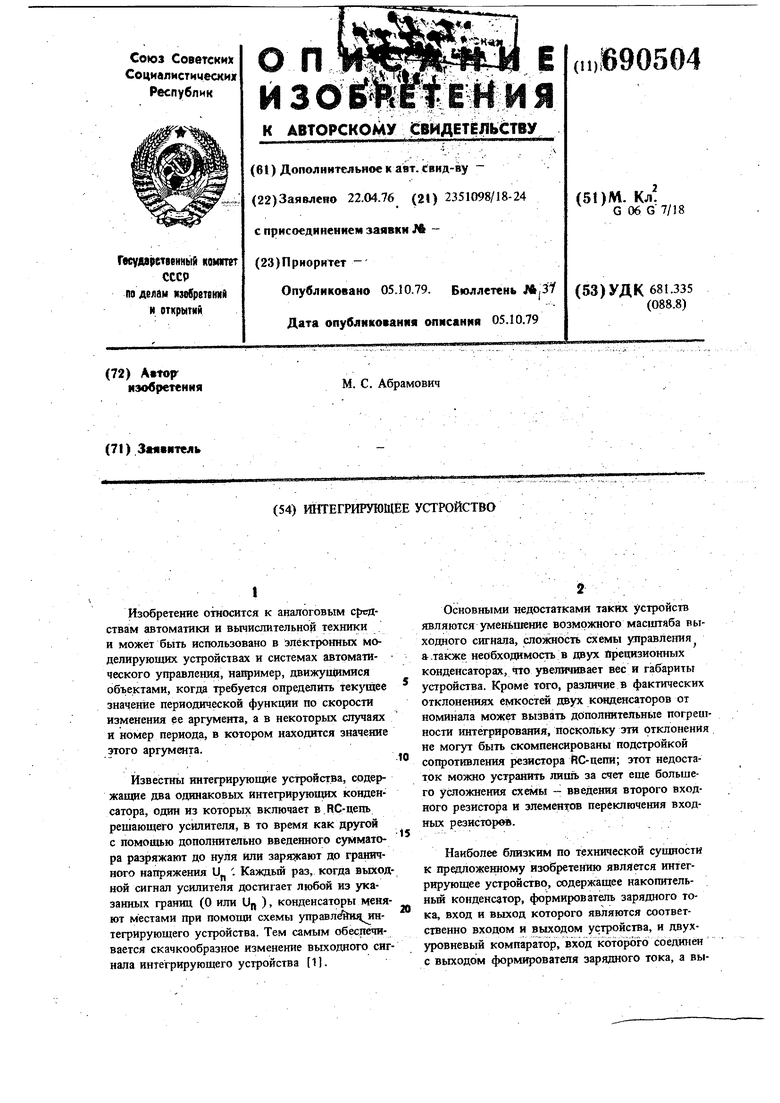

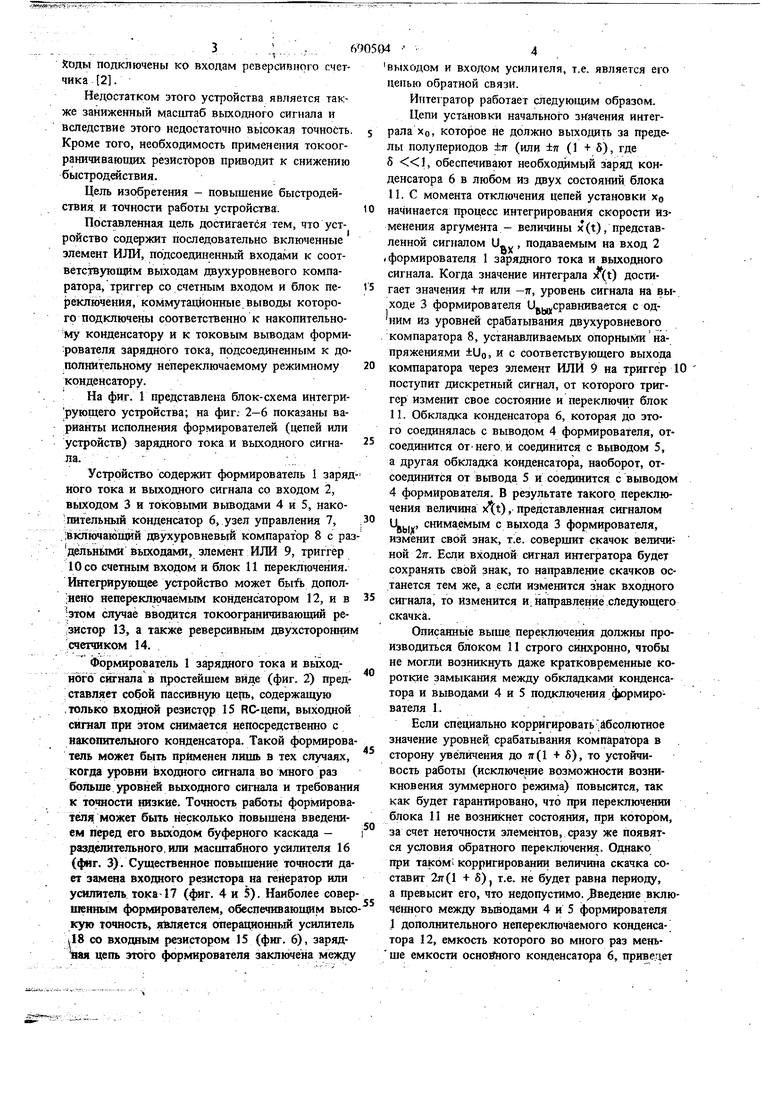

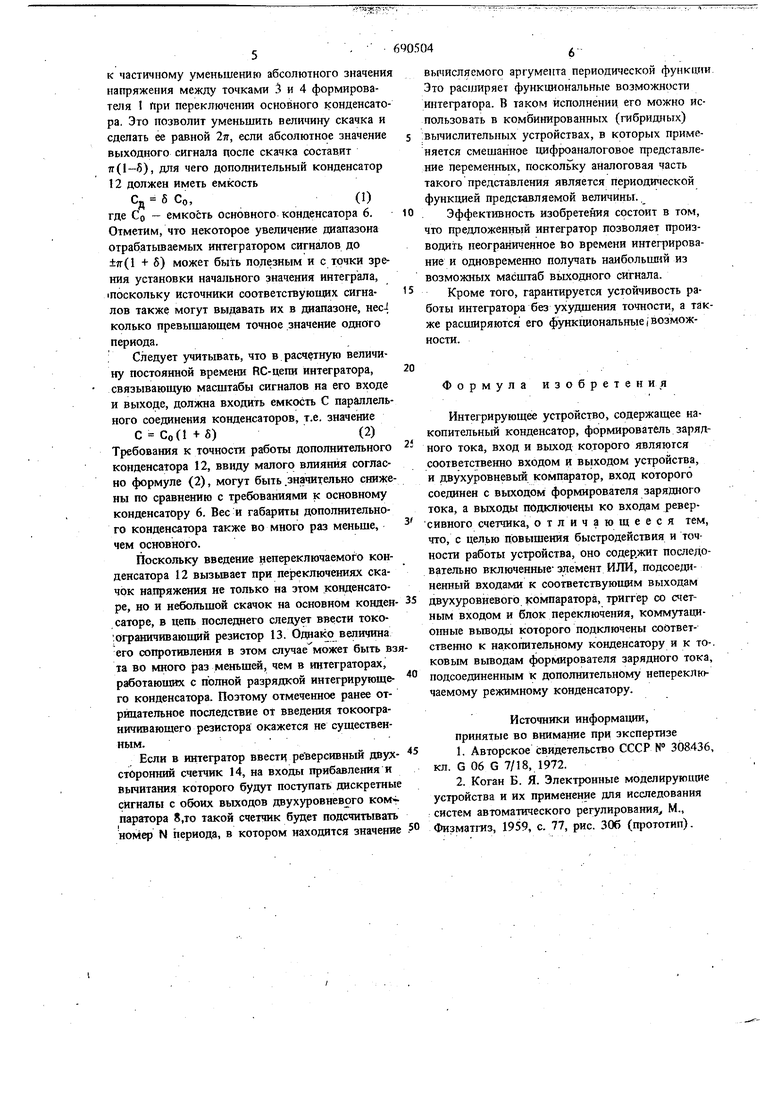

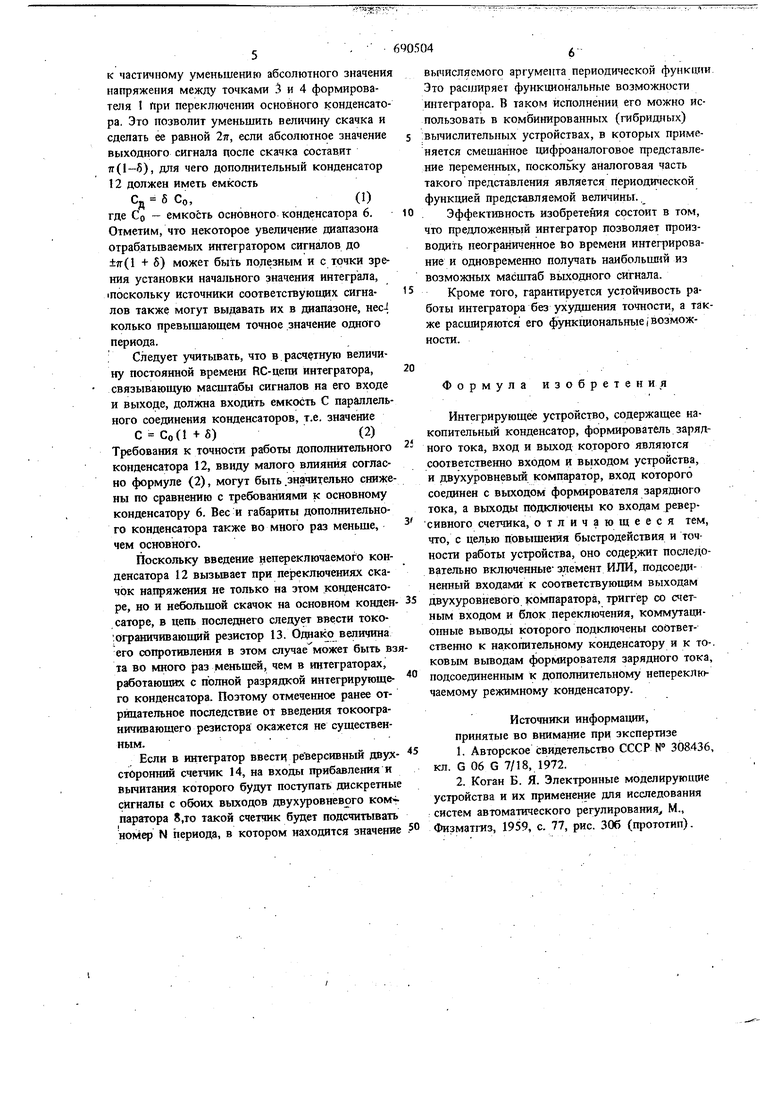

Наиболее близким по технической сущности к предложенному изобретению является интегрирующее устройство, содержащее накопительиый конденсатор, формирователь зарядного тока, вход и выход которого являются соответственно входом и выходом устройства, и двухуровневый компаратор, вход которого соединен с выходом формирователя зарядного тока, а выХоды подключены ко входам реверсивного счетчика 2. Недостатком этого устройства является также заниженный масштаб выходного сигнала и вследствие этого недостаточно высокая точность. Кроме того, необходимость применения токоограничивающих резисторов приводит к снижению быстродействия. Цель изобретения - повышение быстродействия и точности работы устройства. Поставленная цель достигается тем, что устройство содержит последовательно включенные элемент ИЛИ, подсоединенный входами к соответствующим вь1ходам дв тсуровневого компаратора, триггер со счетным входом и блок переключения, коммутационные выводы которого подключены соответственно к накопительному конденсатору и к токовым выводам формирователя зарядного тока, подсоединенным к дополнительному непереключаемому режимному конденсатору. . На фиг. 1 представлена блок-схема интегрирующего устройства; на фиг. 2-6 показаны варианты исполнения формирователей (цепей или устройств) зарядного тока и выходного сигнала. ;..: Устройство содержит формирователь 1 заряд кого тока и выходного сигнала со входом 2, выходом 3 к токовыми вьшодами 4 и 5, нако пительный конденсатор 6, узел управления 7, включающий двухуровневьй компаратор 8 с раз дельньпия выходами, элемент ИЛИ 9, триггер 10 со счетным входом и блок 11 переключения. Интегрирующее устройство может бый. дополнено непереключаемым конденсатором 12, и в :этом случае вводится токоогранитавающий редастор 13, а также реверсивным двухсторонним счетчиком 14. Формирователь 1 зарядного тока и выходного сигнала в простейшем виде (фиг. 2) пред:Ставляет собой пассивную церь, содержащую .только входной резнстфр 15 RC-цепи, выходной сигнал при этом снимается непосредственно с накопительного конденсатора. Такой формирова тель может быть применен лишь в тех случаях, когда уровни входного сигнала во много раз больше уровней вькодного сигнала и требовани к точности низкиб. Точность работы формирова теля может быть несколько повышена введением перед его выходом буферного каскада разделительного, или масштабного усилителя 16 (фиг. 3). Существенное повышение точности да ет замена входного резистора на генератор или усилитель тока-17 (фиг. 4 и 5). Наиболее совер шенным формирователем, обеспечивающим выс кую точность, я)вляется операционный усилитель il8 со входным резистором 15 (фиг. 6), зарядная цепь этого формирователя заключена между

690504 выходом и входом усилителя, т.е. является его епью обратной связи. Ит1тегратор работает следующим образом. Цепи установки начального значения интеграла Хо, которое не должно выходить за предеы полупериодов ±ir (или ±л (1 +6), где 5 «1, обеспечивают необходимый заряд коненсатора 6 в любом из двух состояний блока П. С момента отключения цепей установки хо начинается процесс интегрирования скорости изменения аргумента - величины x(t), представленной сигналом и,, подаваемым на вход 2 формирователя 1 зарядного тока и выходного сигнала. Когда значение интеграла (t) достигает значения +я или -тг, уровень сигнала на выходе 3 формирователя и сравнивается с одним из уровней срабатывания двухуровневого компаратора 8, устанавливаемых опорными напряжениями ±Uo, и с соответствующего выхода компаратора через элемеит ИЛИ 9 на триггер 10 поступит дискретный сигнал, от которого триггер изменит свое состояние и переключит блок 11. Обкладка конденсатора 6, которая до этого соединялась с выводом 4 формирователя, отсоединится От-него, и соединится с выводом 5, а другая обкладка конденсатора, наоборот, отсоединится от вьгеода 5 и соединится с выводом 4 формирователя. В результате такого переключения величина ), представленная сигналом , снимаемым с выхода 3 формирователя, изменит свой знак, т.е. совершит скачок величиной 27г. Если входной сигнал интегратора будет сохранять свой знак, то направление скачков останется тем же, а если из 1енится знак входного сигнала, то изменится и. направление следующего скачка. Описанные выше переключения должны производиться блоком И строго синхронно, чтобы не могли возникнуть даже кратковременные короткие замыкания между обкладками конденсатора и выводами 4 и 5 подключения формирователя 1. Если специально корригироватьабсолютное значение уровней, срабатывания компаратора в сторону увеличения до 7г(1 + 6), то устойчивость работы (исключение возможности возникновения зуммерного режима) повысится, так как будет гарантировано, что при переключении блока II не возникнет состояния, при котором, за счет неточности элементов, сраэу же появятся условия обратного переключения. Однако при таком; корригировании величина скачка составит 27г(1 + 5)j т.е. не будет равна периоду, а превысит его, что недопустимо, ведение включйшого между вьшодами 4 и 5 формирователя 1 дополнительного непереключаемого конденсатора 12, емкость которого во много раз меньше емкости основного конденсатора 6, приведет К частичному уменьшению абсолютного значения напряжения между точками 3 и 4 формирователя 1 При переключении основного кондеисатора. Это позволит уменьшить величину скачка и сделать ее равной 27г, если абсолютное значение выходного сигнала после скачка составит 7г(1-5), для чего дополнительный конденсатор 12 должен иметь емкость Сд 5 Со,(1) где Со - емкость основного конденсатора 6. Отметим, что некоторое увеличение диапазона отрабатьшаемых интегратором сигналов до ±7г(1 + 5) может быть полезным и с точки зрения установки начального значения интеграла, Поскольку источники соответствуюших сигналов также могут выдавать их в диапазоне, нес4 колько превышающем точное значение одного периода. Следует учитывать, что в расчетную величину постоянной времени RC-цепи интегратора, связывающую масштабы сигналов на его входе и выходе, должна входить емкость С параллельного соединения конденсаторов, т.е. значение С Со(1 +6)(2) Требования к точности работы дополнительного конденсатора 12, ввиду малого влияния согласно формуле (2), могут быть .значительно снижены по сравнению с требованиями к основному конденсатору 6. Вес и габариты дополнительного конденсатора также во много раз меньше, чем основного. Поскольку введение неперекпючаемого конденсатора 12 вызывает при переключениях скачок напряжения не только на зтом конденсаторе, но и небольшой скачок на основном конденсаторе, в цепь поспедаего следует ввести токо;ограничивающий резистор 13. Однако величина его сопротивления в этом случае может быть вз та во много раз меньшей, чем в интеграторах, работающих с полной разрядкой интегрирующего конденсатора. Поэтому отмеченное ранее отрицательное последствие от введения токоограничивающего резистора окажется не существенным. Если в интегратор ввест реверсивный двухсторонний счетчик 14, на входы прибавленияи вычитания которого будут поступать дискретные сигналы с обоих выходов двухуровневого ком гпаратора 8,то такой счетчик будет подсчитывать номер N периода, в котором находится значение вычисляемого аргумента периодической фуЕжиии Это расширяет функциональные возможности интегратора. В таком исполнении его можно использовать в комбинированных (гибридных) :вычислительных устройствах, в которых применяется смешанное цифроаналоговое представление переменных, поскольку аналоговая часть такого представления является периодшшской функцией представляемой величины. Эффективность изобретения состоит в том, что предложенный интегратор позволяет производить неограниченное йо времени интегрирование и одновременно получать наибольший из возможных масштаб выходного сигнала. Кроме того, гарантируется устойчивость работы интегратора без ухудшения точности, а также расширяются его функциональные j возможности. рмула изобретения Интегрирующее устройство, содержащее накопительный конденсатор, формнроватйль зарядного тока, вход и выход которого являются соответственно входом и вь1ходом устройства, и двухуровневый компаратор, вход которого соединен с выходом формирователя зарядного тока, а выходы подключены ко входам реверсивного счетчика, отличающееся тем, что, с целью повышения быстродействия и точности работы устройства, оно содержит последовательно включенные- элемент ИЛИ, подсоединенный входами к соответствующим выходам двухуровневого компаратора, триггер со счетным входом и блок переключения, коммутациО1шые вьшоды которого подключены соответственно к накопительному конденсатору и к то-, ковым вьгеодам формирователя зарядного тока, подсоединенным к дополнительному неперекп чаемому режимному конденсатору. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 308436, кл. G 06 G 7/18, 1972. 2.Коган Б. Я. Электронные моделирующие устройства и их применение для исследования систем автоматического регулирования, М., Физматшэ, 1959, с. 77, рис. 306 (прототип).

. i

. .

-X59 5«4 .

.:4..,..

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| ИНТЕГРИРУЮЩИЙ ИЗМЕРИТЕЛЬ ОТНОШЕНИЯ ДВУХ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1992 |

|

RU2032884C1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1559407A2 |

| Измеритель коэффициента нелинейности пилообразного напряжения | 1980 |

|

SU894607A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛА ВРЕМЕНИ В ПОСТОЯННОЕ НАПРЯЖЕНИЕ | 1990 |

|

RU2007028C1 |

| ИНТЕНСИМЕТР С АВТОМАТИЧЕСКИМ ПЕРЕКЛЮЧЕНИЕМ | 1972 |

|

SU354379A1 |

| СПОСОБ ВИХРЕТОКОВОГО КОНТРОЛЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2365910C2 |

| Преобразователь сопротивления резистивного датчика в период следования импульсов | 1979 |

|

SU879503A1 |

| Интегратор | 1982 |

|

SU1062726A1 |

r 6:

ic

J3

LJj:l -i 4 . 2 5

17 fS

3 г

O ff

Фиг.5

.

(4

П

; LbC±30i/2.

I

Из-H

u :Фиг л

15 К/

iJ

уг.б

Авторы

Даты

1979-10-05—Публикация

1976-04-22—Подача