Изобретение относится к автоматике и измерительной технике и может быть использовано в цифровых системах измерения площади статически распределевных видеоимпульсов с медленно меняющейся во времени амплитудой} и длительностью.

Известен интегратор, состоящий из операционного усилителя и интегрирующего конденсатора, включен ного в цепь обратной связи рпера1ЩОННОГО усилителя Cl Т. Одним из недостатков такого устройства является ограниченный динамический диапазон интегрируемых сигналов Для рас ширения динамического диапазона в цепь обратной связи включают группу конденсаторов и ключей и применяют соответствующее устройство управления. Переключение конденсаторов про исходит при достижении выходным на пряжением определенного .уровня.

Невысокое быстродействие современных операционных усилителей не позволяет строить высокочастотные интеграторы видеоимпульсов длительностью единиц микросекунд. Описанному устройству также свойственны погрешности/ связанные с переходнБЯУШ процессами при переключении накопительных конденсаторов во время действия входного сигнала.

Известен интегратор, состоящий из блока преобразования напряжения интегрируемого сигнала в ток: и накопительного кoндeнcaтopat2J.

Недостатке такого интегратора является ограниченный динамический диапазон интегрируемых сигналов.

Наиболее близким к предлагаемся интегратору является интегратор, состоящий из последовательно соединенных блока преобразования напряжения в ток и аналогового ключа. Между выходом аналогового ключа и общим проводом параллельно включены интегрирующий конденсатор и генератор стабильного -разрядного тока Формирователь управляющего сигнала подключен к управляющему входу аналогового ключа. В .исходнс состояни интегрирующий конденсатор разряжен. В данном интегратора реализуется принцип двухта ктного интегрирования В т:ечеиие первого такта, длитеяь ность которого определ яется длительностью импульса, подаваемого на формирователь управляющего сигнала внаяним устройством, происходит заряд конденсатора током, пропорциональным входнс |у напряжению, а в течение второго такта - разряд стабильным токсил до исходного состояния. В течение первого такта ключ. замкнут, а генератор разрядного тока закрыт ynpajiляющим сигиалом и . не влияет нд заряд,конденсатора. В

течениевторого такта ключ .разомкнут, а генератор стабильного тока включен. Нетрудно показать, что.За время действия входного видеоимпульса t конденсатор С зарядится до напряжения

11%

(t)cft ,

где К - коэффициент передачи блока преобразования напряжения в ток; Ugy (t) - напряжение входного видеоимпульса fSj.

очевидно, что время разряда конденсатора стабильным током до исхо дного состояния составит

t . К

I

Ti

(tjeJt.

раз

Таким образом, длительность импульса на выходе интегратора оказывается пропорциональной площади вход5ного сигнала.

Однако интегратор имеет ограниченный динамический диапазон точного измерения площадей входных сигналов, кроме того, необходим сигнал синхро0низации.

Ограниченность динамического диапазона вытекает из того, что мсалент разряда интегрирующего конденсатора до исходного состояния фиксируется

5 компаратором с сядибкой. Позтому существует некоторое нгшменьшее время разряда интегрирующего конденсатора, фиксируемое с точностью не хуже заданной. Максимальное же время разряда определяется максимальным напря0жением, до которого может зарядиться конденсатор в течение первого такта. Очевидно, что это напряжение не может быть больше, чем напряжение питания блоке преобразования напряже5ния в ток.

Целью изобретения является расширение динамического диапазона интег рируемого сигнала.

Указанная цель достигается тем,

0 что в Интегратор, содержащий последовательно соединенные преобразователь напряжения в ток и первый лхн, между выходом которого и шиной нуле- вого потенциала включен генератор

5 тока, интегрирунхций конденсатор,одна обкладка которого соединена с .шиной нулевого потенциала, формирователь управлякяких импульсов,выход которого соединен с управляющим вхо

0 дом первого ключа, введены компаратор, второй ключ, пороговый блок, интегрирующий блок, коммутатор, группа интегрирующих конденсаторов, блок памяти, дешифратор, блок выделения заднего фронта, групг

5

па компараторов и источник опорных нат ряжений, выходы которого подклвдчены к первым входам компараторов труппы,вторые входы которых соединены с выходом интегрирующего блока,вход инг тегрирующего блока и вход порогового блока подключены к выходу второго. ключа, вход которого является входом интегратора, а управляющий вход соединен с выходом формирователя уп- .Q равлякнцих импульсов, выход порогового блока соединен с установочнь входом интегрирующего блока, первьм входом фО лирователя управляющих импульсов и через блок выделения задне-. го фронта с управлякяцим входом блока, псшяти, выходы которого являются выходами кода поддиапазона интегратора и подключены к управляющим входа кс 1мутатора, а выходы через дешифратор соединены с выходами ком-, 20 параторов группы, вход коммутатора подключен к выходу первого ключ, первый выход - к второй обкладке интегрирующего конденсатора, а другие выходы через соответствующий ин- ,25 тегрирующий конденсатор группы - к шине нулевого потенциала, входы компаратора соединены соответственно с выходом преобразователя напряжения в ток и выходом первого ключа, выход,30 являющийся выходом аналогового йитегратора, подклю1чен к второму входу формирователя управляющих импульсов и блокировочным входом генератора тока, а стробирующий вход - к вьрсо- 35 ду формирователя управляющих импульсов.

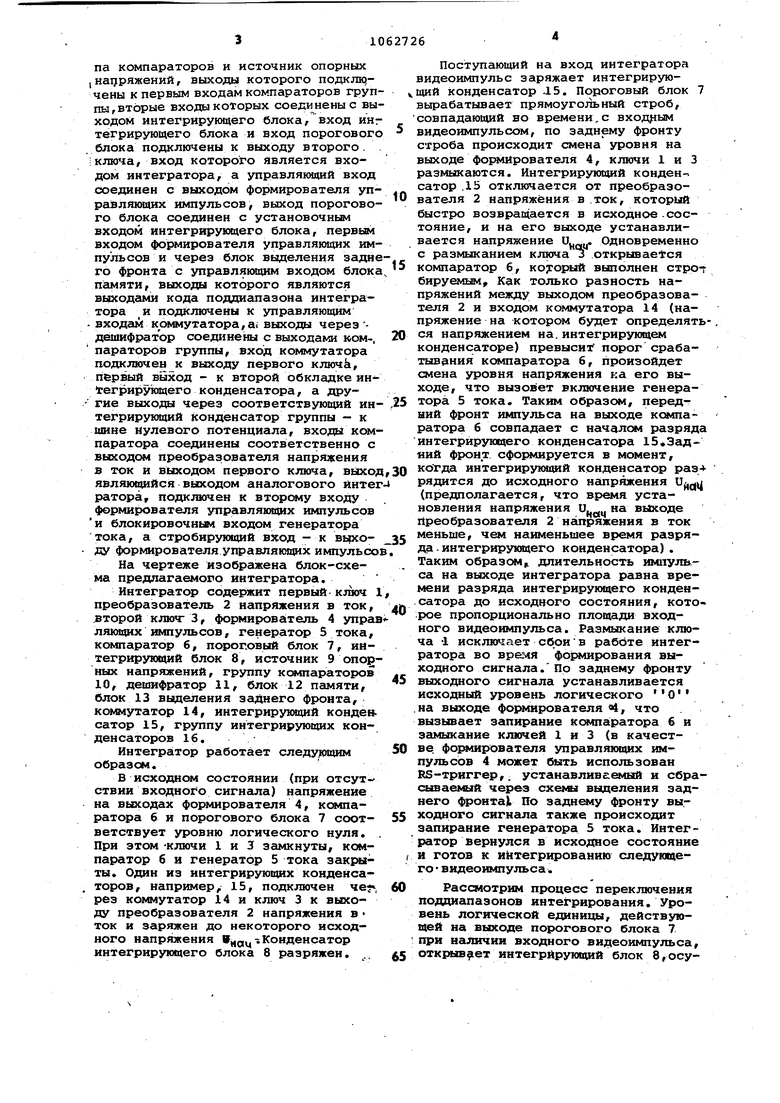

На чертеже изображена блок-схема предлагаемого интегратора.

Интегратор содержит первый кдпоч 1, преобразователь 2 напряжения в ток, л .второй ключ-3, формирователь 4 управ ляющих импульсов, генератор 5 тока, компаратор б, пороговый блок 7, интегрирующий блок 8, источник 9 опорных напряжений, группу компараторов . 10, деишфратор 11, блок 12 памяти, блок 13 выделения заднего фронта, кокмутатор 14, интегрирующий конден. сатор 15, группу интегрирующих конденсаторов 16,

Интегратор работает следу ощим 50 образом.

В исходном состоянии (при отсутствии входного сигнс1ла) напряжение на выходах формирователя 4, кошаратора б и порогового блока 7 соот- 55 ветствует уровню логического нуля. . При этом -ключи 1 и 3 замкнуты, компаратор б и генератор 5 тока закры- / ты. Один из интегрирующих конденсаторов, например/ 15, подключен чег, 60 рез коммутатор 14 и ключ 3 к выходу преобразователя 2 напряжения в ток и заряжен до некоторого исходного напряжения V,,-: Конденсатор интегрирующего блока 8 разряжен. .. 45

Поступающий на вход интегратора видеоимпульс заряжает интегрирующий конденсатор -15. Пороговый блок вырабатывает прямоугольный строб, совпадающий во времени,с входным видеоимпульсом, по заднему фронту строба происходит смена уровня на выходе фосФШрователя 4, ключи 1 и 3 размыкаются. Интегрирующий конденсатор .15 отключается от преобразователя 2 напряжения в .ток, который быстро возвращается в исходное .состояние, и на его выходе устанавливается напряжение ,,,. Одновременно с размыканием ключа 3 открываемся компаратор б, ко-сорый выполнен стро бируемым. Как только разность напряжений между выходом преобразователя 2 и входом коммутатора 14 (напряжение на котором будет определятся напряжением на.интегрирующем конденсаторе) превысит порог срабаТЫВ0НИЯ ксАотаратора б, произойдет смена уровня напряжения на его выходе, что вызоЕ)ет включение генератора 5 тока. Таким образом, передний фронт импульса на выходе кштаратора б совпадает с началом разряд интегрирукхцего конденсатора 15,ЭаД «ий фронт сформируется в момент, Kof да интегрируюишй конденсатор разрядится до исходного напряжения (предполагается, что время установления напряжения Оцац выходе преобразователя 2 напряжения в ток меньше, чем наименьшее время разряда .интегрирующего конденсатора). Таким образом длительность импульса на выходе интегратора равна времени разряда интегрирующего конден.сатора до исходного состояния, которое пропорционально площади входного видеоимпульса. Размыкание ключа исключает сбоиВ рабйте интегратора во формирования выходного сигнала.По заднему фронту выходного сигнала устанавливается исходный уровень логического О .на выходе формирователя 4, что вызывает запирание ксмпа:ратора 6 и замыкание ключей 1 и 3 (в качестве, формирователя управляющих импульсов 4 может быть использован RS-триггер,. устанавлив га4Ый и сбрасывае е2й через схеко выделения заднего фронтаЦ По фронту вы.ходного сигнала также происходит запирание генератора 5 тока. Интегратор вернулся в исходное состояние и готов к интегрированию следующего видеоимпульса.

Рассмотрим процесс переключения поддиапазонов интегрирования. Уровень логической единищ2, действующей на выходе порогового блока 7 при наличии входного видеоимпульса, интегрирующий блок 8,осуществляющий грубое, интегрирование, выходное напряжение этого блока U непрерьшно сравнивается с опорным напряжением компараторами 1 руппы котшараторов 10. Код, образующийся на выходах ксфшараторов, преобразуется в позиционный код дешифратором 11. Пусть ...Е и . Тогда на выходах компараторов . 10„ 1р.установится уровень логической единицы, а на остальных уровень логического нуля. При этом на i-M выходе дешифратора 11 должен установиться уровень логической единицы. Ояевидно, что выбор пр диапазона точного интегрирования можно осуществить лишь йосле .окончания выходного видеоимпульса. Соответственно, позиционный код с дешифратора 11 записывается в блок 12 памяти по имупльсу, вырабатываем му блоком 13 выделения заднего фрон та по заднему фронту порогового бло ка 7. На этом процесс формирования позиционного кода поддиапазона,заканчивается. Возврат порогового блока в исходное состояние вызывает принудительный разряд емкости интегрирующего блока 8, Очевидно, что переключение поддиапазонов будет происходить после значительного изменения параметров входных импульсов. До этого момента будет происходить лишьподтверждение кода, записанного в блок памяти. Таким образом, видеоимпульс, по которому происходит переключение под диапазона, интегрируется с ошибкой, последующие - с высокой точностью. Предлагаемый интегратор позволяет расширить динамический диапазон измеряемых сигналов и автоматизировать процесс измерений в тех случаях, требуется измерить суммарный интеграл длительной последовательности статистически распределенных импульсов с медленно менякжц «1ся параметрами или требуется измерить интеграл одного из серии импульсов. Дальнейшая цифровая обработка результатов измерений упрощается в виду того, что диапазон изменения длительности выходного сигнала интег ратора зависит от числа поддиапазо- нов интегрирования и может быть вы бран достаточно узким. Предлагаемый интегратор может алть использован в приборах ядерной техники (измерители интенсивности и дозы излучения ускорителей заряженных частиц), в магнитных измерениях {в индукционных датчиках, прич меняемнх при контроле технологичесл ких процессов).

| название | год | авторы | номер документа |

|---|---|---|---|

| Гибридное интегрирующее устройство | 1985 |

|

SU1316008A1 |

| Гибридное интегрирующее устройство | 1984 |

|

SU1168972A1 |

| Преобразователь среднего значения напряжения | 1982 |

|

SU1114964A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Аналоговый интегратор | 1983 |

|

SU1239730A1 |

| Цифровой измеритель добротности резонансных систем | 1983 |

|

SU1101757A1 |

| Преобразователь напряжения в частоту | 1988 |

|

SU1522407A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1989 |

|

SU1695503A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

ИНТЕГРАТОР, содержащий последовательно соединенные преобразователь напряжения в ток и первый ключ, между выходсм которого и шиной нулевого потенциала включен генератор тока, интегрируK№S)tu конденсатор, одна обмотка, ко торого соединена с шиной нулевого потенциала, формирователь управляющих импульсов, выход которого сое динен с управляющим входом первого ключа, отличающийся тем, что, с целью расширения динамического диапазона интегрируемых сигналов, в него введены кс таратор, второй ключ, пороговый блок, интегрирующий блок, коммутатор, группа интегрирующих конденсаторов, блок памяти, дешифратор, блок выделения заднего фронта, группа комр параторов и источник опорных напряжений, выходы которого подключены к первым входам компараторов группы, вторые входы которых соединены с выходом интегрирующего блока, .вход интегрирующего блока и вход iпорогового блока подключены к выхр ду второго ключа, вход которого является входом интегратора, а управляющий вход соединен с выходом формирователя управляющих-импульсов, выход порогового блока соединен с установочным входом интегрирующего блока, первым входом форми- рователя управляющих импульсов и через блок выделения заднего фронта с управляющим входом блока памяти, i выхода которого являются выходами кода поддиапазона интегратора и под«Л ключены к управляющим входам коммутатора, а выходы через дешифратор соединены с выходами компараторов группы,. вход ксяймутатора подключен к выходу первого ключа, первый выход - к второй обкладке интегрирующего конденсатора, а другие выходы через соответствующий интегрирукнций конденсатор группы - к шине нулевого потенциала, входы компара1чЭ .тора соединены соответственно с.выsJ ходом преобразователя напряжения в ток и выходом первого ключа, выход, to являющийся выходом аналогового интегО) ратора, подключен к второму входу фОЕ шрователя управляющих импульсов и блокировочньал входом генератора тока, а стробирующий вход - к выходу формирователя управляющих импульсов .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент Японии 8115027, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР , 148541,кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-23—Публикация

1982-07-28—Подача