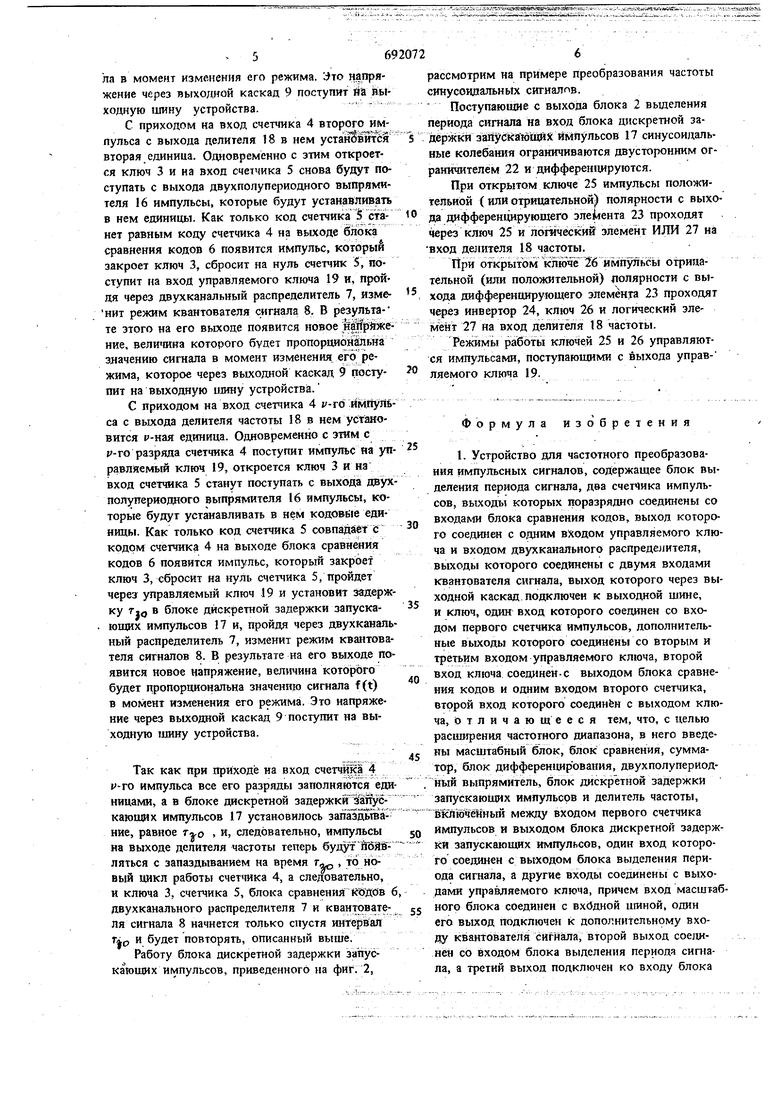

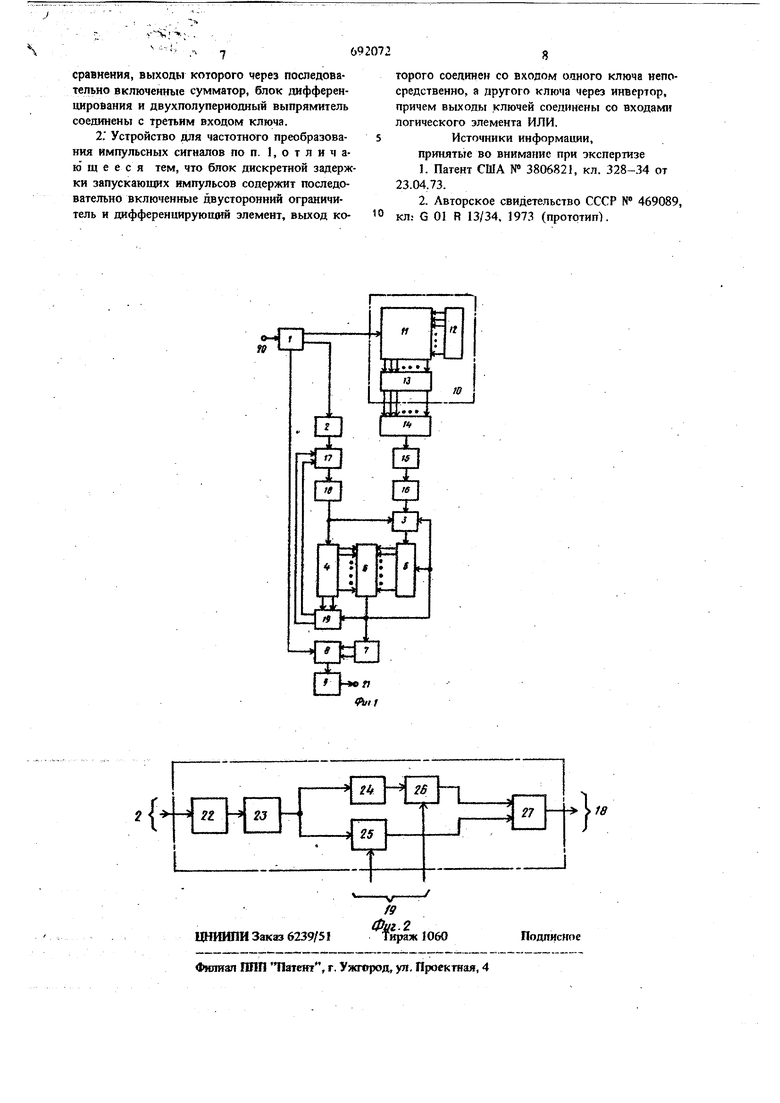

Изобретение относится к импульсной техяи ке. Известно устройство частотного преобразования сигналов, содержащее синхронизатор частоты, умножители частоты, реверсивный счетчик регулятор, сглаживающее устройство, синхронизатор линейного изменения, счетчик ступенчатого снижения, счетчик ступет атого повыйюнйя, схема сравнения, синхронизатор ухода ( Недостатком данного устройства являетсй его сложность.;г :::: : Наиболее близким по технической сущности к данному изобретению является устройство для частотного преобразования импульсных сигналов, содержащее блок выделения периода сигнала, даа счетчика импульсов, выходы которых поразрядно соединены со входами блока сравнения кодов, выход которого соединен с одним входом управляемого ключа и входом двухканального распределителя, выходы которого соедайены с двумя входами квантователя сигнала, вь1ход которого через выходной каскад подключен к выходной шине, и ключ, один вход соединен со §ходом первого счетчика импульсов. дополнительные выходы которого соединены сб вторым и третьим входом управляемого ключа, второй вход ключа соединен с выходом блока сравнения кодов и одним входом второго счетчика, второй вход которого соединен с выходом ключа 12. Недостатком данного устройства является недостаточный частотный диапазон. Цель изобретения - расширение частотного диапазона. Поставленная цель достигается тем, что в устройство частотного преоб{5азования сигналов, содержащее блок выделения сигнала, два счетчика Импульсов, выходы- которых поразрядно соединены со входами блока сравнения кодов, выход которого соединен с одним входом управляемого ключа и входом двухканального распределителя, выходы которого соединены с двумя входами квантователя сигнала, выход которого через выходной каскад подключен к выходной шине, и ключ, один вход которого соединен со входом первого счетчика йМпульсов, д6поШ1 ёльныё выходы которого соединены со вторым и третьим входом управляемого ключа, второй вход ключа соединен с выходом блока сравнения кодов и одним входом второго счетчика, второй вход которою соединен с выходом ключа, введены масштабный блок,блок сравнения, сумматор, блок дифферейцирования, двухполупериодный выпрямитель, блок дискретной задержки .запускающих импульсов и делитель частоты, включенный между входом первого счетчика импульсов и выходом блока дискретной задержки запускающих им- пульсов, один вход которого соединен с выходом блока 1ЩёМШ1Я ngpWo a ItpyrMfe вхьды соединены с выходами управляемого клю ча, причем вход масштабного блока соединен с входной шиной, один его выход подключен к дополйительному входу квантователя сигнала, вто|рой выход соединен со входом блока вьщеПений периода сигнала, а третий выход подключен ко входу блока сравнения, выходы которого адрез последовательно включенные сумматор, блок дифференцирования и двухполупериодный в шрямитель соединен с третьим входом ключа, кроме того, блок дискретной задержки запускаШ ук импульсов содержит последовательно вклю ченные двусторонний ограничитель и дифференциругоа ий элемййт, выход которого соединен со входом одаого ключа непосредственно, а другого через инвертйр, причем выходы ключей соединены со входами; логического элемента ИЛИ. Структурная электрическая схема описываемого устройства приведена на фит. }. На фиг. 2 приведена структурная схема 6JioKa дискретной задержки запускающих импульсов. Описываемое устройство содержит (фиг. 1) масштабный блок 1, блоквьщелешя периода сигнала 2, ключ 3, счетчики импульсов 4 и 5, блок сравнения кодов 6, двухканальный распределитель 7, квантователь сигнала 8, выходной каскад 9, блок сравнения 10, состоящий из вычитателя 11, ийочника эталонных напряжений 12 и блока пороговых элементов 13, сумматор 14, блок дифференцирования 15, двухполуперио ный выпрямитель 16, блок дискретной задержки запускающих импульсов 17, делитель частоты 18 управляемый ключ 19. Входной сигнал подай на входную шину 20. Выходной сигнал снимается с ишны 21. Блок дискретной задержки запускающих импульсов (фиг. 2) содержит двухсторонний ограничитель 22, дифференцирующий элемент 23, инвертор 24, ключи 25 и 26 и логический элемент ИЛИ 27. Принцип работы устройства заключается в следующем. Исходный сигнал f(t) через входную щину 20 и масщтабный блок 1 поступает на сигнальные входы блока сравнения 10, блока 2 выделения периода и квантователь сишала 8. Выходные напряжения источника эталонных напряжений 12 подведены к соответствующим входам вычислителя 11. При этом каждый выход вычитателя 11 соединён со входом соответствующего порогового элемента (на чертеже не показаны) блока пороговых элементов 13. При поступлении на вход блока сравнения 10 исходного сигнала в какие-то моменты вреМёни на выходах соответствующих пороговых элементов блока пороговых элементов 13 появ ляются перепады напряжений, которые после суммирования в сумматоре 14, дифференцирования и двухполупериодного выпрямления поступают в виде импульсов на вход ключа 3. Со второго выхода масштабного блока 1 исходный сигнал через блок 1 выделения периода сигнала, блок дискретной задержки запускаюших импульсов 17 и делитель частоты 18 поступает в виде импульсов на вход счетчика импульсов 4 и второй вход ключа 3. С третьего выхода масштабного блока 1 сигнал f (t) noctynaeT непосредственно на третий вход квантователя сигнала 8. Время задержки т в блоке дискретной задержки запускающих импульсов 17 изменяется с течением времени по закону , С-- тде Гуд - приращение задержки, определяемое из равенства о - ЙГГГ Интервал повторения Т исходного сигнала f(t) И интервал повторения То преобразованного сигнала f (t) связаны выражением То (NTVI + 1) Т. где М - коэффициент деления частоты делителя частоты 18; N - число отсчетов на интервале повторения Т.. Будем считать, что счетчики 4 и 5 находятся в нулевых положениях. Тогда с приходом на вхОд счетчика 4 первого импульса с выхода делителя частоты 18 в нем установится единица. Одновременно с этим откроется ключ 3 и разрешит прохождение импульсов с выхода двухполупериодного выпрямителя 16 на вход счетчика 5. При поступлении на вход счетчика 5 первого импульса в нем установится единица. Вследствие равенства кодов счетчика 4 и счегшка 5 на выходе блока сравнения кодов 6 появится импульс, который закроет ключ 3, сбросит На нуль счетчик 5, поступит на вход управляемого ключа 19 и, пройдя через двухканалъный распределитель 7, изменит режим квантователя сигнала 8. В результате этого на его выходе появится напряжение, величина которо,го пропорциональна значению исходного сигна56ла в момент изменения его режима. Уто щпряжение через выходной каскад 9 поступит йа ЙЫходаую цшну устройства. С приходом на вход счетчика 4 второго импульса с выхода делителя 18 в нем установйт1&я вторая единица. Одновременно с этим откроется ключ 3 и на вход счетчика 5 снова будут поступать с выхода двухполупериодного выпрямителя 16 импульсы, которые будут устанавливать в нем единицы. Как только код счетчика § станет равным коду счетчика 4 на выходе блока сравнения кодов 6 появится импульс, который закроет ключ 3, сбросит на нуль счетчик 5, поступит на вход управляемого ключа 19 и, пройдя через двухканальный распределитель 7, изменит режим квантователя сигнала 8. В резупьтате этого на его выходе появится новое нйрйжение, величина которого будет пропорциоййлша значению сигнала в момент изменения его режима, которое через выходной каскад 9 поступит на выходную ujHHy устройства. С приходом на вход счетчика 4 1-го импульса с выхода делителя частоты 18 в нем установится р-ная единица. Одновременно с этим с -го разряда счетчика 4 поступит импульс на управляемый ключ 19, откроется ключ 3 и на вход счетчика 5 станут поступать с выхода двух полупериодного выпрямителя 16 импульсы, которые будут устанавливать в нем кодовй1е единицы. Как только код счетчика 5 совпадает с кодом счетчика 4 на выходе блока сравнения кодов 6 появится импульс, который закроет ключ 3, сбросит на нуль счетчика 5, пройдет через управляемый ключ 19 и установит задержку TJQ в блоке дискретной задержки запускающих импульсов 17 и, пройдя через двухканальный распределитель 7, изменит режим квантователя сигналов 8, В результате на его выходе появится новое напряжение, величина которого будет пропорциональна значению сигнала f(t) в момент изменения его режима. Это напряжение через выходной каскад 9 поступит на выходную цшну устройства. Так как при приходе на вход счетчика 4 f-ro импульса все его разряды заполняются единицами, а в блоке дискретной задержкй запускающих импульсов 17 установилось запаэдавание, равное То-о , и, следовательно, импульсы на выходе делителя частоты теперь будУт пой§пяться с запаздыванием на время г, , то новый цикл работы счетчика 4, а следовательно, к ключа 3, счетчика 5, блока сравнения КЪдов 6 двухканалъного распределителя 7 и квантрвателя сигнала 8 начнется только спустя иитервал rip и будет повторять, описанный выше. Работу блока дискретной задержки запускающих импульсов, приведенного на фиг. 2, рассмотрим на примере преобразования частоты синусоидальных сигналпв. Поступающие с выхода блока 2 вьщеления периода сигнала на вход блока дискретной задержки зайускающйХ импульсов 17 синусоидальные колебания ограничиваются двусторонним ограничителем 22 и дифферешшруются. При открытом ключе 25 импульсы положительной (или отрицательной) полярности с выхода дифференцирующего элейента 23 проходят через ключ 25 и логический элемент ИЛИ 27 на вход делителя 18 частоты. При от крытом к:лючё 26 импульсъ отрицательной (или положительной) полярности с выхода дифференцирующего элемента 23 проходят через инвертор 24, ключ 26 и логический элемент 27 на вход делителя 18 частоты. Режимы работы ключей 25 и 26 управляются импульсами, поступающими с выхода управляемого ключа 19. Формула изобретения 1. Устройство для частотного преобразования импульсных сигналов, содержащее блок выделения периода сигнала, два счетчика импульсов, выходы которых поразрядао соединены со входами блока сравнения кодов, выход которого соединен с одним входом управляемого ключа и входом двухканального распределителя, выходы которого соединены с двумя входами квантователя сигнала, выход которого через выходной каскад подключен к выходной шине, и ключ, один вход которого соединен со входом первого счетчика импульсов, дополнительные выходы которого соединены со вторым и третьим входом управляемого ключа, второй вход ключа соединен-с выходом блока сравнения кодов и одним входом второго счетчика, второй вход которого соединён с выходом ключа. Отличающееся тем, что, с целью расширения частотного диапазона, в него введены масштабный блок, блок сравнения, сумматор, блок дифферен 1ИрЪвания, двухполупериодный выпрямитель, блок дискретной задержки запускающих импульсов и делитель частоты, включённый между входом первого счетчика импульсов и выходом блока дискретной задержки запускающих импульсов, один вход которого соединен с выходом блока выделения периода сигнала, а другие входы соединены с выходами управляемого ключа, причем вход масштабного блока соединен с вхбдной шиной, один его выход подключен к дополнительному входу квантователя ёИгнала, второй выход соединён со входом блока выделения периода сигаала, а третий выход подключен ко входу блока

сравнения, выходы которого через последовательно включенные сумматор, блок дифференцирования и двухполупериодный выпрямитель соединены с третьим входом ключа.

2. Устройство для частотного преобразования импульсных сигналов по п. 1, о т л и ч аю щ е е с я тем, что блок дискретной задержки запускающих импульсов содержит последовательно включенные двусторонний ограничитель и дифференцирующий элемент, выход которого соединен со входом одного ключа непосредственно, а 71ругого ключа через инвертор, причем выходы ключей соединены со входами логического элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Патент США N 3806821, кл. 328-34 от 23.04.73.

2.Авторское свидетельство СССР N 469089, кл.- G 01 R 13/34, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления непосредственным преобразователем частоты | 1985 |

|

SU1265944A1 |

| Двухканальный сверхвысокочастотный коррелометр | 1983 |

|

SU1124327A1 |

| Преобразователь постоянного напряжения в переменное программируемой формы с блоком управления | 1982 |

|

SU1019566A1 |

| Преобразователь постоянного напряжения в переменное программируемой формы | 1981 |

|

SU972650A1 |

| МОДУЛЯТОР ДИСКРЕТНОГО СИГНАЛА ПО ВРЕМЕННОМУ ПОЛОЖЕНИЮ | 2008 |

|

RU2393640C1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| ЦИФРОВОЙ АНАЛИЗАТОР ЧАСТОТНЫХ ХАРАКТЕРИСТИК ЛИНЕЙНОГО ЧЕТЫРЕХПОЛЮСНИКА | 1968 |

|

SU221785A1 |

| Адаптивный статический анализатор | 1985 |

|

SU1305730A1 |

| Вычислительное устройство для первичной обработки информации | 1978 |

|

SU746605A1 |

| АНАЛИЗАТОР РАБОТЫ СИСТЕМ ДВИГАТЕЛЯ ВНУТРЕННЕГО СГОРАНИЯ | 2011 |

|

RU2532990C2 |

Л Л//7

г)

18

Авторы

Даты

1979-10-15—Публикация

1977-07-25—Подача