Изобретение относится к автоматике и вычислительной технике и может быть использовано при исследовании процессов различной физической природы, которые описываются экспоненциальной функцией.

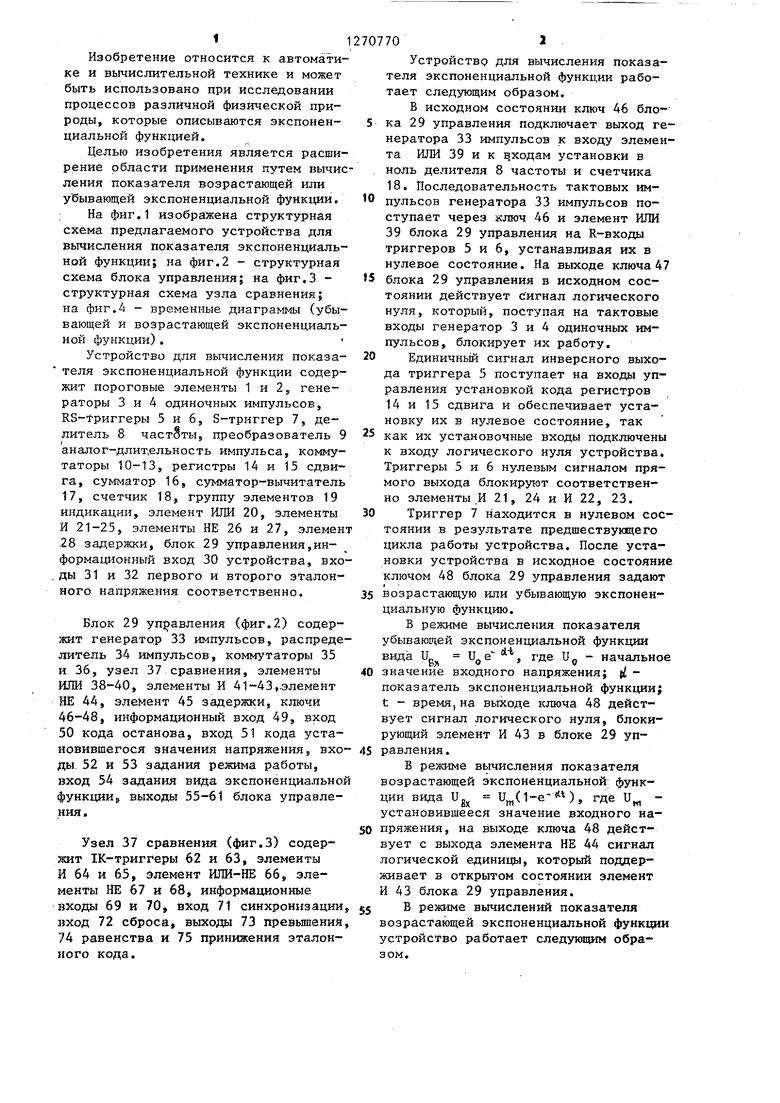

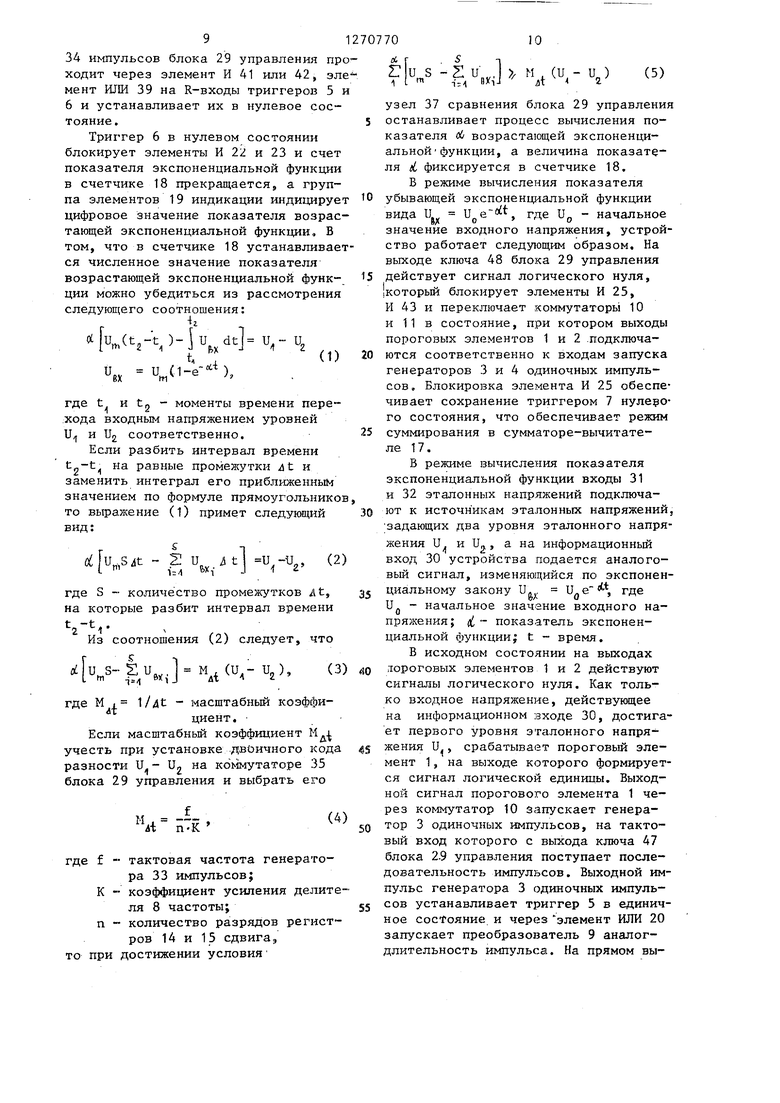

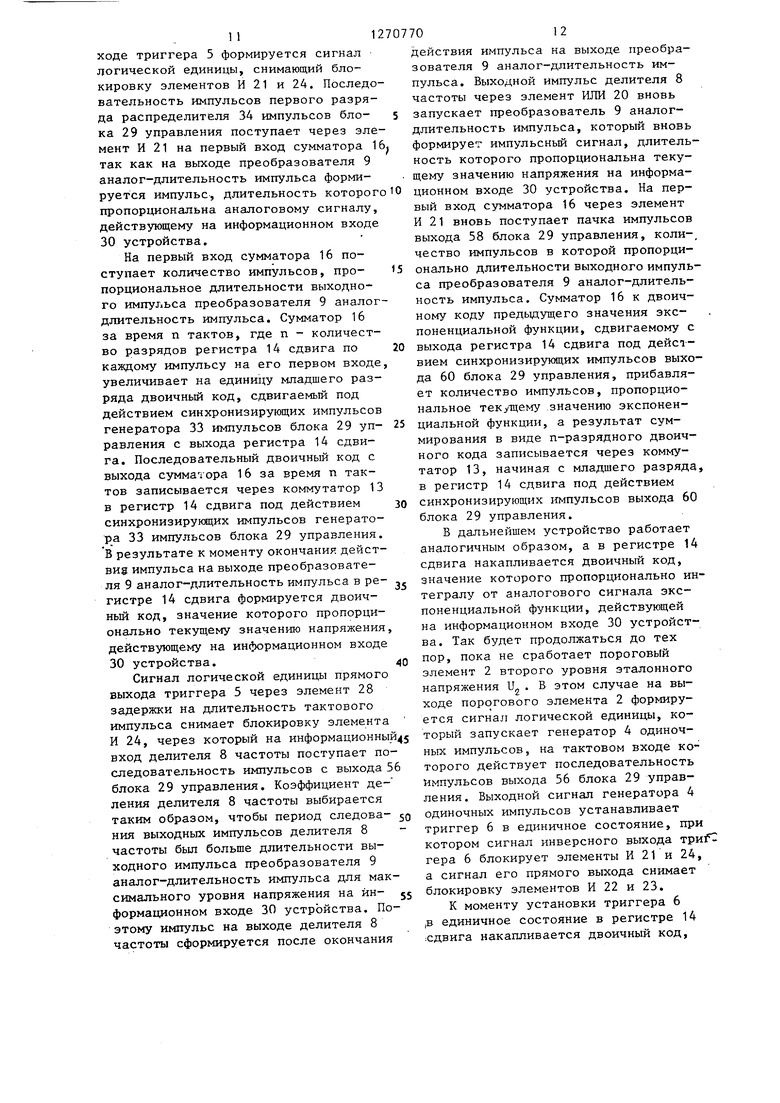

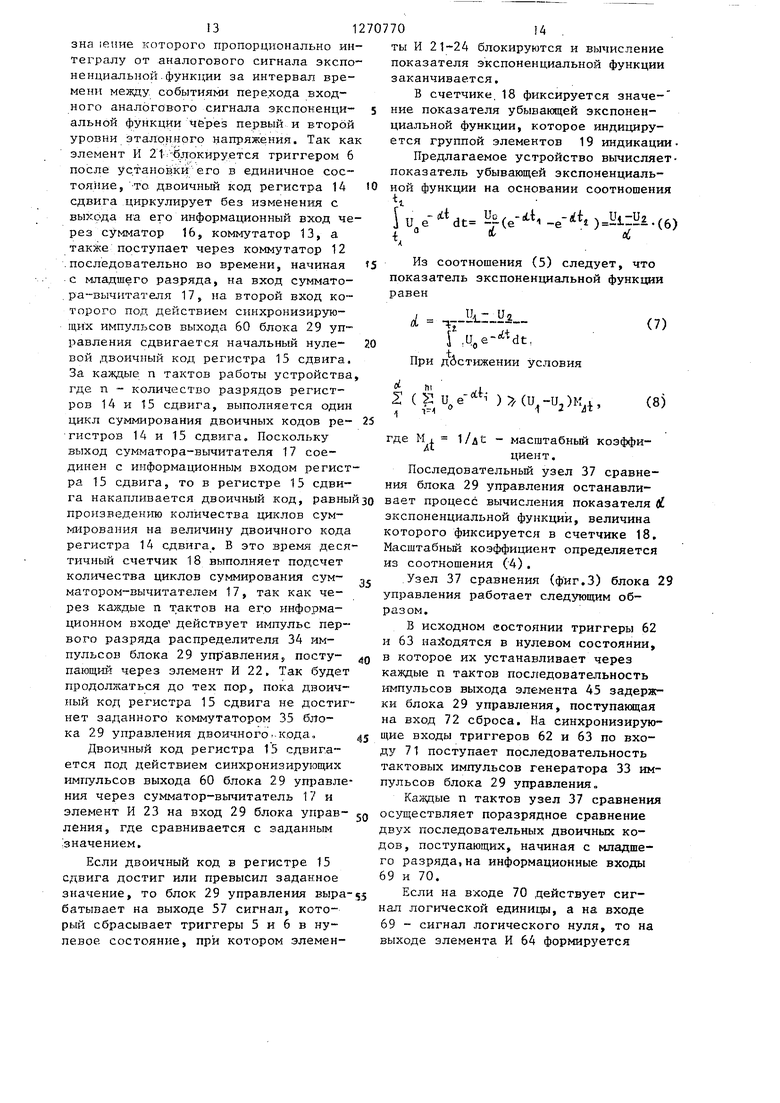

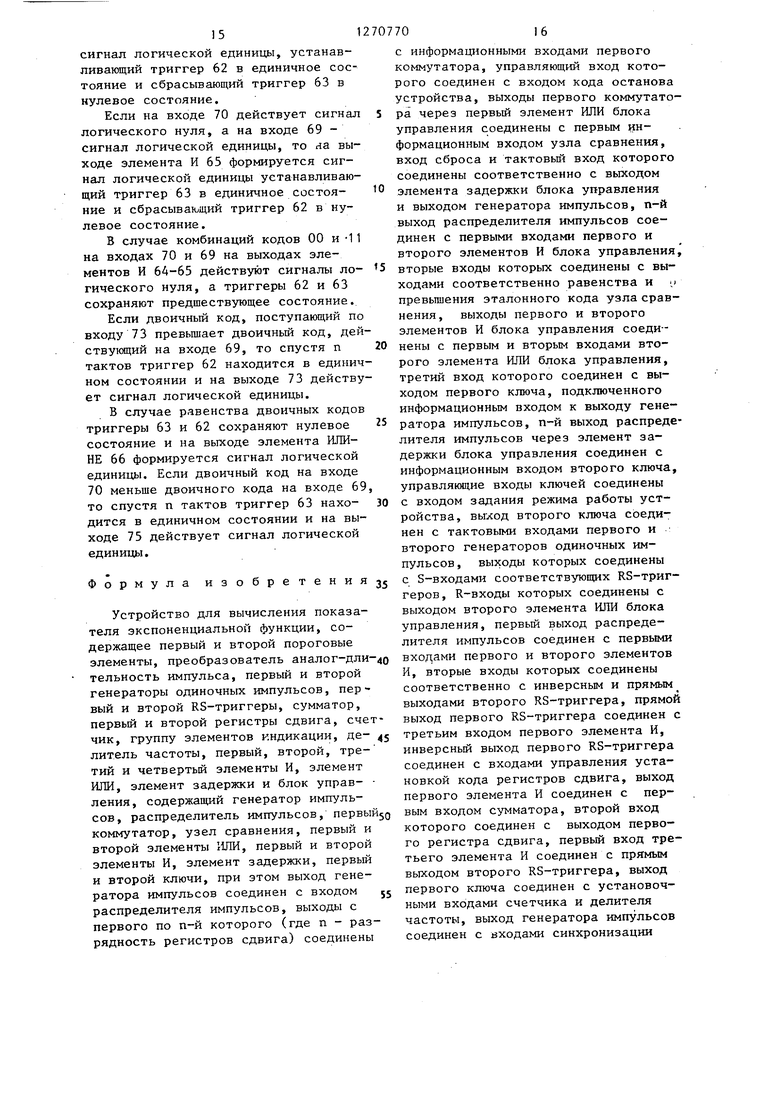

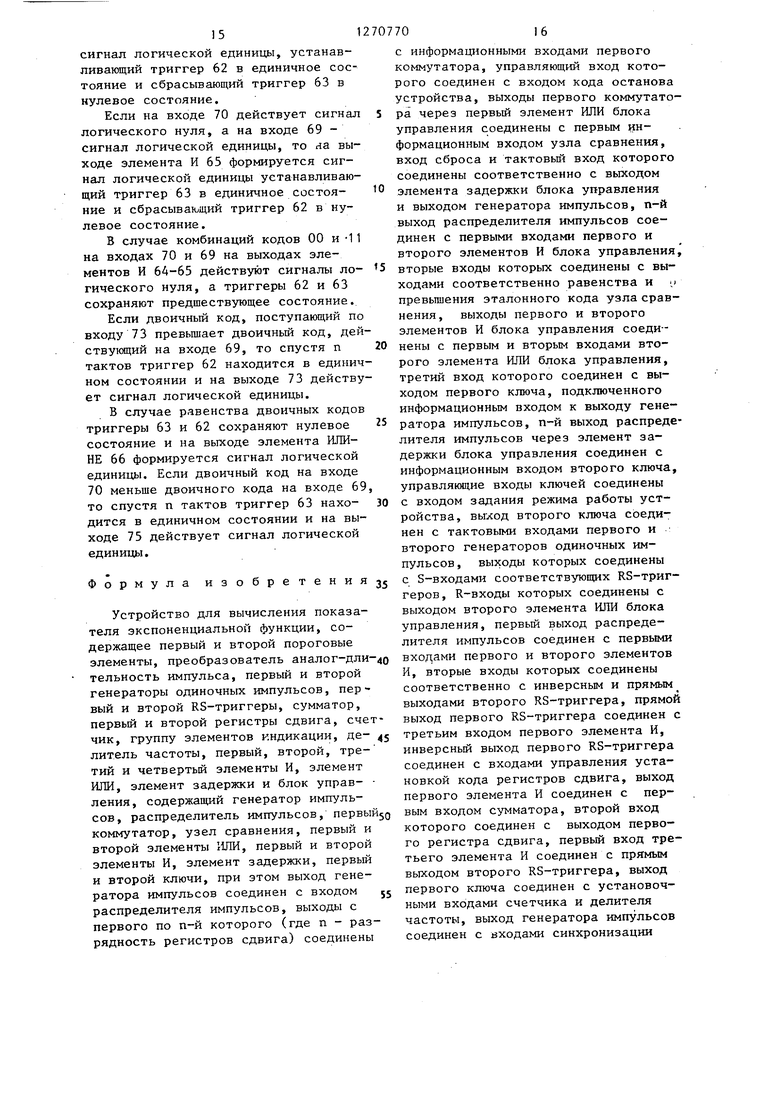

Целью изобретения является расширение области применения путем вычисления показателя возрастающей или убывающей экспоненциальной функции. На фиг.1 изображена структурная схема предлагаемого устройства для вычисления показателя экспоненциальной функции; на фиг.2 - структурная схема блока управления; на фиг.З структурная схема узла сравнения; на фиг.4 - временные диаграммы (убывающей и возрастающей экспоненциальной функции). Устройство для вычисления показателя экспоненциальной функции содержит Пороговые элементы 1 и 2, генераторы 3 и 4 одиночных импульсов, RS-Триггеры 5 и 6, S-триггер 7, делитель 8 частоты, преобразователь 9 аналог-длит,ельность импульса, коммутаторы 10-13, регистры 14 и 15 сдвига, сумматор 16, сумматор-вычитатель 17, счетчик 18, группу элементов 19 индикации, элемент ИЛИ 20, элементы И 21-25, элементы НЕ 26 и 27, элемент 28 задержки, блок 29 управления,информационный вход 30 устройства, входы 31 и 32 первого и второго эталонного напряжения соответственно.

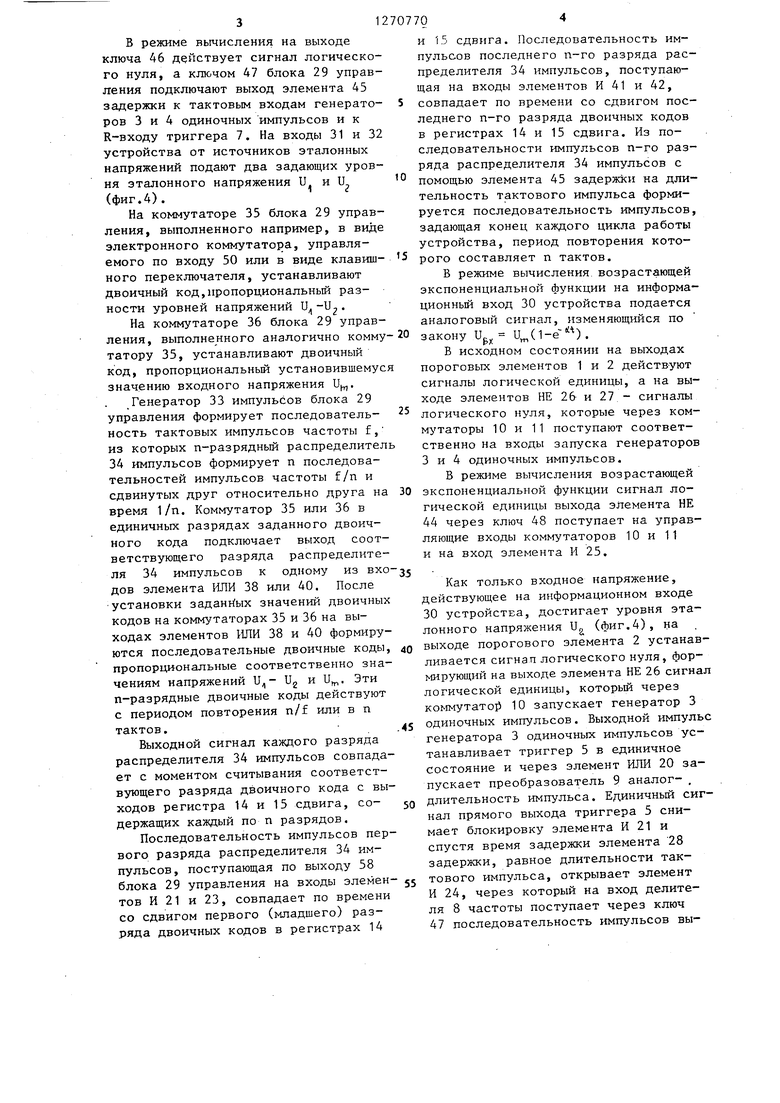

Блок 29 уп равления (фиг.2) содержит генератор 33 импульсов, распредеитель 34 импульсов, коммутаторы 35 и 36, узел 37 сравнения, элементы ИЛИ 38-40, элементы И 41-43,,элемент НЕ 44, элемент 45 задержки, ключи 46-48, информационный вход 49, вход 50 кода останова, вход 51 кода установившегося значения напряжения, вхоы 52 и 53 задания режима работы, вход 54 задания вида экспоненциальной ункции,, выходы 55-61 блока управления.

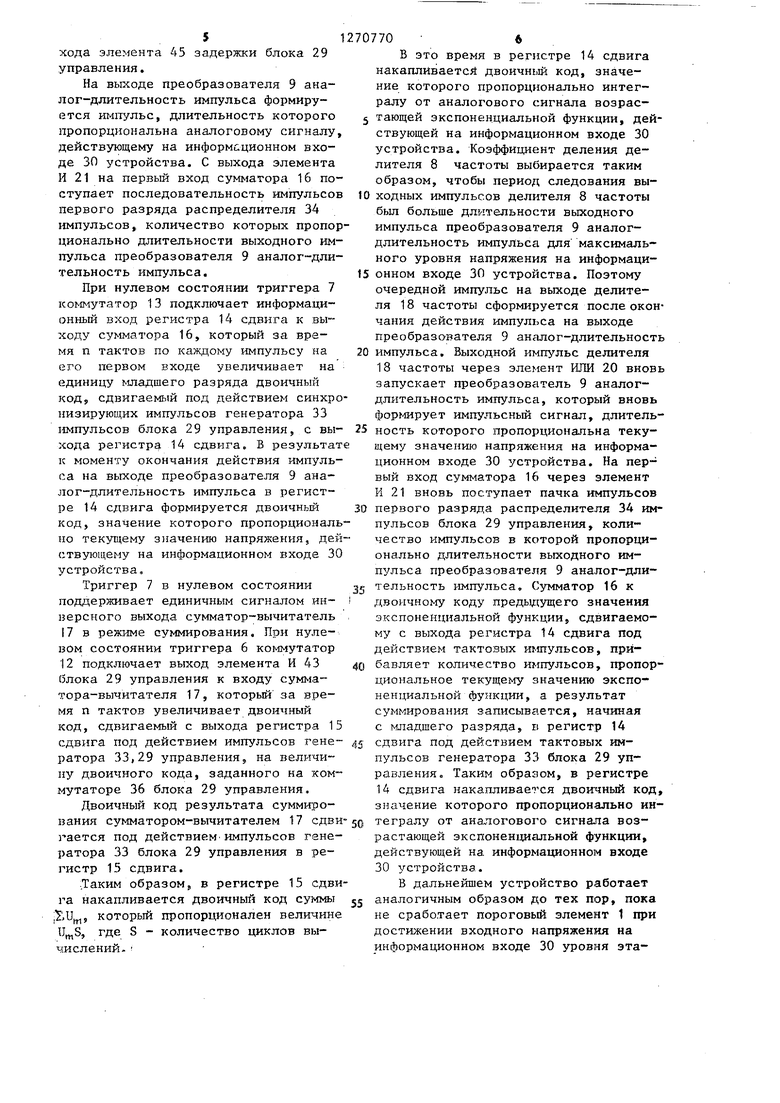

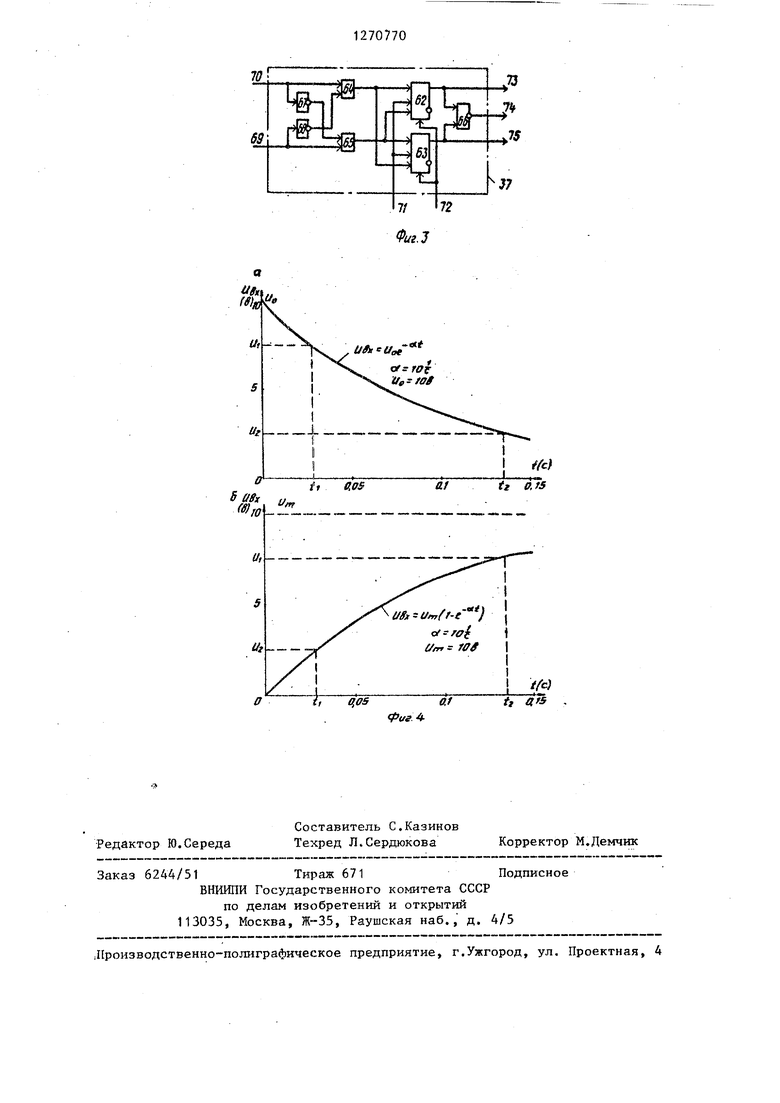

Узел 37 сравнения (фиг.З) содержит 1К-триггеры 62 и 63, элементы И 64 и 65, элемент ИЛИ-НЕ 66, элементы НЕ 67 и 68, информационные входы 69 и 70, вход 71 синхронизации, вход 72 сброса, выходы 73 превьшения, 74 равенства и 75 принижения эталонного кода.

Устройство для вычисления показателя экспоненциальной функции работает следующим образом.

В исходном состоянии ключ 46 блока 29 управления подключает выход генератора 33 импульсов к входу элемента ШШ 39 и к входам установки в ноль делителя 8 частоты и счетчика 18. Последовательность тактовых импульсов генератора 33 импульсов поступает через ключ 46 и элемент ИЛИ 39 блока 29 управления на R-входы триггеров 5 и 6, устанавливая их в нулевое состояние. На выходе ключа 47

блока 29 управления в исходном состоянии действует сигнал логического нуля, который, поступая на тактовые входы генератор 3 и 4 одиночных импульсов, блокирует их работу.

Единичньш сигнал инверсного выхода триггера 5 поступает на входы управления установкой кода регистров 14 и 15 сдвига и обеспечивает установку их в нулевое состояние, так

как их установочные входы подключены

к входу логического нуля устройства. Триггеры 5 и 6 нулевым сигналом прямого выхода блокируют соответственно элементы .И 21, 24 и И 22, 23.

Триггер 7 находится в нулевом состоянии в результате предшествующего цикла работы устройства. После уста новки устройства в исходное состояние ключом 48 блока 29 управления задают

возрастающую или убывающую экспоненциальную функцию.

В режиме вычисления показателя убывающей экспоненциальной функции вида у„ еГ , где U , - начальное

значение входного напряжения; Ц показатель экспоненциальной функции; t - время, на выходе ключа 48 действует сигнал логического нуля, блокирующий элемент И 43 в блоке 29 управления.

В режиме вычисления показателя возрастающей экспоненциальной; функции вида Ugj и(1-е-), где U установившееся значение входного на-

ряжения, на выходе ключа 48 действует с выхода элемента НЕ 44 сигнал логической единицы, который поддеривает в открытом состоянии элемент И 43 блока 29 управления.

В режиме вычислений показателя озрастающей экспоненциальной функции стройство работает следующим образом.

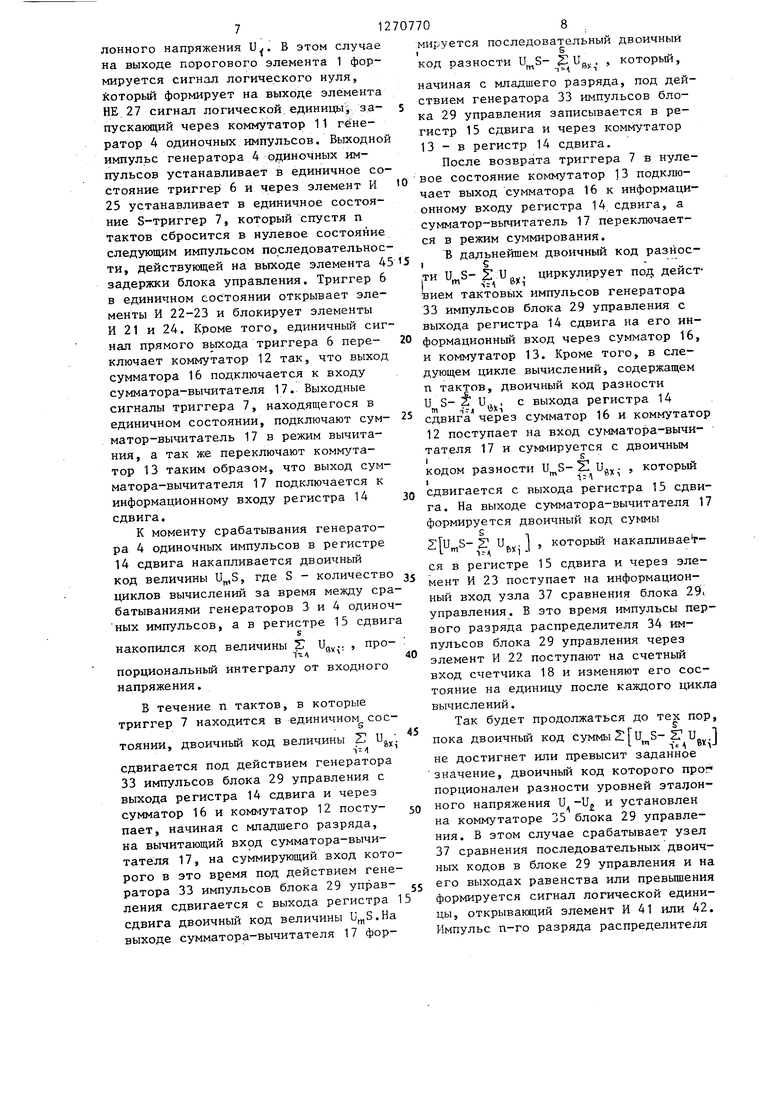

В режиме вычисления на выходе ключа 46 действует сигнал логического нуля, а ключом 47 блока 29 управления подключают выход элемента 45 задержки к тактовым входам генераторов 3 и 4 одиночных импульсов и к R-входу триггера 7. На входы 31 и 32 устройства от источников эталонных напряжений подают два задающих уровня эталонного напряжения U и U (фиг.4).

На коммутаторе 35 блока 29 управления, выполненного например, в виде электронного коммутатора, управляемого по входу 50 или в виде клавишкого переключателя, устанавливают двоичный код,пропорциональный разности уровней напряжений .

На коммутаторе 36 блока 29 управления, выполненного аналогично комму татору 35, устанавливают двоичный код, пропорциональный установившемус значению входного напряжения U.

Генератор 33 импульсов блока 29 управления формирует последовательность тактовых импульсов частоты f, из которых п-разрядный распределител 34 импульсов формирует п последовательностей импульсов частоты f/n и сдвинутых друг относительно друга на время 1/п. Коммутатор 35 или 36 в единичных разрядах заданного двоичного кода подключает выход соответствующего разряда распределителя 34 импульсов к одному из вхо ДОН элемента ИЛИ 38 или 40. После установки заданных значений двоичных кодов на коммутаторах 35 и 36 на выходах элементов ИЛИ 38 и 40 формируются последовательные двоичные коды, пропорциональные соответственно значениям напряжений U,- Ug и U. Эти п-разрядные двоичные коды действуют с периодом повторения n/f или в п тактов.

Выходной сигнал каждого разряда распределителя 34 импульсов совпадает с моментом считывания соответствующего разряда двоичного кода с выходов регистра 14 и 15 сдвига, содержащих каждый по п разрядов.

Последовательность импульсов первого разряда распределителя 34 импульсов, поступающая по выходу 58 блока 29 управления на входы элементон И 21 и 23, совпадает по времени со сдвигом первого (младшего) разряда двоичных кодов в регистрах 14

и 15 сдвига. Последовательность импульсов последнего п-го разряда распределителя 34 импульсов, поступающая на входы элементов И 41 и 42, совпадает по времени со сдвигом последнего п-го разряда двоичных кодов в регистрах 14 и 15 сдвига. Из последовательности импульсов п-го разряда распределителя 34 импульсов с помощью элемента 45 задержки на длительность тактового импульса формируется последовательность импульсов задающая конец каждого цикла работы устройства, период повторения которого составляет п тактов.

В режиме вычисления возрастающей экспоненциальной функции на информационньй вход 30 устройства подается аналоговый сигнал, изменяющийся по закону и. ).

рл

В исходном состоянии на выходах пороговых элементов 1 и 2 действуют сигналы логической единицы, а на выходе элементов НЕ 26 и 27 - сигналы логического нуля, которые через коммутаторы 10 и 11 поступают соответственно на входы запуска генераторов 3 и 4 одиночных импульсов.

В режиме вычисления возрастающей экспоненциальной функции сигнал логической единицы выхода элемента НЕ 44 через ключ 48 поступает на управляющие входы коммутаторов 10 и 11 и на вход элемента И 25.

Как только входное напряжение, действующее на информационном входе 30 устройства, достигает уровня эталонного напряжения , (фиг.4), на выходе порогового элемента 2 устанавливается сигнал логического нуля, формирующий на выходе элемента НЕ 26 сигна логической единицы, который через коммутатор 10 запускает генератор 3 одиночных импульсов. Выходной импуль генератора 3 одиночных импульсов устанавливает триггер 5 в единичное состояние и через элемент ИЛИ 20 запускает преобразователь 9 аналог- . длительность импульса. Единичный сигнал прямого выхода триггера 5 снимает блокировку элемента И 21 и спустя время задержки элемента 28 задержки, равное длительности тактового импульса, открывает элемент И 24, через который на вход делителя 8 частоты поступает через ключ 47 последовательность импульсов выхода элемента 45 задержки блока 29 управления. На выходе преобразователя 9 аналог-длительность импульса формируется импульс, длительность которого пропорциональна аналоговому сигналу, действующему на информационном входе ЗП устройства. С выхода элемента И 21 на первый вход сумматора 16 поступает последовательность импульсов первого разряда распределителя 34 импульсов, количество которых пропор ционально длительности выходного импульса преобразователя 9 аналог-длительность импульса. При нулевом состоянии триггера 7 коммутатор 13 подключает информационный вход регистра 14 сдвига к выходу сумматора 16, который за время п тактов по каждому импульсу на его первом входе увеличивает на единицу младшего разряда двоичный код, сдвигаемый под действием синхро низирующих импульсов генератора 33 импульсов блока 29 управления, с выхода регистра 14 сдвига. В результат к моменту окончания действия импульса на выходе преобразователя 9 аналог-длительность импульса в регистре 14 сдвига формируется двоичный код, значение которого пропорциональ но текущему значению напряжения, дей ствующему на информационном входе 30 устройства. Триггер 7 в нулевом состоянии поддерживает единичным сигналом инверсного выхода сумматор-вычитатель 17 в режиме суммирования. При нулевом состоянии триггера 6 коммутатор 12 подключает выход элемента И 43 блока 29 управления к входу сумматора-вычитателя 17, который за время п тактов увеличивает двоичный код, сдвигаемый с выхода регистра 15 сдвига под действием импульсов гене ратора 33,29 управления, на величину двоичного кода, заданного на ком мутаторе 36 блока 29 управления. Двоичный код результата сумм1-грования сумматором-вычитателем 17 сдвнгается под действиемимпульсов генератора 33 блока 29 управления в регистр 15 сдвига. Таким образом, в регистре 15 сдвига накапливается двоичный код ., который пропорционален величине , где S - количество циклов вычислений. 0770 6 В это время в регистре 14 сдвига накапливается двоичный код, значение которого пропорционально интегралу от аналогового сигнала возрас- 5 тающей экспоненциальной функции, действующей на информационном входе 30 устройства. Коэффициент деления делителя 8 частоты выбирается таким образом, чтобы период следования выходных импульсов делителя 8 частоты был больше длительности выходного импульса преобразователя 9 аналогдлительность импульса для максимального уровня напряжения на информационном входе 30 устройства. Поэтому очередной импульс на выходе делителя 18 частоты сформируется после окончания действия импульса на выходе преобразователя 9 аналог-длительность импульса. Выходной имщльс делителя 18 частоты через элемент ИЛИ 20 вновь запускает преобразователь 9 аналогдлительность импульса, который вновь формирует импульсный сигнал, длительность которого пропорциональна текущему значению напряжения на информационном входе 30 устройства. На первый вход сумматора 16 через элемент И 21 вновь поступает пачка импульсов первого разряда распределителя 34 импульсов блока 29 управления, количество импульсов в которой пропорционально длительности выходного импульса преобразователя 9 аналог-дли- тельность импульса. Сумматор 16 к двоичному коду предыдущего значения экспоненциальной функции, сдвигаемому с выхода регистра 14 сдвига под действием тактовых импульсов, прибавляет количество импульсов, пропорциональное текущему значению экспо ненциальной функции, а результат суммирования записывается, начиная с младшего разряда, в регистр 14 сдвига под действием тактовых импульсов генератора 33 блока 29 управления. Таким образом, в регистре 14 сдвига накаш1ивае7ся двоичный код, значение которого пропорционально инjoтегралу от аналогового сигнала возрастающей экспоненциальной функции, действующей на. информационном входе 30 устройства. В дальнейшем устройство работает jjаналогичным образом до тех пор, пока не сработает пороговый элемент 1 при достижении входного напряжения на информационном входе 30 уровня эталонного напряжения U. В этом случае на выходе порогового элемента 1 формируется сигнал логического нуля, который формирует на выходе элемента НЕ 27 сигнал логической.единицы запускающий через коммутатор 11 генератор 4 одиночных импульсов. Выходно импульс генератора 4 одиночных импульсов устанавливает в единичное со стояние триггер 6 и через элемент И 25 устанавливает в единичное состояние S-триггер 7, который спустя п тактов сбросится в нулевое состояние следующим импульсом последовательнос ти, действукяцей на выходе элемента 4 задержки блока управления. Триггер 6 в единичном состоянии открывает элементы И 22-23 и блокирует элементы И 21 и 24. Кроме того, единичный сиг нал прямого вьгхода триггера 6 переключает коммутатор 12 так, что выход сумматора 16 подключается к входу сумматора-вычитателя 17 Выходные сигналы триггера 7, находящегося в единичном состоянии, подключают сумматор-вычитатель 17 в режим вычитания, а так же переключают коммутатор 13 таким образом, что выход сумматора-вычитателя 17 подключается к информационному входу регистра 14 сдвига. К моменту срабатывания генератора 4 одиночных импульсов в регистре 14 сдвига накапливается двоичный код величины , где S - количество циклов вычислений за время между сра батываниями генераторов 3 и 4 одиноч ных импульсов, а в регистре 15 сдвиг накопился код величины S и„.,.. , про1 Лпорциональный интегралу от входного напряжения. В течение п тактов, в которые триггер 7 находится в единичном состоянии, двоичный код величины S U. сдвигается под действием генератора 33 импульсов блока 29 управления с выхода регистра 14 сдвига и через сумматор 16 и коммутатор 12 поступает, начиная с младшего разряда, на вычитающий вход сумматора-вычитателя 17, на суммирующий вход которого в это время под действием генератора 33 импульсов блока 29 управления сдвигается с выхода регистра сдвига двоичный код величины .Ha выходе сумматора-вычитателя 17 фор1 1 мируется последовательный двоичный 1s код разности 2 U. , который, начиная с младшего разряда, под действием генератора 33 импульсов блока 29 управления записывается в регистр 15 сдвига и через коммутатор 13 - в регистр 14 сдвига. После возврата триггера 7 в нулевое состояние коммутатор 13 подключает выход сумматора 16 к информационному входу регистра 14 сдвига, а сумматор-вычитатель 17 переключается в режим суммирования. В дальнейшем двоичный код разнос1 S, ти 2 и„„. циркулирует под деистm .д В)(, вием тактовых импульсов генератора 33 импульсов блока 29 управления с выхода регистра 14 сдвига на его информационный вход через сумматор 16, и коммутатор 13. Кроме того, в следующем цикле вычислений, содержащем п тактов, двоичный код разности и S- Z и,,,. с выхода регистра 14 m ч-д Wi сдвига через сумматор 16 и коммутатор 12 поступает на вход сумматора-вычитателя 17 и суммируется с двоичным Is кодом разности U. , который сдвигается с выхода регистра 15 сдвига. На выходе сумматора-вычитателя 17 формируется двоичный код суммы s 2 V. I , который накапливаегся в регистре 15 сдвига и через элемент И 23 поступает на информационный вход узла 37 сравнения блока 2911 управления. В это время импульсы первого разряда распределителя 34 импульсов блока 29 управления через элемент И 22 поступают на счетный вход счетчика 18 и изменяют его состояние на единицу после каждого цикла вычислений. Так будет продолжаться до тех пор, пока двоичный код суммы S- 2Г U 1 L Ir Д не достигнет или превысит заданное значение, двоичный код которого прог порционален разности уровней эталонного напряжения U -U и установлен на коммутаторе 35 блока 29 управления. В этом случае срабатывает узел 37 сравнения последовательных двоичных кодов в блоке 29 управления и на его выходах равенства или превьшения формируется сигнал логической единицы, открывающий элемент И 41 или 42. Импульс п-го разряда распределителя 9 34 импульсов блока 29 управленю пр ходит через элемент И 41 или 42, эл мент ШШ 39 на R-входы триггеров 5 6 и устанавливает их в нулевое состояние. Триггер 6 в нулевом состоянии блокирует элементы И 2k и 23 и счет показателя экспоненциальной функции в счетчике 18 прекращается, а группа элементов 19 индикации индшшруе цифровое значение показателя возрас тающей экспоненциальной функции,, В том, что в счетчике 18 устанавливае ся численное значение показателя возрастающей экспоненциальной функции можно убедиться из рассмотрения следуюн(его соотношения: K/t,-t) , (1) , и,1-;-ъ. где t и tg - моменты времени перехода входным напряжением уровней U;, и Ug соответственно. Если разбить интервал времени t -t на равные промежутки At н заменить интеграл его приближенным значением по формуле прямоугольнико то вьфажение (1) примет следующий вид: ,, I U., (2 где S - количество промежутков At, на которые разбит интервал времени соотношения (2) следует, что 4v-|.. з где М , 1/лС - масштабный коэффициент. Если масштабньй коэффициент Мд учесть при установке .двоичного кода разности и - и, на коммутаторе 35 блока 29 управления и выбрать его где f - тактовая частота генератора 33 импульсов; К - коэффициент усиления делите ля 8 частоты; п - количество разрядов регистров 14 и 15 сдвига, то при достижении условия 70 т. 21 S -2 и M() узел 37 сравнения блока 29 управления останавливает процесс вычисления показателя об возрастающей экспоненциальнойфункции, а величина показателя fL фиксируется в счетчике 18. Б режиме вычисления показателя убывающей экспоненциальной функции вида и , где U - начальное значение входного напряжения, устройство работает следующим образом. На выходе ключа 48 блока 29 управления действует сигнал логического нуля, который блокирует элементы И 25, И 43 и переключает коммутаторы 10 и 11 в состояние, при котором выходы пороговых элементов 1 и 2 .подключаются соответственно к входам запуска генераторов 3 и 4 одиночных импульсов. Блокировка элемента И 25 обеспечивает сохранение триггером 7 состояния, что обеспечивает режим суммирования в сумматоре-вычитателе 17. В режиме вычисления показателя экспоненциальной функции входы 31 и 32 эталонных напряжений подключают к источникам эталонных напряжений, задающих два уровня эталонного напряжения и и и„, а на информационный вход 30 устройства подается аналоговый сигнал, изменяющийся по экспонен U, циальному закону U Ug - начальное значение входного напряжения; (С - показатель экспоненциальной функции; t - время. Б исходном состоянии на выходах пороговых элементов 1 и 2 действуют сигналы логического нуля. Как только входное напряжение, действующее на информационном входе 30, достигает первого уровня эталонного напряжения и , срабатывает пороговый элемент 1, на выходе которого формируется сигнал логической единицы. Выходной сигнал порогового элемента 1 через коммутатор 10 запускает генератор 3 одиночных импульсов, на тактовый вход которого с выхода ключа 47 блока 2.9 управления поступает последовательность импульсов. Выходной импульс генератора 3 одиночных импульсов устанавливает триггер 5 в единичное состояние и через элемент ИЛИ 20 запускает преобразователь 9 аналогдлительность импульса. На прямом выходе триггера 5 формируется сигнал логической единицы, снимающий блокировку элементов И 21 и 24. Последовательность импульсов первого разряда распределителя 34 импульсов блока 29 управления поступает через элемент И 21 на первый вход сумматора 16 так как на выходе преобразователя 9 аналог-длительность импульса формируется импульс, длительность которого пропорциональна аналоговому сигналу, действующему на информационном входе 30 устройства.

На первый вход сумматора 16 поступает количество импульсов, пропордиональное длительности выходного импульса преобразователя 9 аналогдлительность импульса. Сумматор 16 за время п тактов, где п - количество разрядов регистра 14 сдвига по каждому импульсу на его первом входе, увеличивает на единицу младшего разряда двоичный код, сдвигаемый под действием синхронизирующих импульсов генератора 33 импульсов блока 29 управления с выхода регистра 14 сдвига. Последовательный двоичный код с выхода сумматора 16 за время п тактов записывается через коммутатор 13 в регистр 14 сдвига под действием синхронизирующих импульсов генератора 33 импульсов блока 29 управления. В результате к моменту окончания деиствид импульса на выходе преобразователя 9 аналог-длительность импульса в регистре 14 сдвига формируется двоичный код, значение которого пропорционально текущему значению напряжения, действующему на информационном входе 30 устройства.

Сигнал логической единицы прямого выхода триггера 5 через элемент 28 задержки на длительность тактового импульса снимает блокировку элемента И 24, через который на информационный вход делителя 8 частоты поступает последовательность импульсов с выхода 5 блока 29 управления. Коэффициент деления делителя 8 частоты выбирается таким образом, чтобы период следования выходных импульсов делителя 8 частоты был больше длительности выходного импульса преобразователя 9 аналог-длительность импульса для максимального уровня напряжения на йнформационном входе 30 устройства. Поэтому импульс на выходе делителя 8 частоты сформируется после окончания

действия импульса на выходе преобразователя 9 анало -длительность импульса. Выходной импульс делителя 8 частоты через элемент ИЛИ 20 вновь запускает преобразователь 9 аналогдлительность импульса, который вновь формирует импульсный сигнал, длительность которого пропорциональна текущему значению напряжения на информационном входе 30 устройства. На первый вход сумматора 16 через элемент И 21 вновь поступает пачка импульсов выхода 58 блока 29 управления, количество импульсов в которой пропорционально длительности выходно.го импульса преобразователя 9 аналог-длительность импульса. Сумматор 16 к двоичному коду предыдущего значения экспоненциальной функции, сдвигаемому с выхода регистра 14 сдвига под дейС1вием синхронизирующих импульсов выхода 60 блока 29 управления, прибавляет количество импульсов, пропорциональное текущему значению экспоненциальной функции, а результат суммирования в виде п-разрядного двоичного кода записывается через коммутатор 13, начиная с младшего разряда в регистр 14 сдвига под действием синхронизирующих импульсов выхода 60 блока 29 управления.

В дальнейшем устройство работает аналогичным образом, а в регистре 14 сдвига накапливается двоичный код, значение которого пропорционально интегралу от аналогового сигнала экспоненциальной функции, действующей на информационном входе 30 устройства. Так будет продолжаться до тех пор, пока не сработает пороговый элемент 2 второго уровня эталонного напряжения U. В этом случае на выходе порогового элемента 2 формируется сигнал логической единицы, который запускает генератор 4 одиночных импульсов, на тактовом входе которого действует последовательность Импульсов выхода 56 блока 29 управления. Выходной сигнал генератора 4 одиночных импульсов устанавливает триггер 6 в единичное состояние, при котором сигнал инверсного выхода три гера 6 блокирует элементы И 21 и 24, а сигнал его прямого выхода снимает блокировку элементов И 22 и 23.

К моменту установки триггера 6 |В единичное состояние в регистре 14 ;сдвига накапливается двоичный код.

зна |еиие которого пропорционально интегралу от аналогового сигнала экспо ненциальной.функции за интервал времени между, событиями перехода входного аналогового сигнала экспоненциальной функции через первый и второй уровни эталонного напряжения. Так как элемент И 21 -бдакируется триггером 6 после устанойкиего в единичное состояние, -то. двоичный код регистра 1А сдвига циркулирует без изменения с выхода на его информационный вход через сумматор 16, коммутатор 13, а поступает через коммутатор 12

.последовательно во времени, начиная с младшего разряда, на вход суммато. ра вычитателя 17, на второй вход которого под действием синхронизирующих импульсов выхода 60 блока 29 управления сдвигается начальный нулеБОЙ двоичный код регистра 15 сдвига. За каждые п тактов работы устройства где п - количество разрядов регистров 14 и 15 сдвига, выполняется один цикл суммирования двоичных кодов регистров 14 и 15 сдвига. Поскольку выход сумматора-вычитателя 17 соединен с информационным входом регистра 15 сдвига, то в регистре 15 сдвига накапливается двоичный код, равный произведению количества циклов суммирования на величину двоичного кода регистра 14 сдвига. В это время десятичный счетчик 18 выполняет подсчет количества циклов суммирования сумматором-вычитателем 17, так как через каждые п тактов на его информационном входе действует импульс первого разряда распределителя 34 импульсов блока 29 управления, поступающий через элемент И 22. Так будет продолжаться до тех пор, пока двоичный код регистра 15 сдвига не достигнет заданного коммутатором 35 е5лока 29 управления двоичного,лсода.,

Двоичный код регистра 15 сдвигается под действием синхронизирующих импульсов выхода 60 блока 29 утфавления через сумматор-вычитатель Г/ и элемент И 23 на вход 29 блока управления, где сравнивается с заданным

значением.

Если двоичный код в регистре 15 сдвига достиг или превысил заданное значение, то блок 29 управления вырабатывает на выходе 57 сигнал, КОТОрый сбрасывает триггеры 5 и 6 в нулевое состояние, при котором элементы И 21-24 блокируются и вычисление показателя экспоненциальной функции заканчивается.

В счетчике, 18 фиксируется значенив показателя убывающей экспоненциальной функции, которое индицируется группой элементов 19 индикации.

Предлагаемое устройство вычисляетпоказатель убывающей экспоненциальной функции на основании соотношения

(e- ti-e- 4 y4- (6)

Из соотношения (5) следует, что показатель экспоненциальной функции

равен

Ид - и

.

(7)

1 ,a,,

при дбстижении условия

2 ( S и е ) (и -Uj )Кд , (8

где М I/it - масштабный коэффициент.

Последовательньш узел 37 сравнения блока 29 управления останавливает процесс вычисления показателя d экспоненциальной функций, величина которого фиксируется в счетчике 18. Масштабный коэффициент определяется из соотношения (А).

Узел 37 сравнения (фиг.З) блока 2 управления работает следзтощим образом.

В исходном состоянии триггеры 62 и 63 на годятся в нулевом состоянии, в которое их устанавливает через каждые п тактов последовательность импульсов выхода элемента 45 задержки блока 29 управления, поступакяцая на вход 72 сброса. На синхронизирующие входы триггеров 62 и 63 по вхоДЗ 71 поступает последовательность тактовых импульсов генератора 33 импульсов блока 29 управления,,

Каждые п тактов узел 37 сравнения осуществляет поразрядное сравнение двух последовательных двоичных кодов, поступающих, начиная с младшего разряда,на информационные входы 69 и 70.

Если на входе 70 действует сигнал логической единицы, а на входе 69 - сигнал логического нуля, то на выходе элемента И 64 формируется сигнал логической единицы, устанавливающий триггер 62 в единичное состояние и сбрасывающий триггер 63 в нулевое состояние. Если на входе 70 действует сигнал логического нуля, а на входе 69 сигнал логической единицы, то ла выходе элемента И 65 формируется сигнал логической единицы устанавливающий триггер 63 в единичное состояние и сбрасывающий триггер 62 в нулевое состояние. В случае комбинаций кодов 00 и -11 на входах 70 и 69 на выходах элементов И 64-65 действуют сигналы логического нуля, а триггеры 62 и 63 сохраняют предшествующее состояние. Если двоичный код, поступающий по входу 73 превьпиает двоичный код, дей ствукщий на входе 69, то спустя п тактов триггер 62 находится в единич ном состоянии и на выходе 73 действу ет сигнал логической единицы. В случае равенства двоичных кодов триггеры 63 и 62 сохраняют нулевое состояние и на выходе элемента ИЛИНЕ 66 формируется сигнал логической единицы. Если двоичный код на входе 70 меньше двоичного кода на входе 69 то спустя п тактов триггер 63 находится в единичном состоянии и на выходе 75 действует сигнал логической единицы. Формула изобретения Устройство для вычисления показателя экспоненциальной функции, содержащее первый и второй пороговые элементы, преобразователь аналог-дли тельность импульса, первый и второй генераторы одиночных импульсов, первый и второй RS-триггеры, сумматор, первый и второй регистры сдвига, сче чик, группу элементов индикации, делитель частоты, первый, второй, третий и четвертый элементы И, элемент ИЛИ, элемент задержки и блок управления, содержащий генератор импульсов, распределитель импульсов, первы коммутатор, узел сравнения, первый и второй элементы ИЛИ, первый и второй элементы И, элемент задержки, первый и второй ключи, при этом выход генератора импульсов соединен с входом распределителя импульсов, выходы с первого по п-й которого (где п - раз рядность регистров сдвига) соединены 1 7016 с информационными входами первого коммутатора, управляющий вход которого соединен с входом кода останова устройства, выходы первого коммутатора через первый элемент ИЛИ блока управления соединены с первым информационным входом узла сравнения, вход сброса и тактовьш вход которого соединены соответственно с выходом элемента задержки блока управления и выходом генератора импульсов, п-й выход распределителя импульсов соединен с первыми входами первого и второго элементов И блока управления, вторые входы которых соединены с выходами соответственно равенства и и превышения эталонного кода узла сравнения, выходы первого и второго элементов И блока управления соединены с первым и вторым входами второго элемента ИЛИ блока управления, третий вход которого соединен с выходом первого ключа, подключенного информационным входом к выходу генератора импульсов, п-й выход распределителя импульсов через элемент задержки блока управления соединен с информационным входом второго ключа, управляющие входы ключей соединены с входом задания режима работы устройства, выход второго ключа соединен с тактовыми входами первого и ; второго генераторов одиночных импульсов , выходы которых соединены с S-входами соответствующих RS-триггеров, R-входы которых соединены с выходом второго элемента ИЛИ блока управления, первый выход распределителя импульсов соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с инверсным и прямым выходами второго RS-триггера, прямой выход первого RS-триггера соединен с третьим входом первого элемента И, инверсный выход первого RS-триггера соединен с входами управления установкой кода регистров сдвига, выход первого элемента И соединен с первым входом сумматора, второй вход которого соединен с выходом первого регистра сдвига, первый вход третьего элемента И соединен с прямым выходом второго RS-триггера, выход первого ключа соединен с установочными входами счетчика и делителя частоты, выход генератора импульсов соединен с входами синхронизации

17

первого и второго регистров сдвига, установочные входы которых соединены с шиной логического нуля устройства, выход второго элемента И соединен с счетным входом счетчика, выходы разрядов которого соединены с соответствующими входами группы элементов индикации, информационный вход устройства соединен с первыми входами первого и второго пороговых элементов и с информационным входом преобразователя аналог-длительность импульса, выход которого подключен к четвертому входу первого элемента И, второй вход первого порогового элемента соединен с входом первого эталонного напряжения устройства, вход второго эталонного напряжения которого соединен с вторым входом второго порогового элемента, прямой выход первого RS-триггера соединен через элемент задержки с первым входом четвертого элемента И,, выход которого подключен к информационному входу делителя частоты, соединенного выходом с первым входом элемента ИЛИ выход которого подключен к входу запуска преобразователя аналог-длительность импульса, инверсный выход второго RS-триггера соединен с вторым входом четвертого элемента И., третий вход которого подключен к выходу второго ключа, выход первого-генератора одиночных импульсов подключен к второму входу элемента ИЛИ, отличающееся TeMj, что, с целью расширения области применеНИЛ путем вычисления показателя возрастающей или убывающей экспоненциальной функции, в него введены сумматор-вычитатель, первьм, второй, третий и четвертый коммутаторы, Sтриггер, пятый элемент И, первый и второй элементы НЕ, а блок управления содержит второй коммутатор, третий элемент ИЛИ, третий элемент И, третий ключ и элемент НЕ, причем выходы с первого по п-й распределителя импульсов соединены с информационными входами второго коммутатора блока управления, управляклдий вход которого соединен с входом кода установившегося значения напряжения устройства, выходы второго коммутатора блока управления через третий элемент ИЛИ соединены с первым входом третьего элемента И блока управления, соединенного вторым входом с выходом третьего ключа, управляющий вход кото7077018

рого соединен с входом задания вида экспоненциальной функции устройства, первый и второй информационные входы третьего ключа соединены соответстJ венно с шиной логического нуля устройства и с выходом элемента НЕ блока управления, вход которого подключен к шине логического нуля устройства, выход третьего ключа соединен

(О с управляющими входами первого и

второго коммутаторов и с первым входом пятого элемента И, выход третьего элемента И блока управления соединен с первым информационным вхоJ5 дом третьего коммутатора, управляющий вход которого соединен с прямым выходом второго RS-триггера и первым входом третьего элемента И, второй информационный вход узла сравнения

2Q соединен с выходом третьего элемента И, второй вход которого соединен с выходом сумматора-вычитателя, выход второго ключа соединен с R-входом S-триггера, S-вход которого соеди25 ней с выходом пятого элемента И, подключенного вторым входом к выходу

второго генератора одиночных импульсов, выходы первого и второго пороговых элементов соединены соответственно с первыми информационными входами первого и второго коммутаторов , выходы которых соединены соответственно с входами запуска первого и второго генераторов одиночных импульсов, вторые информационные входы первого и второго коммутаторов соединены соответственно с выходами первого и второго элементов НЕ, входы которых подключены соответственно к выходам второго и первого пороговых элементов, информационный вход первого регистра сдвига соединен с выходом четвертого коммутатора, управляющий вход которого подключен к прям;ому выходу S-триггера, выход сумматора соединен с вторым информационным входом третьего коммутатора и с первым информационным входом четвертого коммутатора, второй информационный вход которого соединен с информационным входом второго регистра сдвига и выходом сумматоравычитателя , прямой и инверсный выходы S-триггера соединены с входами управления знаком суммирования сумма5 тора-вычитателя,первый и второй иифор мационные входы которого подключены соответственно к выходу второго регистра сдвига и к выходу третьего коммутатора .

t5

Т f

Ц Ч

Ш gp H-Tf

fPu2.1 157

59

55

ftS

Фи.г.2

70

73

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1335989A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Устройство для контроля экспоненциальных процессов | 1984 |

|

SU1282087A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1984 |

|

SU1272342A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при исследовании процессов различной физической природы, которые описываются экспоненц11альной функцией. Изобретение позволяет определять показатель экспоненциальной возрастающей и убывающей функции за время ее изменения между двумя эталонными значения-. ми. Устройство содержит два пороговых элемента, два генератора одиночных импульсов, два RS-триггера, Sтриггер, делитель частоты, преобразователь аналог-длительность импульса, четыре коммутатора, два регистра сдвига, сумматор, сумматор-вычитатеЛь, счетчик, группу элементов индикации, элемент ИЛИ, пять элементов И, два элемента НЕ, элемент задержки, блок (Л управления. Устройство работает в двух режимах. 4 ил. с

ff etfff

(г О, fS

и,

Ut

| РОТАЦИОННЫЙ УНИВЕРСАЛЬНЫЙ КОМБИНИРОВАННЫЙ АГРЕГАТ | 2000 |

|

RU2206967C2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления показа-ТЕля эКСпОНЕНциАльНОй фуНКции | 1979 |

|

SU824230A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-15—Публикация

1985-05-06—Подача