держки, а выход элемента памяти - выходом блока задержки.;

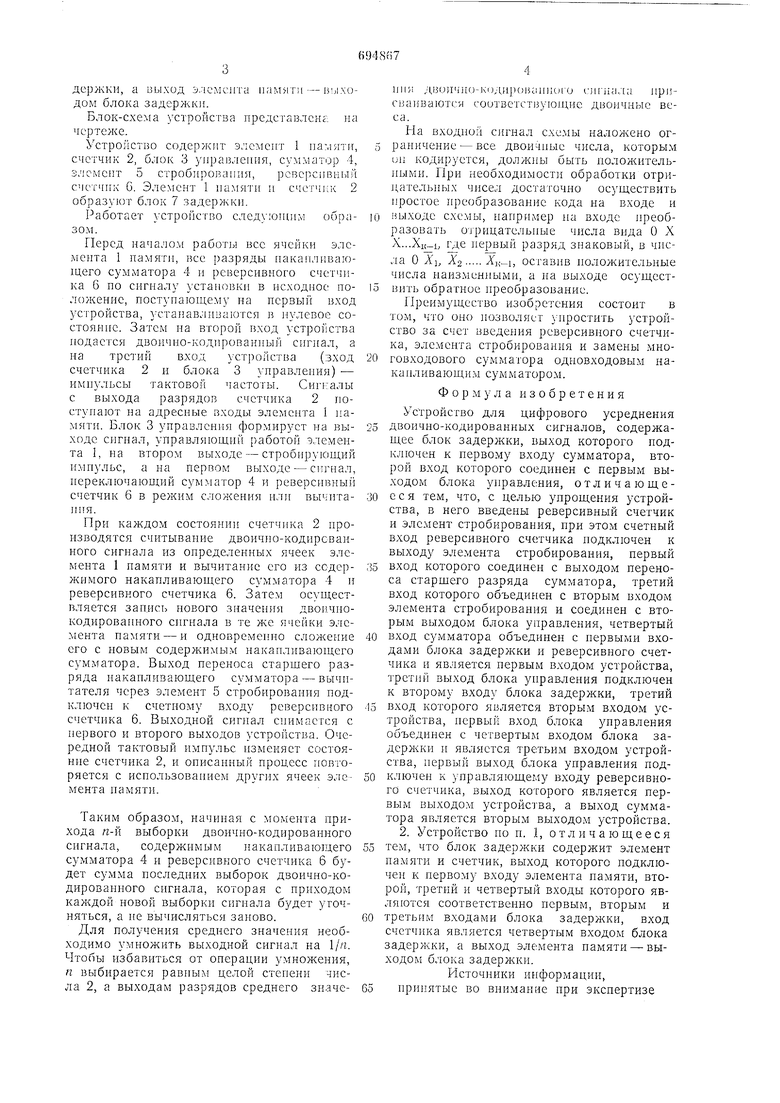

Блок-схема устройства представлена на чертеже.

Устройство содержит элемент 1 памяти, счетчик 2, блок 3 управления, сумматор 4, элемент 5 стробирования, реверсивный счетчик 6. Элемент 1 памяти и счетчнк 2 образуют блок 7 задержки.

Работает устройство следуюпшм образом.

Перед началом работы все ячейки элемента 1 памяти, все разряды накапливающего сумматора 4 и реверсивного счетчика 6 по сигналу установки в исходное положение, поступающему на первый вход устройства, устанавливаются в нулевое состояние. Затем на второй вход устройства подается двоично-кодированный сигнал, а на третий вход устройства (вход счетчика 2 и блока 3 управления) - импульсы тактовой частоты. Сигналы с выхода разрядов счетчика 2 поступают на адресные входы элемента 1 памяти. Блок 3 управлепия формирует на выходе сигнал, управляющий работой элемента 1, на втором выходе - стробирующий импульс, а па первом выходе - сигнал, переключающий сумматор 4 и реверсивный счетчик 6 в режим сложения или вычитания.

При каждом состоянии счетчика 2 производятся считывание двоично-кодированного сигнала из определенных ячеек элемента 1 памяти и вычитание его из содержимого накапливающего сумматора 4 и реверсивного счетчика 6. Затем осуществляется заплсь нового значения двоичнокодированного сигнала в те же ячейки элемента памяти - иодновременно сложение его с новым содержимым накапливающего сумматора. Выход переноса старшего разряда накапливающего сумматора - вычитателя через элемент 5 стробирования подключен к счетному входу реверсивного счетчика 6. Выходной сигнал снимается с первого и второго выходов устройства. Очередной тактовый импульс изменяет состояние счетчика 2, и описанный процесс повторяется с использованием других ячеек элемента памяти.

Таким образом, начиная с момента прихода л-й выборки двоично-кодированного сигнала, содержимым накапливающего сумматора 4 и реверсивного счетчика 6 будет сумма последних выборок двоично-кодированного сигнала, которая с приходом каждой новой выборки сигнала будет уточняться, а не вычисляться заново.

Для получения среднего значения необходимо умножить выходной сигнал на 1/п. Чтобы избавиться от операции умножения, п выбирается равным целой стенени числа 2, а выходам разрядов среднего значения двоично-кодированного сигнала присваиваются соответствующие двоичные веса.

На входной сигнал схемы налол ено ограничение - все двоичные числа, которым он кодируется, должны быть положительными. При необходимости обработкиотрицательных чисел достаточно осуществить простое преобразование кода на входе и

выходе схемы, например на входе преобразовать отрицательные числа вида О X X...Xi(b гд,е первый разряд знаковый, в числа О Xi, оставив положительные

числа наизменными, а на выходе осуществить обратное преобразование.

Преимущество изобретения состоит в том, что оно позволяет упростить устройство за счет введения реверсивного счетчика, элемента стробирования и замены многовходового сумматора одновходовым накапливающим сумматором.

Формула изобретения

Устройство для цифрового усреднения

двоично-кодированных сигналов, содержащее блок задержки, выход которого подключен к первому входу сумматора, второй вход которого соединен с первым выходом блока управления, отличающеее я тем, что, с целью упрощения устройства, в него введены реверсивный счетчик и элемент стробирования, при этом счетный вход реверсивного счетчика подключен к выходу элемента стробирования, первый

вход которого соединен с выходом переноса старщего разряда сумматора, третий вход которого объединен с вторым входом элемента стробирования и соединен с вторым выходом блока управления, четвертый

вход сумматора объединен с первыми входами блока задержки и реверсивного счетчика и является первым входом устройства, третий выход, блока управления подключен к второму входу блока задержки, третий

вход которого является вторым входом устройства, первый вход блока управления объединен с четвертым входом блока задержки и является третьим входом устройства, первый выход блока управления подключен к управляющему входу реверсивного счетчика, выход которого является первым выходом устройства, а выход сумматора является вторым выходом устройства. 2. Устройство по п. 1, отличающееся

тем, что блок задержки содержит элемент памяти и счетчик, выход которого подключен к первому входу элемента памяти, второй, третий и четвертый входы которого являются соответственно первым, вторым и

третьим входами блока задержки, вход счетчика является четвертым входом блока задержки, а выход элемента памяти - выходом блока задержки.

Источники информации,

принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 4Q5714, НОЗН 7/10, 1975. 2. «Электроника № 22, 1970, с. 20 (перевод с английского).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления скользящего среднего | 1986 |

|

SU1410058A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для анализа случайных процессов | 1980 |

|

SU955089A1 |

| Вероятностный коррелометр | 1981 |

|

SU1049921A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1984 |

|

SU1243015A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

Авторы

Даты

1979-10-30—Публикация

1976-08-09—Подача