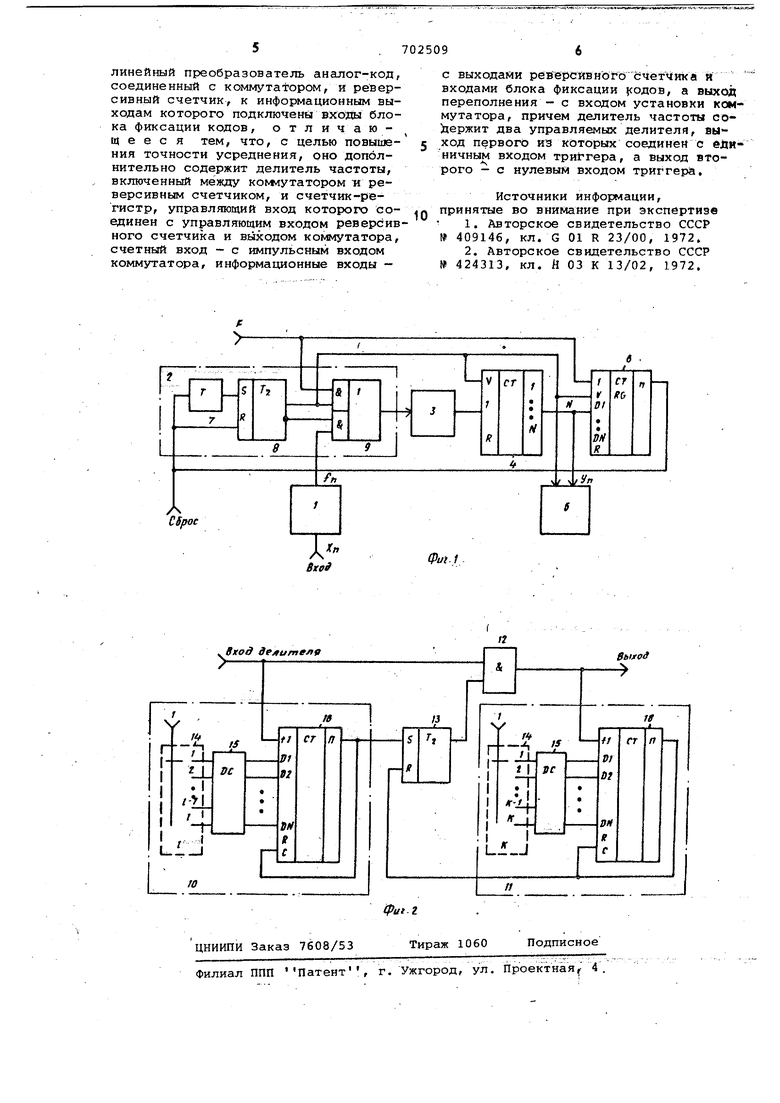

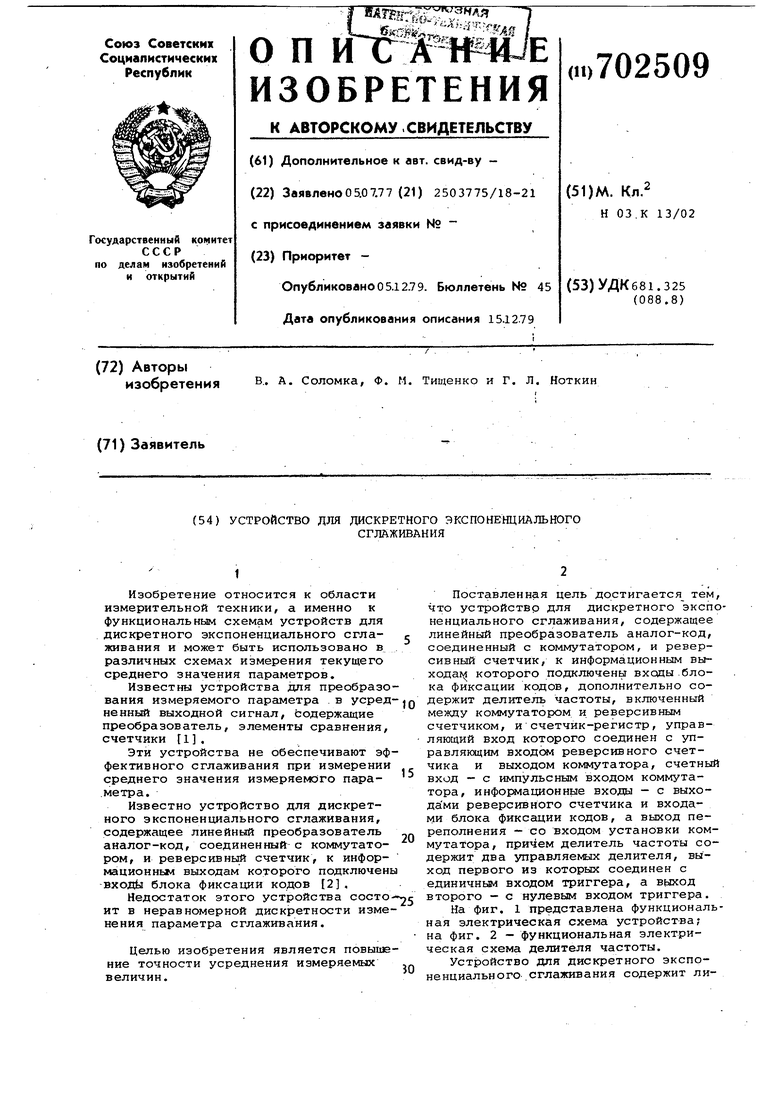

нейньй преобразователь авалог-код 1 (например} п| еобразователь аналог-частота) , коммутатор 2, к выходу которо го подключен делитель частоты 3, соединенный с реверсивным счетчиком 4, к информациониьм выходам которого подключены блок фиксаций кода 5 и счетчйк-регистр 6. Коммутатор 2 включает последовательно включенные элемент задеркки 7, триггер 8 и элемен 2И/ИЛИ 9. Один из импульсных входов элемента 2И/ИЛИ 9 соединен со счетным входом счетчика-регистра 6 с шиной импульсов, другой - с преобразователе аналог-частота 1. Выход счетчика-регистра б подключен к нулевому, а через элемент зГадержки 7 к единичному входу триггера 8, единичный выход которого соединен с управляющими входами счетчика 4, счетчика-регистра б и блока фиксации кодов 5. Делитель частоты 3 (см. фиг. 2) вы полнен на двух управляемых делителях 10 и 11, элементе И 12 и триггере 13 Каждый управляемый делитель 10 и 11 состоит иэ переключателя 14, дешифратора 15 и счетчика 16, информационныё входы (Д1...ДЫ) которого соеди нены с дешифратором, вход делителя 3 соединен со счетным входом счетчика 16 делителя 10 и через схему И 12 - со счётным входом счетчика 16 делите ля 11. Йлходы делителей 10 и 11 соединённ соответственно с единичным и нулевым входами триггера 13 и со ;вхо дами синхронизации счетчиков 16. В исходном состоянии делитель частоты 3, реверсивный счетчик 4 и сче чик-регистр 6 установлены в нулевое Сброс подают состояние и на вход импульс, который устанавливает в нул вбё состояние триггер 8 и запускает схему задержки 7. При наличии на входе устройства ШмерЙемсЙ вШйчЙньГ х :-йШ$ШьШ с выхода преобразователя 1 через элемент 2И/ИЛИ 9 поступают на вход делителя частоты 3. Коэффициенты деления Е и К управляемых делителей 10 и 11 устанавливают с помощью переключателей 14. . Дешифраторами 15 коэффициенты деления К и преобразуются в двоичные коды, и в мсйиент появления импульсов переполнения на выходах управляемых делителей коды переписываются в счет чики, определяя коэффициенты деления. При поступлении на вход первого управляемого делителя 10 импульсов с выхода коммутатора 2 на выходе делителя получают импульс, который устанавливает триггер 13 в единичное состояние. Потенциал с выхода триггера 13 от КЕЯлвает схему И 12 и входные импульсы поступают на делитель 11, с выхода кот о каждый К-й импульс посту пает на триггер 13 и устанав ливает его в нулевое состояние. Такое выпол- , нение делителя позволяет реализовать любой дробно-рациональный коэффициент еления делителя 3 равный - при К Е - 1.1 Импульсы с выхода делителя 3 поступают в течение времени Т (Т - параметр схемы задержки 7) на счетчик 4, установленный первоначально потёнци- : алом с выхода триггера 8 по управляющему входу, на сложение. Счетчик просчитывает импульсы, соответствующие частоте - , где f - средняя частота следованиявходных импульсов с преобразователя 1; Р - коэффициент деления делителя 3. Через время Т после подачи импульса на вход Сброс с выхода схемы задержки 7 на вход триггера 8 поступает первый тактовый импульс, который устанавливает триггер в состояние переписывает накопленный к этому моменту в реверсивном счетчике 4 код У - Т в блок фиксации кода 5 и счетчик-регистр 6 и включает реверсивный счетчик 4 по управляющему входу V на вычитание. : йа вход делителя частоты 3 через .элемент 2И/ИЛИ 9 начинают поступать импульсы,с шины счетных импульсов и реверсивный счетчик 4 просчитывает частоту Тгр , где F - частота счетных импульсов. Одновременно счетчик-регистр, работающий на вычитание, начинает просчитывать частоту F и через время t - на выходе переполнения счетчика-регистра б появляется импульс, который устанавливает триггер 8 в состояние О, переключает реверсивный счетчик 4 на сложение и запускает схему задержки 7. За время t реверсивный счетчик 4 просЧиты1вЖёт число импульсов, равное E-i и в момент установки триггера 8 О в счетчике 4 будет в состояние записан код К приходу п-го тактового импульса с выхода схемы задержки 7 в счетчике 4 будет записан Код где с(. - - - любое Дробно-рациональное число в диапазоне от О до 1. Таким образом в устройстве для дискретного экспоненциального сглаживания устраняется систематическая погрешность, а параметр сглаживания может изменяться от О до 1 и тем caNtHM повышается точность усреднения иэмеряемых величин Формула изобретения Устройствр дли дискретного экспоненциального сглаживания, содержащее

линейный преобразователь аналог-код, соединенный с коммутатором, и реверсивный счетчик, к информационным выходам которого подключены входаа блока фиксации кодов, отличающееся тем, что, с целью повышения точности усреднения, оно дополнительно содержит делитель частоты, включенный между коммутатором и реверсивным счетчиком, и счетчик-регистр, управляющий вход которого соединен с управляющим входом реверсивного счетчика и выходом коммутатора, счетный вход - с импульсным входом коммутатора, информационные входы -

с выходами рейтерсйвного счетчика н входами блока фиксации , а выход переполнения - с входом установки коммутатора, причем делитель частоты содержит два управляемьк делителя, выход первого из которых соединен с елиничным входом три1:гера, а выход второго - с нулевым входом триггера.

Источники информации, принятые во внимание при экспертизе

0

1.Авторское свидетельство СССР 409146, кл. G 01 R 23/00, 1972.

2.Авторское свидетельство СССР 424313, кл. Л 03 К 13/02, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

| Устройство для измерения девиации частоты линейно-частотно-модулированного колебания | 1989 |

|

SU1711087A1 |

| Устройство для измерения механической скорости бурения | 1979 |

|

SU863843A1 |

| Цифровой генератор функций | 1974 |

|

SU506845A1 |

| Устройство для сглаживания периодических случайных сигналов | 1981 |

|

SU982012A1 |

| Устройство символьной синхронизации | 1990 |

|

SU1775869A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Цифровой кодирующий преобразователь частоты следования импульсов | 1980 |

|

SU919080A1 |

Авторы

Даты

1979-12-05—Публикация

1977-07-05—Подача