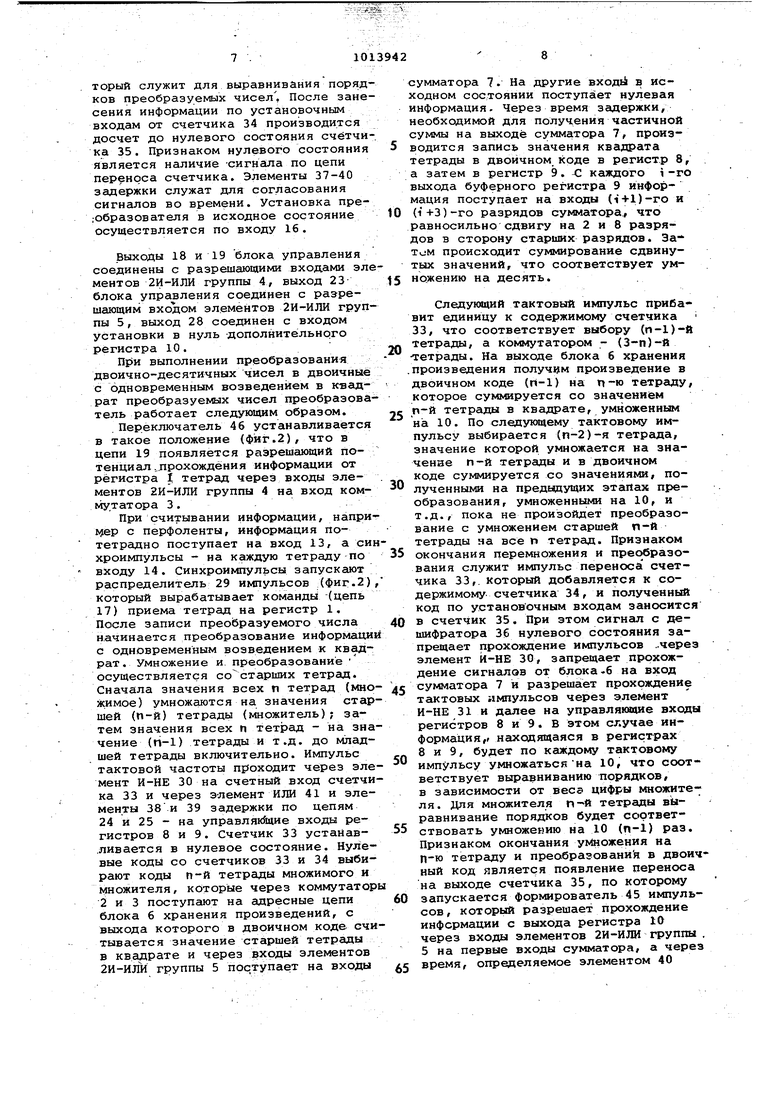

третий счетчики, дешифратор нулевого состояния, четыре элемента задержки, первый и второй элементы ИЛИ элемент 2И-ИЛИ, RS-триггер, формирователь импульсов и первый и второй переключатели, входы которых соединены с входом логического нуля преобразователя, а нулевой и единичный выходы первого переключателя являются соответственно первым и вторым выходами режима работы блока управлений, вход синхронизации которого соединен с синхровходом распределителя импульсов, выход которого является первым выходом разре11:ения записи блока управления, вход сброса которого соединен с входом сброса распределителя импульсов, с входами сброса первого, второго и третьего счетчиков, R-входом К5-триггера первым входом первого элемента ИЛИ и является вторым выходом сброса блока управления, цервый выход сброса которого соединен с выходом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента задержки и является четвертым выходом разрешения записи блока управления, второй и третий выходы разрешения записи которого соединены соответственно с выходами последовательно соединенных второго и третьего элементов задержки, вход третьего элемента задержки соединен с вы ходом второго элемента ИЛИ, первый вход которого соединен с выходом первого элемента и со счетным входом первого счетчика, выход переполнения которого, соединен со счетным входом второго счетчика и через

четвертый элемент задержки - с управляющим входом приема третьего счетчика и первым входом элемента 2И-ИЛИ, второй вход которого соединен с выходом второго переключателя, а третий и четвертый входы элемента 2И-ИЛИ соединен с выходом переполнения второго счетчика, разрядные выходы которого соединены -с информационными входами третьего счетчика, 1выход переполнения которого соединен JC входом первого элемента згщержки и через формирователь импульсов с первым выходом обратной связи блока управления, второй выход обратной связи которого соединен с первым входом первого элемента И-НЕ и через элемент НЕ - с первым входом второго элемента И-НЕ, а также с выходом дешифратора нулевого состояния, входы которого соединены с разрядными выходами третьего счетчика, счетный вход которого соединен с вторым входом второго элемента ИЛИ и с выходом второго элемента И-НЕ, второй вход которого соединен с вторьпл входом первого элемента И-НЕ и с выходом КЗ-триггера, S.-вход которого соединен с выходом элемента 2И-ИЛИ, третий вход первого элемента И-НЕ соединен с выходом запрета распределителя импульсов, .а четвертый вход первого элемента И-НЕ соединен с третьим входом второго элемента И-НЕ и является тактовым входом блока управления, первый и второй выходы управления умножением которого соединены соответственно с разрядными выходами первого и второго счетчиков ..

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичного кода | 1984 |

|

SU1208607A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

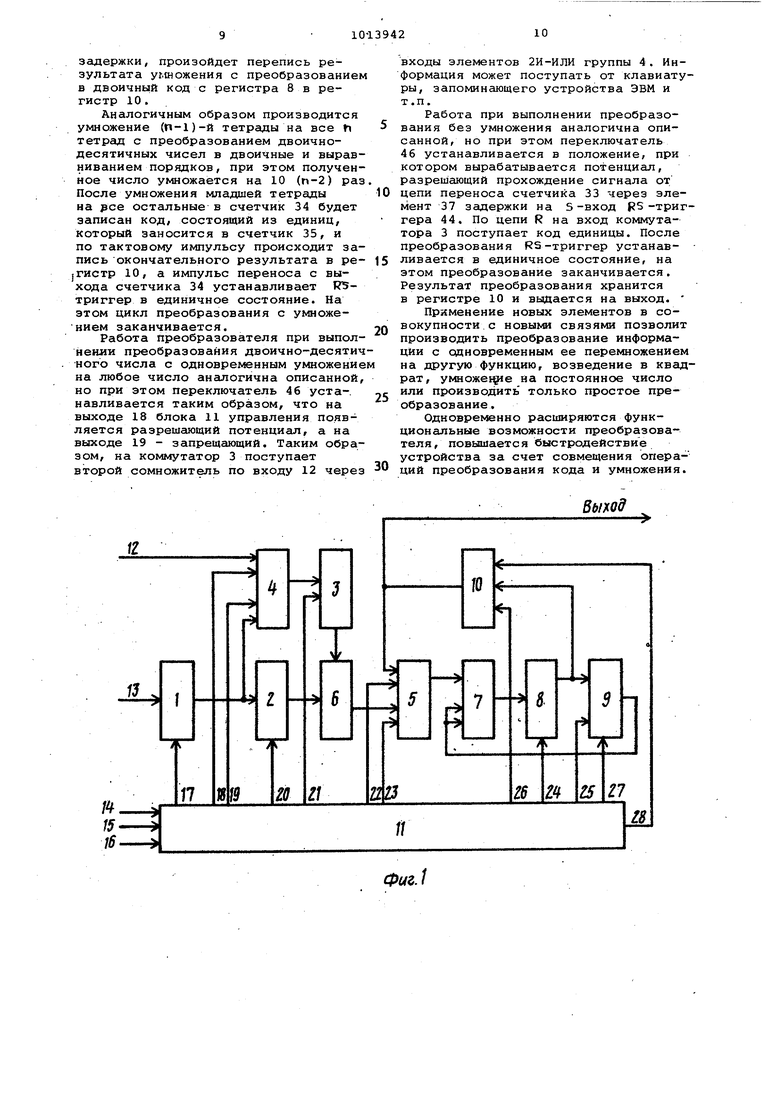

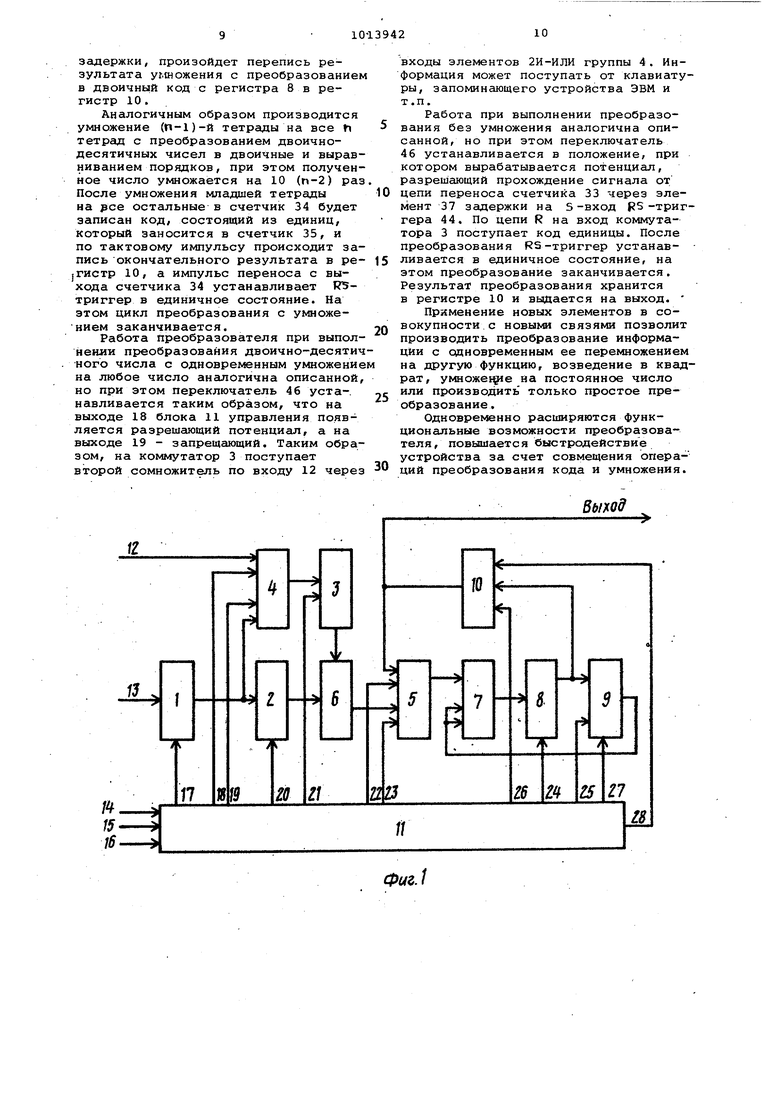

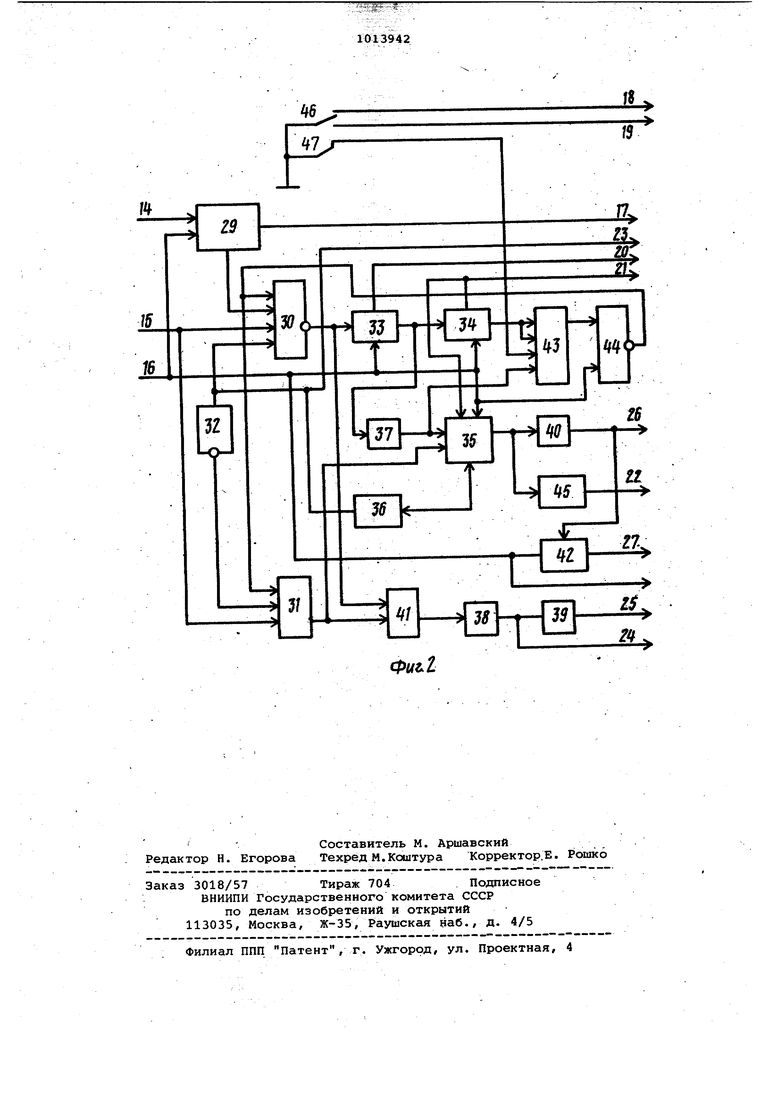

1. ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОДЕСЯТИЧНОГО КОДА Б ДВОИЧНЫЙ, содержащий регистр тетрад, сумматор, блок управления, основной регистр и буферный регистр, информационные входы которого срединены с выходами основного регистра, информационные входы которого соединены с выходами сумматора, первые Ьходаа (i+l)-ro и (i+3)-ro разрядов которого соединены с выходом i-ro разряда буферного регистра () , где (п+З) число разрядов выxoд oгo кода, вход регистра тетрад являетс.я информационным входом преобразователя, вход синхронизации, тактовый вход и вход сброса которого являются соответственно входом синхронизации, тактовым входом и входом сброса блока управления, первый, второй и третий выходы разрешения записи которого соединены соответственно с управляющими входами регистра тетрад, основиого и, буферного регистров, вход сброса последнего соединён с первым выходом сброса блока управления, .отлич аю.щи и с я тем, что, с целью распшрения функциональных возможностей путем обеспечения преобразования с масштабированием и одновременным возведением в квадрат. и повьшения быстродействия, в него введены первый и второй кокву1утаторы первая и вторая группы элементов 2И-ИЛИ, блок хранения произведений и дополнительный регистр, информационные входы которого соединены с выходами основного регистра, вход сброса соединен с вторым выходом сброса блока управления, четвертый вахоя разрешения записи которого соединен с управляющим уходом дополнительного регистра, выходы которого являются выхспом преобразователя и соединены с первыми входами Элементов 2И-ИЛИ второй группы, вторые входы которых соединены с выходами .блока хранения произведений, первый, и второй входы которого соединены соответственно с выходами первого и второго коммутаторов, управляющие СП входы которых соединены соответственно с первым и вторым выходами -управления умножением блока управления, первый и второй выходы приз§ наков обратной связи которого соеди-, нены соответственно с третьими и четвертыми вводами элементов 2И-ИЛИ второй группы, выходы которых соединены с вторыми входами сукматора, информационные входы второго коммусо со татора соединены с выходами элементов 2И-ИЛИ первой группы, первые входы которых соединены с масштабным и Is9 входом преобразователя,, вторые входы соединены с выходами регистра тетрад и информационными входами пер- вого коммутатора, а третьи и четвертые входы элементов 2И-ИЛИ группы соединены соответственно с первым и вторым выходами режима работы блока управления, вход логического чуля которого является входом . .логического нуля преобразователя. 2. Преобразователь по п. 1, отличак) тем, что блок управления содержит распределитель импульсов, первый и второй элементы И-НЕ, элемент НЕ, первый, второй и

Известен преобразователь двоичнодесятичного кода в двоичный, содержшдий регистр числа, блок управления блок хранения эквивалентов, два сумматора и два регистра

Недостаток данного преобразователя состоит в «изком быстродействии связанном.с последовательным принципом работы, а также в невозможности масштабирования.

Наиболее близким по технической сущностиК изобретению является преобразователь двоично-десятичного

кода в двоичный, содержащий регистр тетрад, сумматор, выходной регистр, состоящий из осйовного и буферного регистров, причём выходы сумматора через основной регистр подключены ко входам буферного регистра, выход i-го ) разряда буферного регистра соединен со входами (i+l)-rp и (i+3)-го разрядов сумматора СЗ.

Недостаток известного преобразователя состоит в невозможности производить преобразование с одновременным умножением, а также в относительно низком быстродействии.

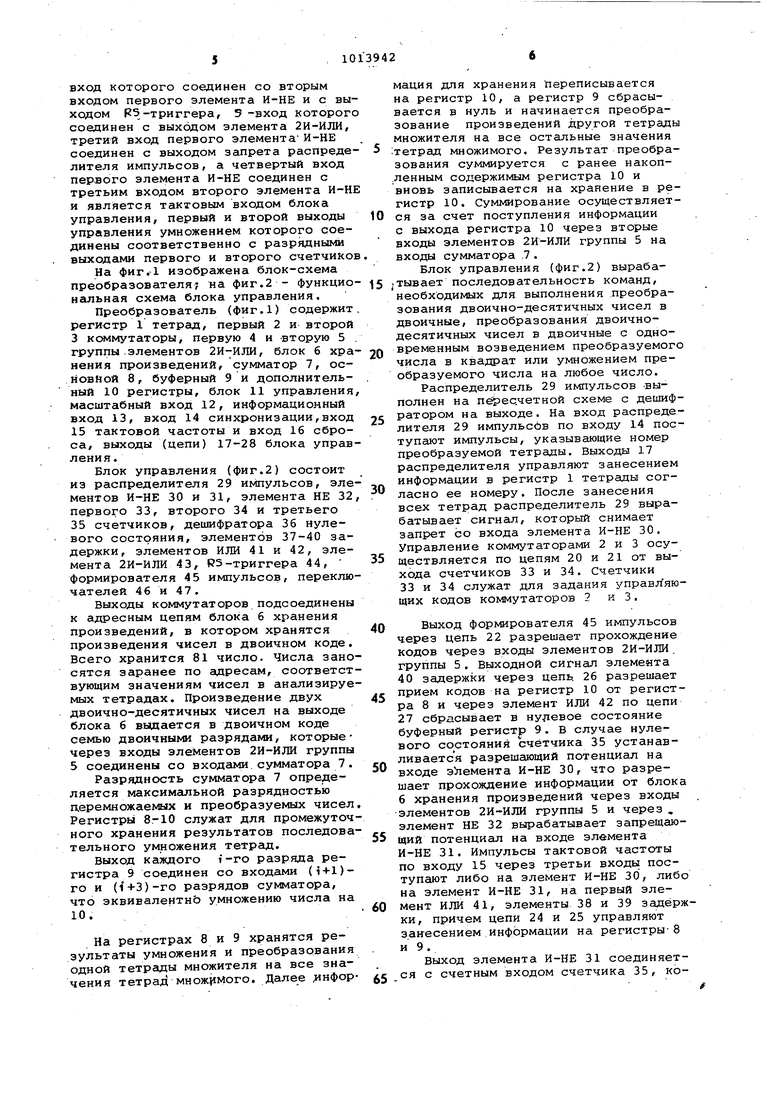

Цель изобретения -.расширение функциональных возможностей преобразователя за счет обеспечения преобразования с масштабированием и одновременным возведением в квадрат и повышение быстродейстрия. Поставленная цель достигается т.ем что в преобразователь двоично-десятичного кода в двоичный, содержащий регистр тетращ, сумматор, блок управ ления, основной регистр и буферный регистр, информационные входы которогр соединены с- выходами основного регистра, информационными входами соединенного с выходами сумматора, первые входы (i+l)-ro и (i-f3)-ro которого соединены с выходом i-го разряда буферного регистра (i 1-п) , где (п+3) - число разрядов выходного кода, вход регистра тетрад является информационным входом преобразователя, вход синхронизации, тактовый вход и вход сброса которого являются соответственно входом синхронизации, тактовым входом и входом сброса блока управления, первый, второй и третий выходы разрешения записи которого соединены соответственно с управляющими входами регистра тетрад, ОСНОВНОГО и буферного регистров, вход сброса последнего соединен с первым выходом сброса блока управления, введены первый и второй коммутаторы, первая и вторая группы элементов 2И-ИЛИ, блок хранения произведений и дополнительный регист информационные входы которого соедииены с выходами основного регистра, вход сброса соединен со вторым выходом сброса, блока управления, четвертый выход разрешения записи которого соединен с управляющим входом дополнительного регистра, выходы которого являются выходом преобразова теля и соединены с первыми входами элементов 2И-ИЛИ второй группы, вто рые входы которых соединены с выходами блока хранения произведений, первый и второй входы которого соединены соответственно с выходами , первого и второго коммутаторов, управляющие входы которых соединены соответственно с первым и вторым вы ходами управления умножением блока управления, первый и второй выходы признаков обратной связи которого соединены соответственно с третьими и четвертыми входами элементов 2И-ИЛИ второй группы, выходы которы соединены со вторыми входами сумматора, информационные входал второго коммутатора соединены с выходами элементов 2И-ИЛИ первой группы, пер вые входы которых соединены с масш.табным входом преобразователя, вторые входы соединены с выходами регистра тетрад и информационными вхо дами первого коммутатора,а третьи и четвертые входы элементов 2И-ИЛИ первой группы соединены соответственно с первым и вторым выходами ре жима работы блока управления, вход логического нуля которого является вх дом лoi7ичecкoгo нуля преобразователя Блок управления содержит распределитель импульсов, первый и второйэлементы И-НЕ, элемент НЕ, первый, второй и третий счетчики, дешифратор нулевого состояния, четыре элемента задержки, первый и второй элементы ИЛИ, элемент 2И-ИЛИ, R5-триггер, формирователь импульсов и первый и второй переключатели, входы которых. соединены с входом логического нуля преобразователя, а нулевой и единичный выходы первого переключателя явлтотся соответственно первым и вторым выходами режима работы блока управления, вход синхронизации которого соединен с синхровходом .распределителя Импульсов, выход которого является первым выходом разрешения записи блока управления, вход сброса которого соединен со входом сброса распределителя импульсов, со .входами Сброса первого, второго и третьего счетчиков, R-входом R3-триггера, первым входом первого элемента ИЛИ и является вторым выходом сбрсхза блока управления, первый выход сброса которого соединен с выходом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента задержки и является четвертым выходом разрешения записи блока управления, второй и третий выходы разрешения записи которого соединены соответственно с выходами последовательно соединенных второго и третьего элементов задержки, вход третьего элемента задержки соединен с ,выходом второго элемента ИЛИ, первый вход которого соединен с выходом первого элемента И-НЕ и со счетным входом первого счетчика, выход переполнения которого соединен со счетным входом второго счетчика и через четвертый элемент задержки - с управлякнцим входом приема третьего счетчика и первым входом элемента 2И-ИЛИ, второй вход которого соединен с выходом второго переключателя, а третий и четвертый входы элемента 2И-ИЛИ соединены с выходе переполнения второго счетчика, разрядные выходы которого соединены с информационньвш входами третьего счетчика, выход переполнения которого соединен со входом первого элемента задержки и че-. рез формирователь импульсов - с первым выходом обратной связи блока управления, второй ЁЫХОД обратной связи которого соединен с первым входе первого элемента И-НЕ и через элемент НЕ - с первым входом второго элемента И-НЕ, а также с выходом дешифратора нулевого состояния, входы которого соединены с разрядными выходами третьего счетчика, счетный вход которого соединен со вторым ,входом второго элемента ИЛИ и с выходом второго элемента И-НЕ, второй вход которого соединен со вторым входом первого элемента И-НЕ и с вы ходом R5-триггера, 5 -вход которог соединен с выходом элемента 2И-ИЛИ, третий вход первого элемента И-НЕ соединен с выходом запрета распреде лителя импульсов, а четвертый вход первого элемента И-НЕ соединен с третьим входом второго элемента И-Н и является тактовым входом блока управления, первый и второй выходы управления умножением которого соединены соответственно с разрядными выходами первого и второго счетчико На фиг.1 изображена блок-схема преобразователя; «а фиг.2 - функцио нальная схема блока управления. Преобразователь (фиг.1) содержит регистр 1 тетрад, первый 2 и второй 3 коммутаторы, первую 4 и -вторую 5 группы.элементов 2И-ИЛИ, блок 6 хра нения произведений, сумматор 7, основной 8, буферный 9 и дополнительный 10 регистры, блок 11 управления масштабный вход 12, информационный вход 13, вход 14 синхронизации,вход 15 тактовой частоты и вход 16 сброса, выходы (цепи) 17-28 блока управ ления. Блок управления (фиг.2) состоит из распределителя 29 импульсов, эле ментов И-НЕ 30 и 31, элемента НЕ 32 первого 33, второго 34 и третьего 35 счетчиков, дешифратора 36 нулевого состояния, элементов 37-40 задержки, элементов ИЛИ 41 и 42, элемента 2И-ИЛИ 43, РЗ-триггера 44, формирователя 45 импульсов, переклю чателей 46 и 47. Выходы коммутаторов подсоединены к адресным цепям блока б хранения произведений, в котором хранятся произведения чисел в двоичном коде. Всего хранится 81 число. Числа зано сятся заранее по адресам, соответст вующим значениям чисел в анализируе мых тетрадах. Произведение двух двоично-десятичных чисел на выходе блока 6 вьщается в двоичном коде семью двоичными разрядами, которыечерез входы элементов 2И-ИЛИ группы 5 соединены со входами сумматора 7. Разрядность сумматора 7 определяется максимёшьной разрядностью перемножаемых и преобразуемых чисел Регистры 8г10 служат для промежуточного хранения результатов последовательного умножения тетргад. Выход каждого i-ro разряда регистра 9 соединен со входами (i+l)го и (1+3)-го разрядов сумматора, что эквивалентно умножению числа на 10. На регистрах 8 и 9 хранятся результаты умножения и преобразования одной тетрады множителя на все значения тетрад множимого. Далее Д1нформация для хранения переписывается на регистр 10, а регистр 9 сбрасывается в нуль и начинается преобразование произведений другой тетрады множителя на все остальные значения тетрад множимого. Результат преобразования суммируется с ранее накопленным содержимым регистра 10 и вновь записывается на хранение в регистр 10. Суммирование осуществляется за счет поступления информации с выхода регистра 10 через вторые входы элементов 2И-ИЛИ группы 5 на входы сумматора 7. Блок управления (фиг.2) выраба;тывает последовательность команд, необходимых для выполнения преобразования двоично-десятичных чисел в двоичные, преобразования двоичнодесятичных чисел в двоичные с одновременным возведением преобразуемого числа в квадрат или умножением преобразуемого числа на любое число. Распределитель 29 импульсов -выполнен на п есчетной схеме с дешифратором на выходе. На вход распределителя 29 импульсбв по входу 14 поступают импульсы, указывгиощие номер преобразуемой тетрады. Выходы 17 распределителя управляют занесением информации в регистр 1 тетрады согласно ее номеру. После занесения всех тетрад распределитель 29 вырабатывает сигнсш, который снимает запрет со входа элемента И-НЕ 30. Управление коммутаторами 2 и 3 осуществляется по цепям 20 и 21 от выхода счетчиков 33 и 34. Счетчики 33 и 34 служат для задания управ яющих кодов коммутаторов 2 к 3. Выход формирователя 45 импульсов через цепь 22 разрешает прохождение кодов через входы элементов 2И-ИЛИ группы 5. Выходной сигнал элемента 40 задержки через цепь. 26 разрешает прием кодов на регистр 10 от регистра 8 и через элемент ИЛИ 42 по цепи 27 сбрасывает в ну 1евое состояние буферный регистр 9. В случае нулевого состояния счётчика 35 устанавливается разрешающий потенциал на входе элемента И-НЕ 30, что разрешает прохождение информации от блока 6 хранения произведений через входы элементов 2И-ИЛИ группы 5 и через , элемент НЕ 32 вырабатывает запрещающий потенциал на входе элемента И-НЕ 31. Импульсы тактовой частоты по входу 15 через третьи входы поступают либо на элемент И-НЕ 30, либо на элемент И-НЕ 31, на первый элемент ИЛИ 41, элементы 38 и 39 задержки, причем цепи 24 и 25 управляют занесением информации на регистры8 и 9. Выход элемента И-НВ 31 соединяется с счетным входом счетчика 35, который служит для выравнивания порядков преобразуемых чисел , После занесения информации по установочным входам от счетчика 34 производится досчет до нулевого состояния счётчика 35. Признаком нулевого состояния является наличие -сигнгша по цепи переноса счетчика. Элементы 37-40 задержки служат для согласования сигналов во времени. Установка пре;Образователя в исходное состояние осуществляется по входу 16.

Выходы 18 и 19 блока управления соединены с разрешающими входами элементов 2И-ИЛИ группы 4, выход 23блока управления соединен с разрешающим входом элементов 2И-ИЛИ группы 5, выход 28 соединен с входом установки в нуль -дополнительного регистра 10.

При выполнении преобразования двоично-десятичных чисел в двоичные с одновременным возведением в квадрат преобразуемых чисел преобразователь работает следующим образом.

Переключатель 46 устанавливается в такое положение (фиг.2), что в цепи 19 появляется разрешающий потенциал .прохождения информощии от регистра t тетрад через входы элементов 2И-ИЛИ группы 4 на вход коммутатора 3.

При считывании информации, наприtJfep с перфоленты, информация потетрадно поступает на вход 13, а синхроимпульсы - на каждую тетраду по входу 14. Синхроимпульсы запускают распределитель 29 импульсов (фиг.2) , который вырабатывает команды -(цепь 17) приема тетрад на регистр 1, После записи преобразуемого числа начинается преобразование информации с одновременным возведением к квадрат. Умножение и. преобразование осуществляется со старших тетрад. Сначала значения всех п тетрад (множимое) умножаются на значения старшей (п-й) тетрады (мнржитель); затем значения всех п тетрад - на значение (ri-1) тетрады и т.д. до младшей тетрады включительно. Импульс тактовой частоты проходит через элемент И-НЕ 30 на счетный вход счетчика 33 и через элемент ИЛИ 41 и элементы 38и 39 задержки по цепям 24 и 25 - на управлякйцие входы регистров 8 и 9. Счетчик 33 устанавливается в нулевое состояние. Нулевые коды со счетчиков 33 и 34 выбирают коды п-й тетрады множимого и множителя, которые через коммутаторы 2 и 3 поступают на адресные цепи блока 6 хранения произведений, с выхода которого в двоичном коде считывается значение старшей тетрады в квадрате и через входы элементов 2И-ИЛИ группы 5 поцтупает на входы

сумматора 7. На другие входь в исходном состоянии поступает нулевая информация. Через время задержки, необходимой для получения частичной суммы на выходе сумматора 7, производится запись значения квадрата тетрады в двоичном коде в регистр 8, а затем в регистр 9. С каждого i-го выхода буферного регистра 9 информация поступает на входы (i+l)-ro и

0 (1+3)-го разрядов сумматора, что равносильно сдвигу на 2 и В разрядов в сторону старших разрядов. За Том происходит суммирование сдвинутых значений, что соответствует умножению на десять.

Следукндий тактовый импульс прибавит единицу к содержимому счетчика 33, что соответствует выбору (п-1)-й тетрады, а коммутатором - (З-п)-й тетрады. На выходе блока 6 хранения .произведения получим произведение в двоичном коде (п-1) на п-ю тетраду, которое суммируется со значени(ем

5 п-й тетрады в квадрате, умноженным на 10. По следукнцему тактовому импульсу выбирается (п-2)-я тетрада, значение которой умножается на значение п-й тетрады и в двоичном коде суммируется со значениями, по0лученными на предыдущих этапах преобразования, умноженньми на 10, и т.д., пока не произойдет преобразование с умножением старшей п-й тетрады на все г тетрад. Признаком

5 окончания перемножения и преобразования служит импульс переноса счетчика 33,. который добавляется к содержимому, счетчика 34, и полученный код по установочным входам заносится

0 в счетчик 35. При этом сигнал с дешифратора 36 нулевого состояния запрещает прохождение импульсов ..через элемент И-НЕ 30, запрещает прохождение сигналов от блока 6 на вход

С сумматора 7 и разрешает прохождение тактовых импульсов через элемент И-НЕ 31 и далее на управлякйцие входы регистров 8 и 9. В этом случае информация, находяцаяся в регистрах 8 и 9, будет по каждому тактовому

импульсу умножаться на 10, что соответствует выравниванию порядков, в зависимости от весэ цифры множителя. Для множителя П-и тетрады выравнивание порядков будет сортвет5 ствовать умножению на Ю (п-1) раз. Признаком окончания умножения на П-ю тетраду и преобразований в двоичный код являетря появление переноса на выходе счетчика 35, по которому

0 запускается формирователь 45 импульсов , который разрешает прохождение информации с выхода регистра 10 через входы элементов 2И-ИЛИ группы . 5 на первые входы сумматора, а через

5 время, определяемое элементом 40 задержки, произойдет перепись результата умножения с преобразование в двоичный код с регистра 8 в регистр 10. Аналогичным образом производится умножение (п-1)-й тетрады на все П тетрад с преобразованием двоичнодесятичных чисел в двоичные и вырав ниванием порядков , при этом получен ное число умножается на 10 (п-2) ра После умножения младшей тетрады на рее остальные в счетчик 34 будет записан код, состоящий из единиц, который заносится в счетчик 35, и по тактовому импульсу происходит запись окончательного результата в ре(Гистр 10, а импульс переноса с выхода счетчика 34 устанавливает R5триггер в единичное состояние. На этом цикл преобразования с умножением заканчивается. Работа Преобразователя при выполнении преобразования двоично-десятич ного числа с одновременным умножение на любое число аналогична описанной но при этом переключатель 46 устанавливается таким образом, что на выходе 18 блока 11 управления появляется разрешающий потенциал, а на выходе 19 - запрещающий. Таким образом, на коммутатор 3 поступает второй сомножитель по входу 12 через

/

BbiJiOd

Фиг.1 входы элементов 2И-ИЛИ группы 4. Информация может поступать от клавиатуры, запоминающего устройства ЭВМ и т.п. Работа при выполнении преобразования без умножения аналогична описанной, но при этом переключатель 46 устанавливается в положение, при котором вырабатывается потенциал, разрешающий прохождение сигнала от цепи переноса счетчика 33 через элемент 37 задержки на 5-вход RS-триггера 44. По цепи R на вход коммутатора 3 поступает код единицы. После преобразования RS-триггер устанавливается в единичное состояние, на этом преобразование заканчивается. Результат преобразования хранится в регистре 10 и вьедается на выход. Применение новых элементов в совокупности, с новыми связями позволит производить преобразование информации с одновременным ее перемножением на другую функцию, возведение в квадрат, умноже1 е на постоянное число или производить только простое преобразование. Одновременно расширяются функциональные возможности преобразователя, повышается быстродействие устройства за счет совмещения операций преобразования кода и умножения.

Ф(/й2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь двоичнодесятичного кода в двоичный | 1977 |

|

SU656052A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США 3524976, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

Авторы

Даты

1983-04-23—Публикация

1981-12-31—Подача