тактовых импульсов подключен к счетным входам с второго по п-й управляемых делителей частоты, а каждьй i-й (2 i i i п) управляемый делитель частоты соединен выходом с входом аргумента i-ro цифроаналогового интерполятора, подключенного первым и вторым входами ординат к выходам соответственно (21-1)-го и 2i-ro цифроаналоговых преобразователей, причем блок разрешения обмена соединен первой группой входов с прямыми выходами триггеров первой группы, второй группой входов - с прямыми выходами триггеров второй группы, а выходом - с первыми входами первого элемента И и первого элемента И-НЕ, причем каждый i-й (1 . п +. 1) элемен И подключен вторым входом к инверсному выходу i-ro триггера первой группы, а выходом - к первым входам (i + 1)-го элемента И и (i « 1)-го элемента И-НЕ, каждый i-й элемент И-НЕ соединен вторым входом с прямым выходом i-ro триггера первой группы, а выходом - с единичным установочным входом i-ro триггера второй группы, подключенного инверсным выходом через i-й элемент задержки к входам обнулени i-x триггеров первой и второй групп, причем прямой выход первого триггера второй группы соединен с входом разрешения передачи блока передачи кода, а прямые вькоды осталных триггеров второй группы подключены к входам шифратора, соединенного выходом с информационным входом регистра, номера канала и входом дешифратора, а выход элемента задержки импульсов записи подключен к единичному установочному входу первого триггера первой группы, а единичный установочный вход каждого i-ro (2

: i п+1) триггера первой группы подключен к первому импульсному выходу (i-l)-ro цифроаналогового интерполятора,

2.Генератор по п. 1, отличающийся тем, что каждый цифроаналоговый интерполятор содержит декодирующую резисторную матрицу, коммутатор, элемент ИЛИ и реверсивный счетчик, счетный вход которого является входом аргумента цифроаналогового интерполятора, выходы признаков переполнения и обнуления реверсивного счетчика под ключены к входам элемента ИЛИ, а кодовый выход - к управляющему входу коммутатора, соединенного информационными входами с выходами декодирующей резисторной матрицы, первый и второй входы которой являются соответственно первым и вторым входами ординат цифроаналогового интерполятора, а выход элемента ИЛИ и выходы признаков обнуления и пере полнения являются соответственно первым, вторым и третьим импульсными выходами цифроаналогового интерполятора.

3.Генератор по п. 1, о т л и чаюгцийся тем, что блок разрешения обмена содержит две группы по (п+1) элементов НЕ и элемент И, выход которого является выходом блока разрешения обмена, инверсный вход элемента И подключен к выходам элементов ЕЕ первой группы, входы кторых являются первой группой входо блока разрешения обмена, а прямой вход элемента И соединен с выходами элементов НЕ второй группы, входы которых являются второй группой входов блока разрешения обмена.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный генератор | 1983 |

|

SU1120364A1 |

| Устройство для двухкоординатного управления рабочим органом | 1990 |

|

SU1815620A1 |

| Функциональный генератор | 1983 |

|

SU1120308A1 |

| Устройство для воспроизведения функций | 1985 |

|

SU1273955A1 |

| Функциональный генератор | 1985 |

|

SU1262533A1 |

| Устройство для программного управления электроприводом | 1985 |

|

SU1260919A1 |

| Имитатор технологического объекта | 1980 |

|

SU924672A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

1. МНОГОКАНАЛЬНЫЙ ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР, содержащий генератор тактовых импульсов, соединенный выходом со счетным входом первого управ ляемого делителя частоты, выход которого подключен к входу аргумента первого цифроаналогового интерполятора, соединенного первым и вторым входами ординат с выходами первого и второго цифроаналоговых преобразователей соответственно, блок памяти и блок управления, содержащий дешифратор и первый счетчик адреса, отличающийся тем, что, с целью повышения точности воспроизведения .функций и расширения частотного диапазона выходных сигналов, в иего дополнительно введены с второго по п-й, где п - количество каналов генератора, управляемые делители частоты, с второго по п-й цифроаналоговые интерполяторы, с третьего по 2п-йцифроаналоговые преобразователи, 2п буферных регистров, шифра тор, блок разрешения обмена, дешифратор номера канала, (n+l) элементов И, (п+1) злементов И-НЕ, (п+1) элементов задержки, две группы по (п+1) триггеров и блок передачи кода, а блок управления дополнительно содержит с второго по п-й счетчики адреса, элемент ИЛИ, элемент задержки импульса записи, регистр номера канала и коммутатор, подключенный информационными входами к выходам счетчиков адреса соответственно, а управляющим входом - к выходу регистра номера канала, соединенного входом разрешения записи с входом элемента задержки импульса записи и выходом элемента ИЛИ, подключенного каждым i-M

1

Изобретение относится к автоматике и вычислительной технике и может найти применение, в частности, при формировании аналоговых управляющих сигналов в многоканальных электрогидравлических системах управления механическим нагружением при испытаниях различных конструкций, например авиационных.

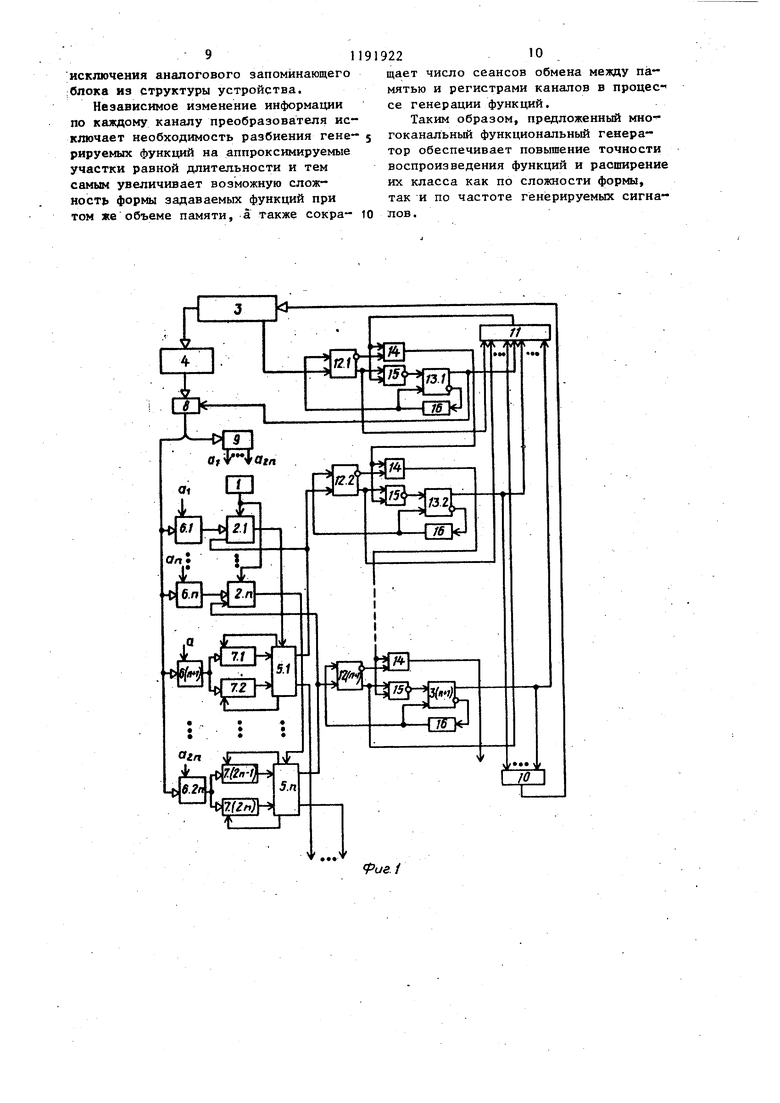

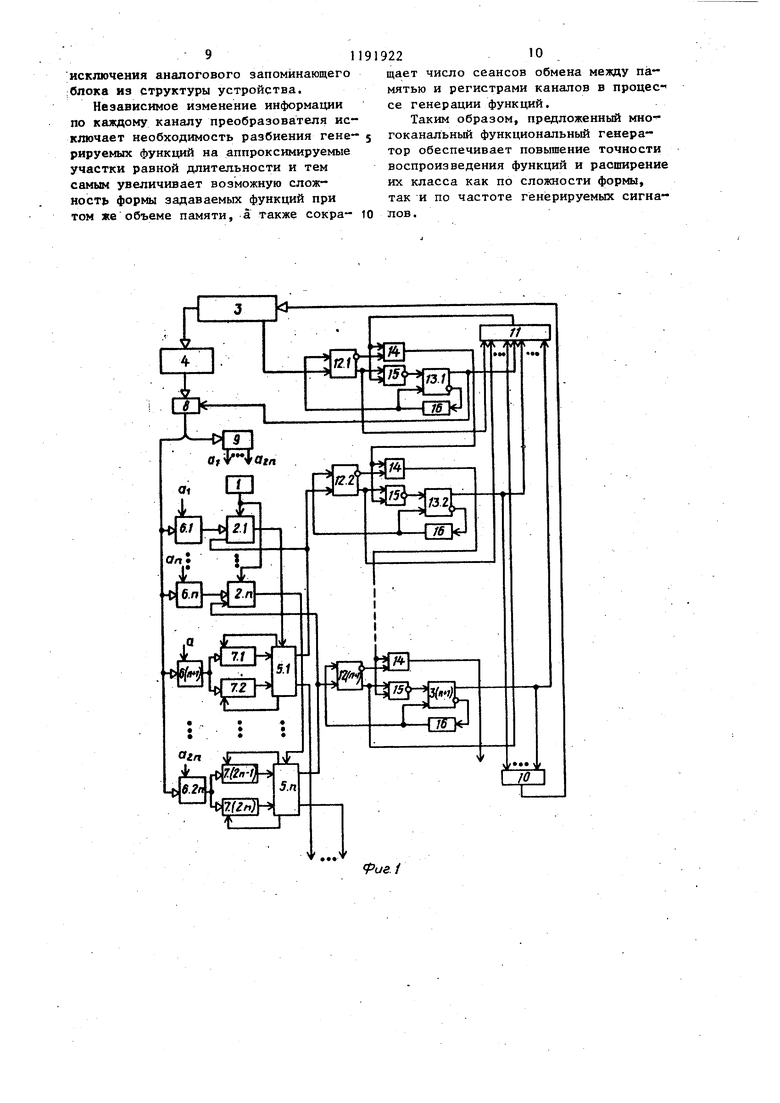

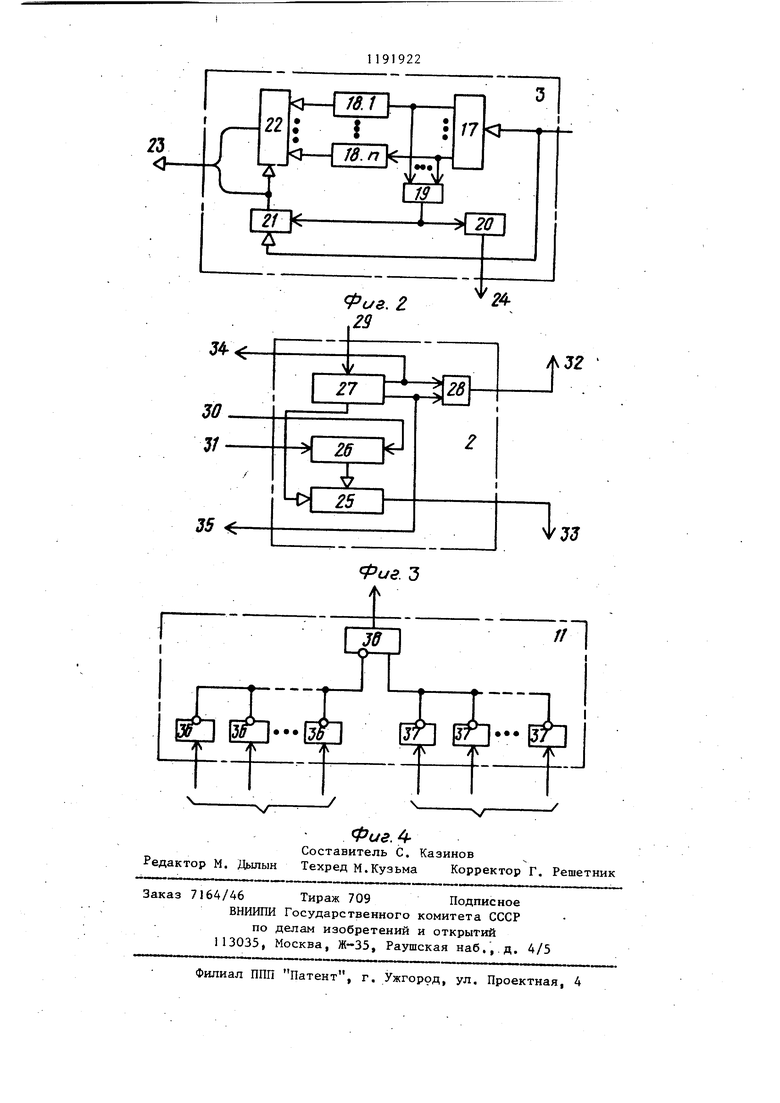

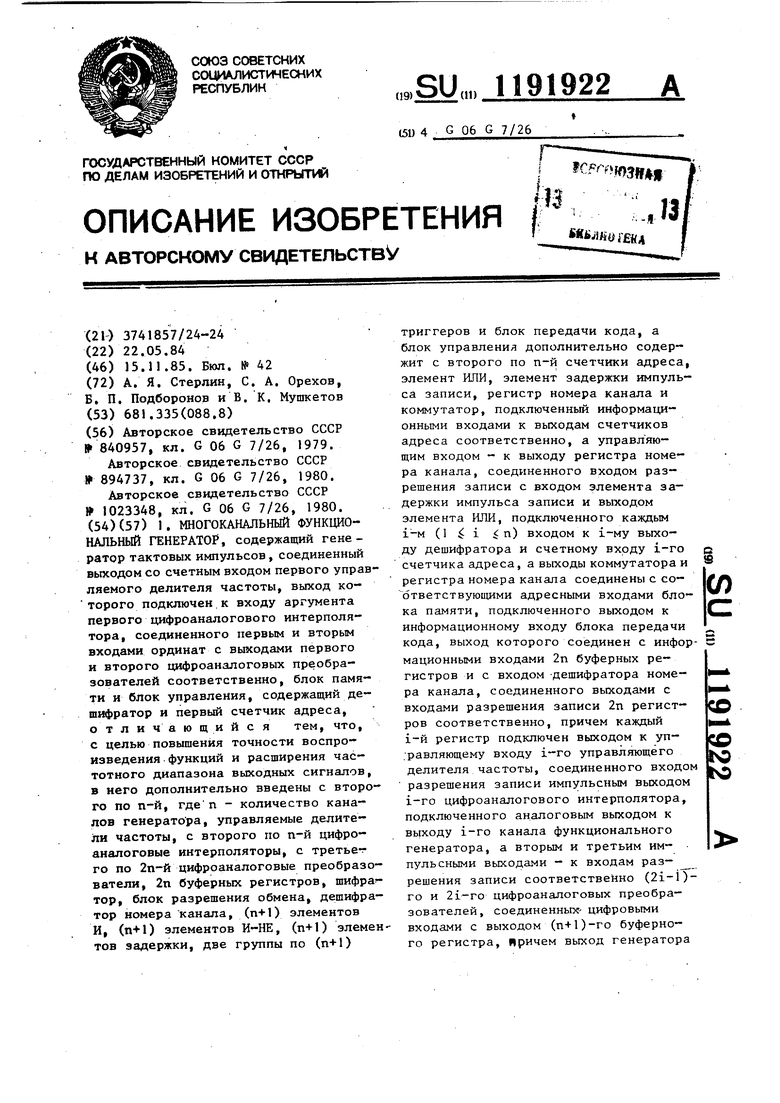

Цель изобретения - повьппение точности воспроизведения функций и расширение частотного диапазона выходных сигналов. 3 На фиг, 1 изображена блок-схема многоканального функционального генератора; на фиг. 2 - схема блока управления; на фиг. 3 - схема цифроаналогового интерполятора; на фиг. 4 схема блока разрешения обмена. Многоканальный функциональный. преобразователь (фиг. 1) содержит генератор 1 тактовых импульсов; п (где п - количество каналов преобразователя) управляемых делителей 2.1,2.2,...,2.п частоты; блок 3 управления; блок 4 памяти; п цифроаналоговых интерполяторов 5.1,...,5п; 2п буферных регистров 6.1, 6.2,... 6(2п), 2п цифроаналоговых преобразователя 7.1, 7.2,...7.(2п); блок 8 передачи кода, дешифратор 9 номера канала; шифратор 10; блок 11 разрешения обмена; триггеры 12.1, 12.2. 12.(n+I) первой группы; триггеры 13.1, 13.2,... ,13.(п+О второй группы; п+1 элементов И 14; п+1 элементов И-НЕ 15 и п+1 элементов 16 задержки. Блок 3 управления(фиг. 2 ) содержи дешифратор 17, п счетчиков 18.1,..., 18.П адреса, элемент ИЛИ 19, элемент 20задержки импульса записи, регистр 21номера канала и коммутатор 22 (на фиг. 2 позициями 23 и 24 обозначены соответственно цифровой и импульсный выходы блока управления }. Каждый цифроанапоговый интерполятор 5 (фиг. 3) содержит коммутатор 25,декодирующую резисторную матрицу 26,реверсивный счетчик 27 и элемент ИЛИ 28 (позициями 29-33 на фиг. 3 обозначены вход аргумента, первый и второй входы ординат, импульсный и аналоговые вьпсоды интерполятора соответственно позициями 34-35 - выход переполнения и обнуления реверсивног счетчика ). Блок 11 разрешения обмена (фиг. 4 содержит первую группу из (п+1) элементов НЕ 36, вторую группу из. (п+.1) элементов НЕ 37 и элемент И 38. ; Каждый из управляемых делителей 2 частоты выполнен на счетчике ирегистре, выход которого подключен к установочному входу счетчика, соединенного входом разрешения установки кода со свим выходом переполнения Цифроаналоговые преобразователи 7 содержат входные регистры для промежуточного хранения данных. Реверсивные счетчики 27 содержат собственно 224 счетчики, дешифраторы-признаков обнуления и переполнения и триггер ре верса. Многоканальный функциональный преобразователь работает следуюш им образом. В исходном состоянии обнулены триггеры 12.1,...,12.(п+1) и ГЗ 1,. .., 13. (п+1) и входные регистры четных цифроаналоговых преобразова телей 7.2, 7.4.,,,; во входные регистры нечетных цифроаналоговых.преобразователей 7.1, 7.3,... занесены коды ординат конечных точек первых участков интерполяции функций каналов преобразования; во входные регистры управляемых делителей 2.1,,,,2п занесены коды длительностей.первых участков интерполяции функций каналов преобразования J в счетчики 18.1,...,18.п блока 3 управления записаны единицы младших разрядов, соответствующие адресам вторых участ ков интерполяции; в регистры 6,1,, ,..,6.п занесены коды длительностей вторых участков интерполяции, а в регистры 6. (ntl),...,6.(2п) - коды ординат конечных точек вторых участков интерполяции. По сигналу Иуск (цепи приведения узлов в исходное состояние и запуска устройства не изображены) включается генератор 1, выходные импульсы которого поступают на счетные входы управляемых делителей 2.1,...,2.п частоты. Импульсы с выходов делителей 2.1, ,..,2.п, частоты следования которых соответствуют кодам длительностей первых участков интерполяции функций, поступают на входы аргументов интерполяторов 5.1,...,5.п, С помощью интерполяторов 5.1,..., 5,п осуществляется кусочно-линейная интерполяция воспроизводимых функций в каналах генератора. Интерполяторы 5.1,...,5.п работают следующим образом. Реверсивные счетчики 27 (фиг. 3) интерполяторов накапливают импульсы с выходов делителей 2.1-, ...,2.п соответственно и формируют линейновозрастающие от нуля до максимума коды развертки первых участков интерполяции по соответствующим каналам. Выходные коды счетчиков 27 поступают на управляющие входы коммутаторов 25 интерполяторов . Каждый из коммутаторов 25 переключает выходы соответст-

вукицей резисторной матрицы 26 таким образом что напряжение на выходе коммутатора изменяется ступенчато от нуля (напряжение на выходе четных цифроаналоговых преобразова телей 7.2, 7.А,,., каналов) до на; пряжения соответствующего коду ординаты конечной точки первого участ ка интерполяции (напряжение на выходе нечетных цифроаналоговых преобразователей 7 . 1 , 7,3,... каналов, При достижении кодом счетчика 27 своего максимального значения сигнал с выхода признака переполнения счетчика переводит его в режим вычитания импульсов, поступает на второй импульсный выход 35 интерполятора и через элемент ИЛИ 28 - на первый импульсный выход 32 интерполятора. По явление сигнала на выходе 32 свидетельствует об окончании отработки первого участка интерполяции воспроизводимой функции.

Предположим, что закончил отработку первого участка интерполятор 5.1. Тогда сигнал с его первого импульсного выхода поступает на единичный установочный вход триггера 12.2 и на вхо, разрешения записи управляемого делителя 2.1. В результате триггер 12.2 устанавливается в единичное состояние, а во входной регистр делителя 2.1 заносится код регистра 6.1, определяющий длительность второго .участка интерполяции. Сигнал с второго импульсного вькода интерполятора 5.1 поступает на вход разрешения записи цифроаналогового преобразователя 7.2, разрешая запись в ег входной регистр кода регистра S.Cn+l) определяющего ординату второго участка. Интерполятор 5.1 начинает отработку второго участка, функционируя аналогично указанному, с той лишь разницей, что происходит уменьшение содержимого счетчика 27 и переключение выходов, матрицы 26 в обратном порядке, В результате напряжение на выходе коммутатора 25 изменяется сту пёнчато от напряжения, соответствующего ординате конечной точки первого участка интерполяции (напряжение на выходе преобразователя 7.1), до напряжения, соответствующего ординате конечной точки второго участка интерполяции (напряжение на выходе преобразователя 7.2). При зтом переход к

отработке следующего участка и реверс счетчика 27 осуществляются в момент обнуления счетчика 27 по сигнал с выхода его признака обнуления.

В процессе отработки второго участка интерполяции функции, воспроизводимой в первом канале преобразователя, обновление информации в регистрах 6.1 и 6.(п+I) происходит следующим образом. Так как в исходном состоянии (до момента записи единицы в триггер 12,1) на прямых выходах триггеров 12.1,...,12.(п+1), 13.1,.. 13.(п+1) были нулевые сигналы, то на выходе блока 11 разрешения обмена также формируется нулевой сигнал, обуславливающий наличие нулевых уровней на выходе элементов 14 и единичных уровней на выходе элементов И-НЕ 15. В результате появления инициирующего сигнала на первом импульсном выходе интерполятора 5.Г триггер 12.2 устанавливается в единичное состояние. Сигнал с прямого выхода триггера поступает на соответствующий вход первой группы входов блока 11 разрешения обмена.

Блок 11 (фиг. 4) работает следующим образом.

В исходном состоянии на входы элементов НЕ 36 и 37 поступают нулевые сигналы, поэтому на прямом и инверсном входах элемента И 38 присутствуют единичные сигналы, обус- лавливайщие наличие нулевого сигнала на выходе блока -11. При подаче на .один из входов первой группы

входов блока 11 единичного сигнала на выходе соответствующего элемента НЕ 36 появляется нулевой уровень. Так как объединение выходов элементов НЕ 36 образует схему МОНТАЖНОЕ И, то на инверсный вход элемента И 38 также начинает поступать нулевой сигнал. В результате н выходе блока 11 появляется единичный сигнал.

Единичный сигнал с выхода блока 11 проходит через первый элемент И 14 (на второй вход которого поступает единичный сигнал с инверсного выхода триггера 12.1) и поступает на первый вход второго элемента ИЧШ 15, на второй вход которого поступает единичный сигнал с прямого выхода триггера 12.2. В результате на выходе второго элемента И-НЕ 15 71 появляется нулевой сигнал, обуславливающий установление триггера 13.2 в единичное состояние (триггеры 13 переключаются отрицательными фронтами импульсов, т.е. переходами сигналов от единичных уровней к нулевым). По истечении времени, определяемогр элементом 16 задержки, триггеры 12.2 и 13.2 возвращаются в исходное нулевое состояние. Сформированный на пря мом выходе триггера 13.2 единичный импульс поступает на один из входов второй группы блока 11 и на соответствующий вход шифратора 10, Появление единичного сигнала на входе одного из- элементов НЕ 37, объединение выходов которых образует в блоке 11 вторую схему МОНТАЖНОЕ И, вызывает формирование нулевого сигнала на прямом входе элемента И 38 и обнуление сигнала на выходе блока 11. Выходной сигнал шифратора 10, предетавлякщий собой код номера кана ла преобразователя, в котором закончипась отработка текущего участка интерполяции, поступает на вход блока 3 управления (фиг. 2). Дешифратор 17 преобразует входной сигнал в еди ничный импульс, поступающий на один из входов элемента ИПИ 19 и на счет ный вход счетчика 18.1 адреса первого канала Выходной сигнал элемента ШШ 19 разрешает запись в регистр .21 кода номера канала и поступает на вход элемента задержки 20. Выходной код регистра 21 устанавливает коммутатор 22 в такое положение, при кото ром к выходу коммутатора 22 подключаются выходы разрядов счетчика 18.1 На выходе 23 блока 3 управления фор мируется код обращения к блоку 4 памяти, старшие разряды которого onpt деляют.номер канала преобразователя, а младшие разряды определяют номер нового участка интерполяции (в рас- сматриваемом случае - третьего участ ка) . На выходе блока 4 памяти выра- батьшается код, соответствующие част разрядов которого определяют значени длительности третьего участка,ордина ты его конечной точки и номера реги стров, в которые эта информация долж на быть занесена (в качестве блоков 3 и 4 может быть использован микропр цессор ). Импульс с выхода элемента 20 задержки устанавливает триггер 12.1 в единичное состояние. Единичный сиг22Sнал с прямого выхода триггера 12.1, поступает на второй вход первого элемента И-НЕ 15 и вход блока 11 разрешения обмена. На выходе блока 11 формируется единичный сигнал, поступающий на первый вход элемента И-НЕ 15. Перепадом напряжения с выхода элемента И-НЕ 15 триггер 13.1 устанавливается в единичное состояние. Сигнал с прямого выхода триггера 13.1 поступает на управляющий вход блока 8 передачи кода, разрешая считывание информации с выхода блока 4 памяти в регистры 6.1 и 6.(2п), а также поступает на вторую группу входов блока 11, вызывая появление на выходе блока 11 нулевого сигнала. По истечении времени, определяемого первым элементом 16 задержки, триггеры 12.1 и 13.1 устанавливаются в исходное нулевое состояние. Обновление информации об узловых значениях ординат и длительностях участков интерполяции в регистрах 6.2,...,6.(2п) других каналов преобразователя происходит аналогично указанному. В тех случаях, когда сиг налы об окончании текущего участка интерполяции формируются одновременно на выходах двух или более интерполяторов 5, то обновление информации по каналам преобразователя выполняется последовательно, начиная с каналов, имеющих меньший порядковый номер. Соблюдение очередности обеспечивается тем, что при окончании отработки текущего участка интерполяции в i-M (1 . i и) канале преобразователя и установлении триггера 12.(i+) в единичное состояние нулевой сигнал с инверсного выхода этого триггера запирает (1+1)-й элемент И 14, запрещая прохождение единичного выходного сигнала блока 1I разрешения обмена на вторые входы элементов И-НЕ 15 последующих каналов . Таким образом, введение в состав устройства новых узлов и связей позво.. ляет повысить точность воспроизведения функций, расширить частотный диапазон выходных сигналов за счет независимого задания длительностей участков интерполяции,по отдельным каналам, возможности перехода с воспроизведения одного участка интерполяции к другому участку по ряду каналов генератора одновременно и 91 исключения аналогового запоминающего блока из структуры устройства. Независимое изменение информации по каждому каналу преобразователя исключает необходимость разбиения генерируемых функций на аппроксимируемые участки равной длительности и тем самым увеличивает возможную сложность формы задаваемых функций при том жа объеме памяти, а также сокра2210щает число сеансов обмена между памятью и регистрами каналов в процес се генерации функций. Таким образом, предложенный мно гоканальный функциональный генератор обеспечивает повьппение точности воспроизведения функций и расширение их класса как по сложности формы, так и по частоте генерируемых сигналов.

| Многоканальный функциональныйпРЕОбРАзОВАТЕль | 1979 |

|

SU840957A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1980 |

|

SU894737A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальный функциональный преобразователь | 1980 |

|

SU1023348A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-11-15—Публикация

1984-05-22—Подача