I

Изобретение относится к технике связи, может использоваться при декодировании импульсных сигналов.

Известно декодирующее устройство, содержащее генератор сдвигающих импульсов, выход которого подключен ко входу делителя частоты и к сдвигающим входам первого и второго регистров сдвига, а также первый сумматор по модулю два и последовательно соединенные второй сумматор по модулю два и первый мажоритарный элемент, вцход которого подключен ко входу второго регистра сдвига, выходы разрядов которого подключены к одним входам конъюнкторов, к-другим входам которых подключен выход делителя частоты, а выходы конъюнкторов подключены ко входам второго мажоритарного элемента; при этом вход и выход первого сумматора по модулю два подключены ко входу и выходу первого регистра сдвига 1.

Однако данное устройство имеет невысокую помехоустойчивость.

Цель изобретения - повышение помехоустойчивости схемы.

Для этого в декодирующее устройство, содержащее генератор сдвигающих импульсов, выход которого подключен ко входу делителя частоты и к сдвигающим входам первого и второго регистров сдвига, а также

первый сумматор по модулю два и последовательно соединенные второй сумматор по модулю два и первый мажоритарный элемент, выход которого подключен ко входу второго регистра сдвига, выходы разрядов которого подключены кодним входам конъюнкторов, к другим входам которых подключен выход делителя частоты, а выходы конъюнкторов подключены ко входам второго мажоритарного элемента, причем вход и выход первого сумматора по модулю два подключены ко входу и выходу первого регистра сдвига, введены последовательно соединенные дополнительный сумматор по модулю два, дополнительный регистр сдвига и первый блок ключей, а также второй блок ключей, дополнительный конъюнктор и счетчик, вход которого подключен к сдвигающим входам дополнительного регистра сдвига и к выходу делителя частоты, а выход счетчика подключен ко входу дополнительного

коыьюнкторп и к сдвигающим входам первог,; и F5Toporo б iOKOB ключсй, прнчсм к друп1 входам вт( рого блока ключей подсоедииеШ) выходы разрядов первого peiiunра сдвиг;, а выходы BTOpoio блока ключей, объединенные с соответствующими выходами первого блока ключей, подсоединены соответственно ко входам второго сумматора по модулю два и первого мажоритарного элемента; другой вход дополнительно; о конъюнктора подключен к выходу перпого мажоритарного элемента, а выход дополнительного регистра сдвига подключен к другому входу дополнительного сумматора по модулю два.

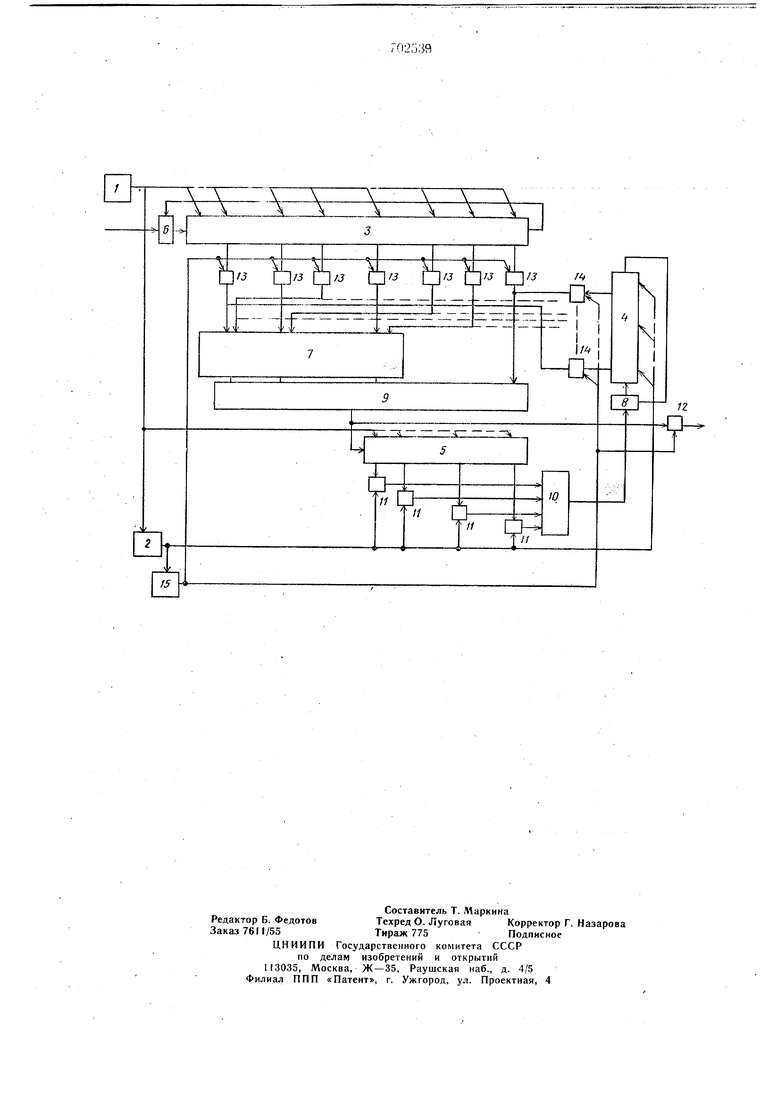

На чертеже изображена структурная электрическая схема предложенного устройства.

.Декодирующее устройство, содержит генератор I сдвигающих импульсов, делитель 2 частоты, регистры 3-5 сдвига, сумматоры 6-8 по модулю два, мажоритарные элементы 9, 10, конъюнкторы И, 12 блоки ключей 13, 14 и счетчик 15.

Устройство работает следующим образом.

Частота сдвигающих импульсов с генератора 1 в К раз превышает входную частоту импульсной последовательносгм,поэтому каждой позиции кодовой комбинации отводится К разрядов регистра 3, счетчик 15 открь1вает блок ключей 13 и запирает блок ключей 14. Сумматор 7 выполняет К проверок Для каждой позиции. Сигнал с мажоритарного .элемента 9 записывается в ретистр 5. Спустя К тактов от начала декодирова.ния в регистр 5 записывается выходной сигнал мажоритарного элемента 9 по первой позиции кода. В это время сигнал с делителя 2 поступает на конъюнктор 11, содержи.мое регистра 5 одновременно приходит на мажоритарный 10 и записывается в первый разряд. Спустя Кп-тактов, где п -- длина кода, в регистр 4 занисьшается комбинация. В это время сигнал со счетчика 15 запирает блок ключей 13 и .открывает блок ключей 14 и конъюнктор 12. Сумматор 7 проверяет кодовую комбинацию, и мажоритарный элемент 9 решает по большинству «1 или «0 соответствие данной позиции, после чего комбинация проходит через конъюнктор 12. Введение новых

rvioKdii значительно повышает помехоустойiii iocTb схемы.

Формула изобретения

Декодирующее устройстве, содержащее генератор сдвигающих импульсов, выход которого нодк.т-очен KCI делителя, часто ты и к сдвигающим входам первого и второго регисгров сллша, а также первый сум.матор по модулю два и последовательно соединенные второй сумматор по модулю два и первый мажоритарн,1Й э.лемент, выход которого нодключен ко входу второго регистра

сдвига, выход,. разрядов которого ПОДКЛ Очены к одним входам конъюнкторов, к другим входам которых нодключен выход делителя частоты, а выходы конъюн торов подключены ко входам второго мажоритарного элемента, при этом входи выход первого сумматора по 1Одул О два подключе 1ы ко пходу и к выходу первого регистра сдвига, отличающееся тем, что, с целью повышения помехоустойчивости декодирования информации, в схему введены последовательно соединённые дополнительный сумматор по модулю два, дог олнительнь1Й регистр сдвига иг первый 6vTOK ключей, а также второй блок , дополнительный конъюнктор и счетчик, вход которого подключен к сдвигающим входам дополнительного регистра сдвига и к выходу делителя частоты, а выход счетчика подключен ко входу дополнительного конъюнктора и к сдвигающим входам первого и второго блоков ключей, причем к другим входам второго блока ключей подсоединены выходы разрядов первого регистра сдвига, а вы.ходы второго блока ключей, объединенные с соответствующими выходами нервого блока лючей, подсоединены соотS ветственно ко входам второго сумматора по .модулю два и нервого мажоритарного элемента, при этом другой вход дополнительного конъюнктора подключен к выходу первого мажоритарного элемента, а выход дополнительного регистра сдвига подключен к другому входу дополнительного сумматора но модулю два.

Источники и 1формации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР

S № 559388, кл. Н 03 К 13/258, 1976 (прототип). Л ....-IA: к/5 п п/Гп т,тXт J- ГГ1 I TI I rzni: ,--..-I- -I г УТЛ J

ч

i

1

ю

i СИ

// I - 3 - о -- I Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство циклического кода | 1978 |

|

SU758514A1 |

| Устройство декодирования импульсной последовательности | 1976 |

|

SU559388A1 |

| Декодирующее устройство | 1984 |

|

SU1251340A2 |

| Декодирующее устройство @ -разрядного кода | 1985 |

|

SU1444963A1 |

| Устройство декодирования импульсной последовательности | 1977 |

|

SU680169A2 |

| Устройство для декодирования модулярного кода | 1987 |

|

SU1411980A1 |

| Устройство декодирования импульсной последовательности | 1979 |

|

SU860308A2 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

Авторы

Даты

1979-12-05—Публикация

1978-04-03—Подача