Изобретение относится к вычислительной технике, может использоваться в системах передачи цифровых данных и является усовершенствованием устройства но авт. св. № 702539.

Цель изобретения - повышение по.мехо- устойчивости декодирования.

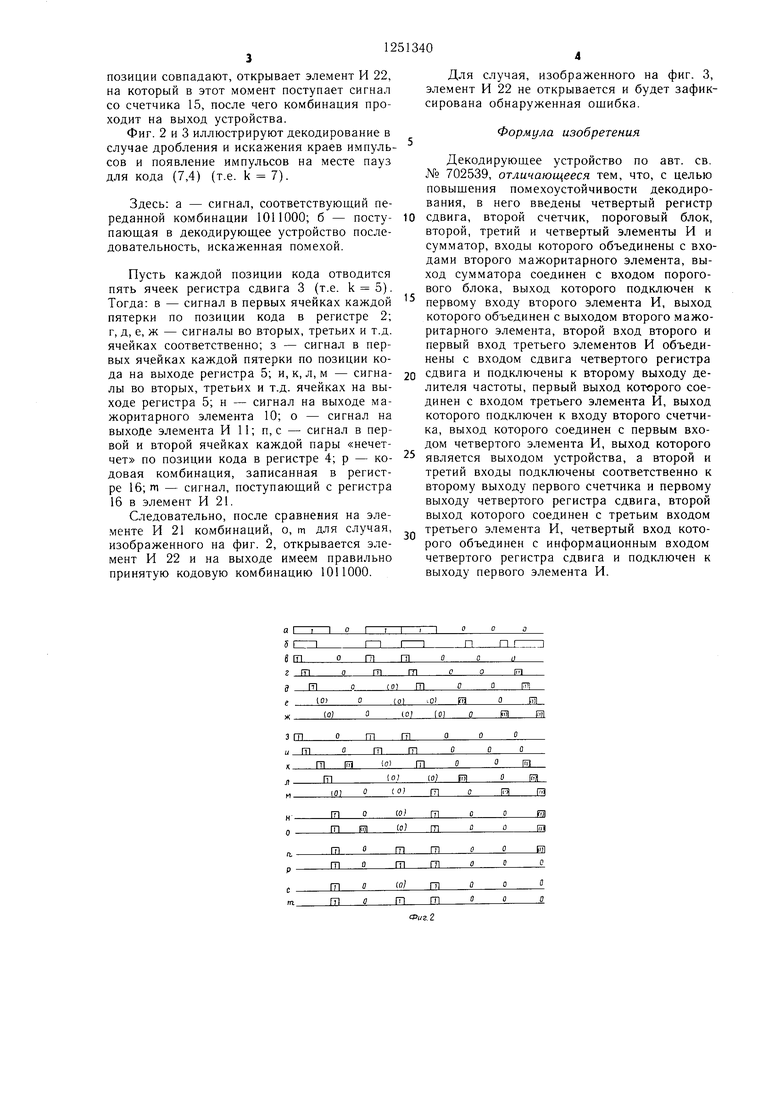

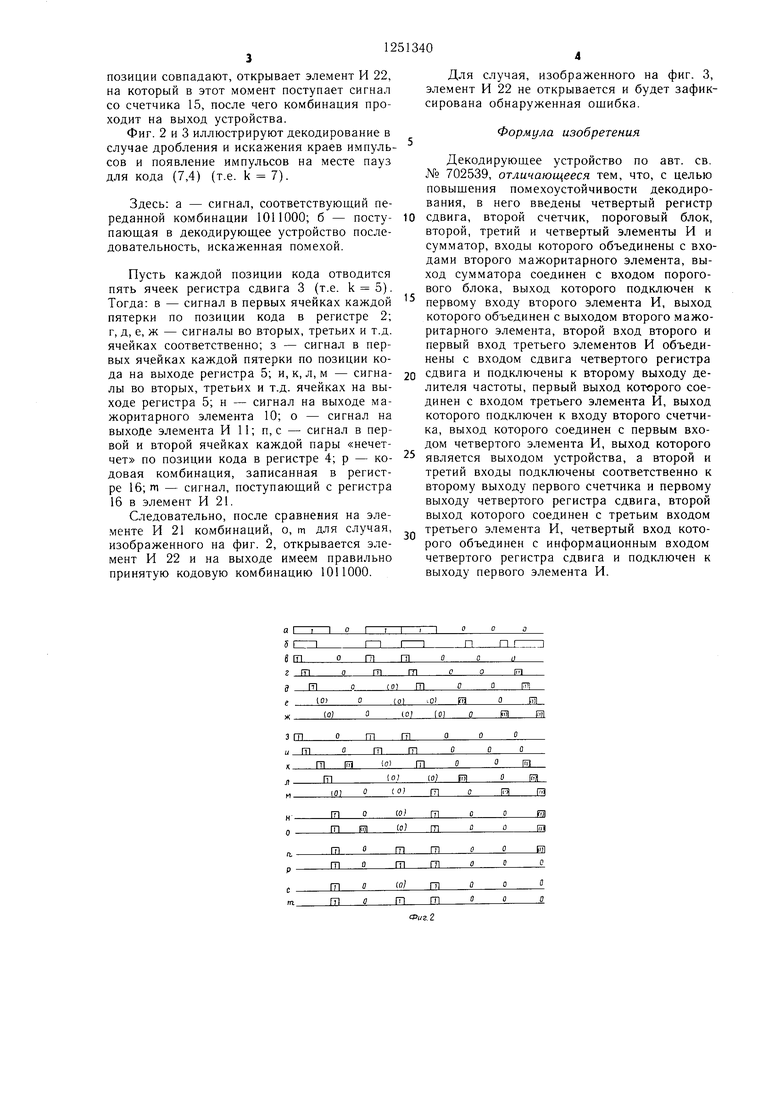

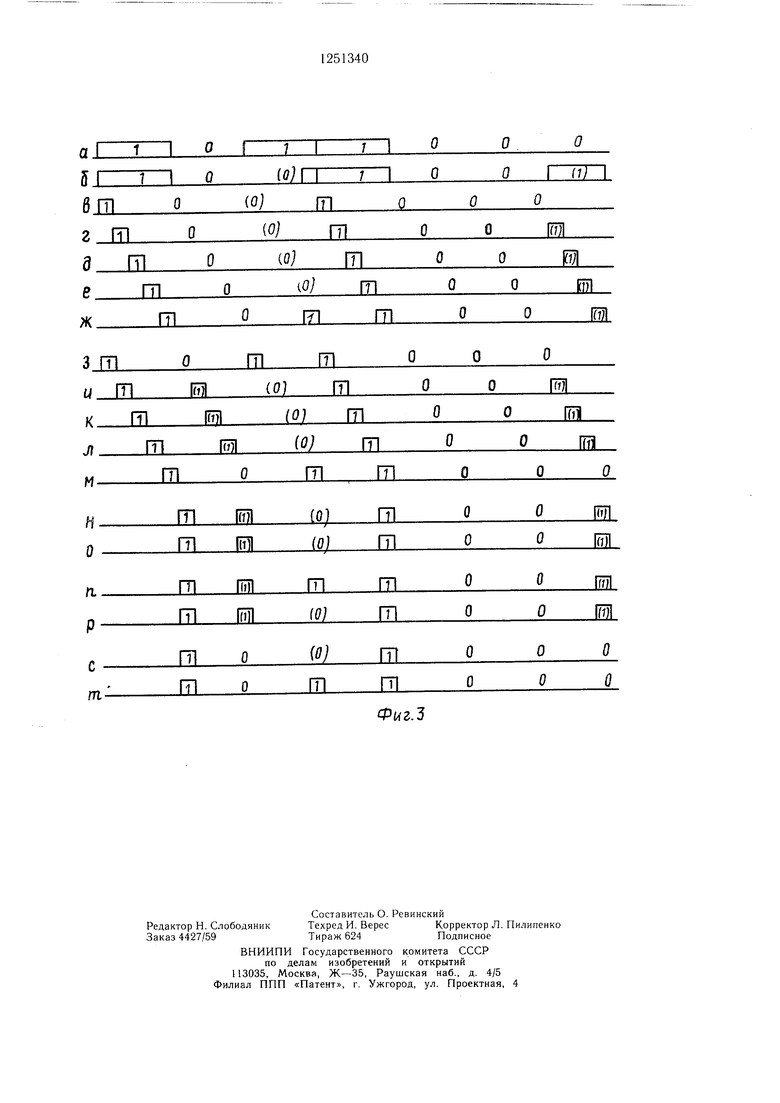

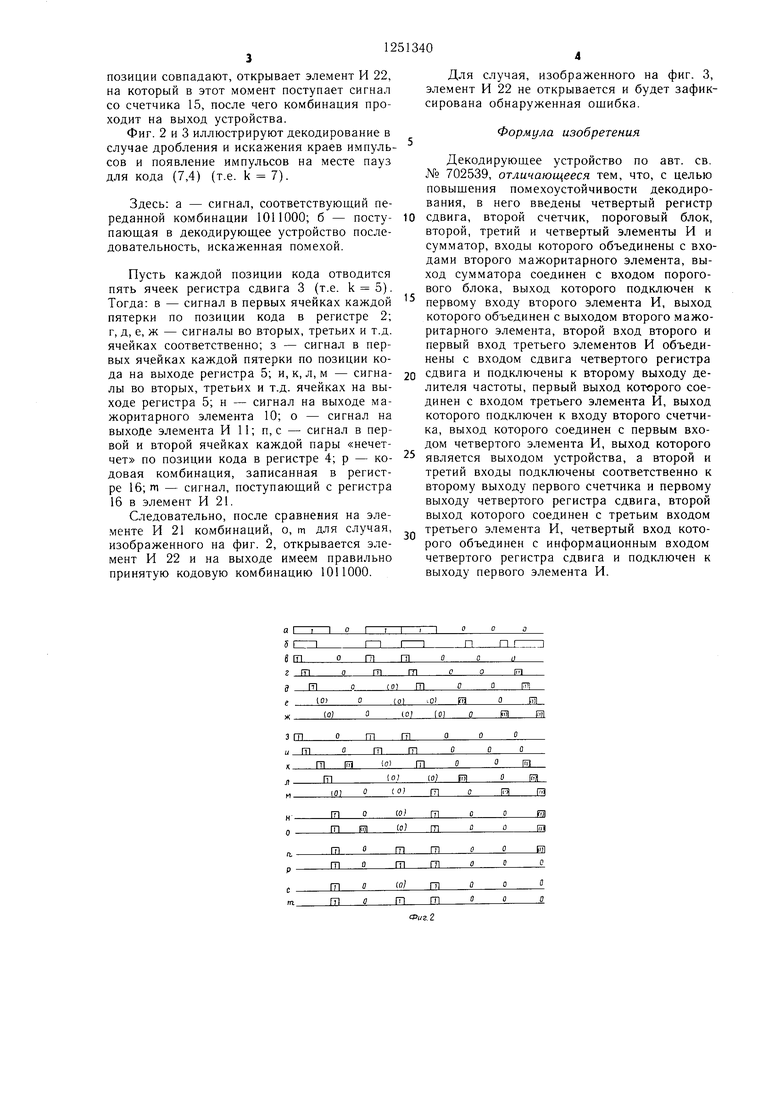

На фиг. 1 приведена функциональная схема декодирующего устройства; на фиг. 2, 3 - функцио1шрование устройства при наличии по.мехи для кода {7, 4).

Декодирующее устройство содержит генератор 1 двигающих и.мпульсов, делитель 2 частоты, первый-третий регистры 3-5 сдвига, первый--третий сумматоры 6-В по модулю два, первый и второй мажоритарные элементы 9, 10, первый элемент И 11, первый-третий блоки 12-14 элементов И и первый счетчик 15, а также четвертый регистр 16 сдвига, второй счетчик 17, сумматор 18, пороговый блок 19, второй-четвертый элементы И 20-22. Первый вход первого сумматора 6 по .модулю два является входом устройства, второй вход подключен к выходу первого регистра 3 сдвига, информационный вход которого соединен с выходом первого сум.матора 6 по модулю два, а вход сдвига соединен с выходом генератора 1, подключенный также к входу сдвига третьего регистра 5 сдвига и входу делителя 2 частоты. Выходы разрядов первого 3 и второго 4 регистров сдвига подключены к пер10

рого элемента И 20, выход которого объединен с выходом второго .мажоритарного элемента 10. Второй вход второго и первый вход третьего эле.ментов И 20, 21 объединены с входом сдвига четвертого регистра 16 сдвига и подключены к второму выходу делителя 2 частоты, первый выход которого соединен с вторым входом третьего элемента И 21. Выход последнего подключен к входу второго счетчика 17, выход которого соединен с первым входом четвертого элемента И 22, выход которого является выходом устройства, второй и третий входы элемента И 22 подключены соответственно к второму выходу первого счетчика 15 и первому выходу четвертого регистра 16 сдвига, второй выход которого соединен с третьим входом третьего элемента И 21, четвертый вход которого объединен с информационным входом четвертого регистра 16 сдвига и подключен к выходу первого элемента И 11.

Делитель 2 частоты по второму выходу и.меет в 1,5 раза больший коэффициент деления, чем по первому.

Устройство работает следующим образом.

Частота сдвигающих импульсов с генера- тора 1 в k раз превышает входную частоту импульсной последовательности, поэтому каждой позиции кодовой комбинации отводится k .разрядов регистра 3, счетчик 15 открывает блок 12 и запирает блок 13.

15

20

вым входам соответствующих блоков 12 и 13 Q Сумматор 7 выполняет k ripoeepoK для каж- элементов И, вторые входы которых объеди- дои позиции. Сигнал с мажоритарного элемента 9 записывается в регистр 5. Спустя k тактов от начала д,екодирования в регистр 5 записывается выходной сигнал .мажоритарного элемента 9 по первой позиции кода.

которого вместе с последними выходами бло-35 это время сигнал с делителя 2 частоты по- ков 12 и 13 соединены с входами первого ступает на блок 14, содержимое регистра 5

нены и подключены к первому выходу первого счетчика 15. Выходы блоков 12 и 13 подключены к соответствующим входам второго сумматора 7 по модулю два, выходы

мажоритарного элемента 9, выход последне го подключен к информационному входу второго регистра 5 сдвига и нервому входу первого элемента И 11, второй вход которого подключен к перво.му выходу первого счетчика 15. Выходы разрядов третьего регистра 5 сдвига соединены с первыми входами третьего блока 4 элементов И, вторые входы которого объединены с входом сдвига второго регистра 4 сдвига и входом первого счетчика 15 и подключены к первому выходу делителя 2 частоты, выходы третьего блока 14 элементов И соединены с входами второго мажоритарного элемента 10, выход которого подключен к первому входу треть50

одновременно приходит на .мажоритарный элемент 10. Если на его входах единиц больше или равно 40 гистр 4 сдвига записывается

числу -1 +

J, то в ре. При каждом нечетном поступлении сигнала на блок 14 поступает сигнал на эле.мент И 20, который открывается если на входе су.м.матора

18

единица оольше или равна числу

fi-Li

I 2. J

45

его сумматора 8 по .модулю два, выход которого соединен с информационным входом второго регистра 4 сдвига, выход которого подключен к второму входу третьего сум.ма- 8 по модулю два. Кроме того, входы второго мажоритарного элемента И) объединены с входами сумматора 18, которого подключен к входу порогового блока 19, выход которого соединен с первы.м входом втои в регистр 4 сдвига записывается вторая позиция первого разряда. Спустя k-n тактов, где п - длина кода, в регистр 4 записывается вся комбинация. В это время сигнал со счетчика 15 запирает блок 12 и открывает блок 13 и элемент И 11. Сумматор 7 проверяет кодовую комбинацию, а мажоритарный элемент 9 решает по большинству единиц или нулей соответствие данной позиции. После этого нечетная позиция проходит через элемент И 11 в регистр 6, а каждая четная 55 на элемент 21, в которых происходит сравнение нечетной позиции с четной. Счетчик 17 подсчитывает число совпадений и, если все

рого элемента И 20, выход которого объединен с выходом второго .мажоритарного элемента 10. Второй вход второго и первый вход третьего эле.ментов И 20, 21 объединены с входом сдвига четвертого регистра 16 сдвига и подключены к второму выходу делителя 2 частоты, первый выход которого соединен с вторым входом третьего элемента И 21. Выход последнего подключен к входу второго счетчика 17, выход которого соединен с первым входом четвертого элемента И 22, выход которого является выходом устройства, второй и третий входы элемента И 22 подключены соответственно к второму выходу первого счетчика 15 и первому выходу четвертого регистра 16 сдвига, второй выход которого соединен с третьим входом третьего элемента И 21, четвертый вход которого объединен с информационным входом четвертого регистра 16 сдвига и подключен к выходу первого элемента И 11.

Делитель 2 частоты по второму выходу и.меет в 1,5 раза больший коэффициент деления, чем по первому.

Устройство работает следующим образом.

Частота сдвигающих импульсов с генера- тора 1 в k раз превышает входную частоту импульсной последовательности, поэтому каждой позиции кодовой комбинации отводится k .разрядов регистра 3, счетчик 15 открывает блок 12 и запирает блок 13.

одновременно приходит на .мажоритарный элемент 10. Если на его входах единиц больше или равно 0 гистр 4 сдвига записывается

числу -1 +

J, то в ре. При каждом нечетном поступлении сигнала на блок 14 поступает сигнал на эле.мент И 20, который открывается если на входе су.м.матора

18

единица оольше или равна числу

fi-Li

I 2. J

и в регистр 4 сдвига записывается вторая позиция первого разряда. Спустя k-n тактов, где п - длина кода, в регистр 4 записывается вся комбинация. В это время сигнал со счетчика 15 запирает блок 12 и открывает блок 13 и элемент И 11. Сумматор 7 проверяет кодовую комбинацию, а мажоритарный элемент 9 решает по большинству единиц или нулей соответствие данной позиции. После этого нечетная позиция проходит через элемент И 11 в регистр 6, а каждая четная на элемент 21, в которых происходит сравнение нечетной позиции с четной. Счетчик 17 подсчитывает число совпадений и, если все

позиции совпадают, открывает элемент И 22, на который в этот момент поступает сигнал со счетчика 15, после чего комбинация проходит на выход устройства.

Фиг. 2 и 3 иллюстрируют декодирование в случае дробления и искажения краев импуль сов и появление импульсов на месте пауз для кода (7,4) (т.е. k 7).

Здесь: а - сигнал, соответствующий переданной комбинации 1011000; б - посту- пающая в декодирующее устройство последовательность, искаженная помехой.

Пусть каждой позиции кода отводится пять ячеек регистра сдвига 3 (т.е. k 5). Тогда: в - сигнал в первых ячейках каждой пятерки по позиции кода в регистре 2; г, д, е, ж - сигналы во вторых, третьих и т.д. ячейках соответственно; з - сигнал в первых ячейках каждой пятерки по позиции кода на выходе регистра 5; и, к, л, м - сигналы во вторых, третьих и т.д. ячейках на выходе регистра 5; н - сигнал на выходе мажоритарного элемента 10; о - сигнал на выходе элемента И 11; п, с - сигнал в первой и второй ячейках каждой пары «нечет- чет по позиции кода в регистре 4; р - кодовая комбинация, записанная в регистре 16; m - сигнал, поступающий с регистра 16 в элемент И 21.

Следовательно, после сравнения на эле- .менте И 21 комбинаций, о, m для случая, изображенного на фиг. 2, открывается элемент И 22 и на выходе имеем правильно принятую кодовую комбинацию 1011000.

3 m

m

-ШJR. ..liL

0

5

Для случая, изображенного на фиг. 3, элемент И 22 не открывается и будет зафиксирована обнаруженная ошибка.

Формула изобретения

Декодирующее устройство по авт. св. № 702539, отличающееся тем, что, с целью повышения помехоустойчивости декодирования, в него введены четвертый регистр сдвига, второй счетчик, пороговый блок, второй, третий и четвертый элементы И и сумматор, входы которого объединены с входами второго мажоритарного элемента, выход сумматора соединен с входом порогового блока, выход которого подключен к первому входу второго элемента И, выход которого объединен с выходом второго мажоритарного элемента, второй вход второго и первый вход третьего элементов И объединены с входом сдвига четвертого регистра сдвига и подключены к второму выходу делителя частоты, первый выход которого соединен с входом третьего элемента И, выход которого подключен к входу второго счетчика, выход которого соединен с первым входом четвертого элемента И, выход которого

5 является выходом устройства, а второй и третий входы подключены соответственно к второму выходу первого счетчика и первому выходу четвертого регистра сдвига, второй выход которого соединен с третьим входом

Q третьего элемента И, четвертый вход которого объединен с информационным входом четвертого регистра сдвига и подключен к выходу первого элемента И.

0

JH

ja

m JJL

JOL JIL

Ш1

Составитель О. Ревинский

Техред И. ВересКорректор Л. Пилипенко

Тираж 624Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| Декодирующее устройство | 1978 |

|

SU702539A1 |

| Устройство для декодирования модулярного кода | 1987 |

|

SU1411980A1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1981 |

|

SU1005151A2 |

| Декодер | 1979 |

|

SU860330A1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

| Устройство декодирования импульсной последовательности | 1979 |

|

SU860308A2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2009 |

|

RU2450465C2 |

| Устройство для кодирования цифровой информации циклическими кодами | 1986 |

|

SU1336255A1 |

Изобретение является дополнительным к авторскому свидетельству № 702539 и при применении в цифровых системах передачи информации позволяет повысить помехоустойчивость декодирования. Устройство содержит генератор 1 сдвигающих импульсов, делитель 2 частоты, три регистра 3, 4, 5 сдвига, три сумматора 6, 7, 8 по модулю два, два мажоритарных элемента 9, 10, первый элемент 11 И, три блока 12, 13, 14 элементов И и первый счетчик 15. Благодаря введению четвертого регистра 16 сдвига, второго счетчика 17, сумматора 18, порогового блока 19 и трех элементов 20, 21, 22 И появляется возможность исправлять ошибки за счет дробления и искажения краев сигнальных импульсов и появления импульсов на месте сигнальных пауз. 3 ил. S (Л 1чЭ 01 ОЭ 4 ФмгЛ ГО

| Декодирующее устройство | 1978 |

|

SU702539A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-08-15—Публикация

1984-12-29—Подача