f

Изобретение относится к области импульсной техники и может использоваться при декодировании импульсных сигналов.

Известны декодирующие устройства полных групповых и укороченных кодов, основанных на умножении или делении принятых двоичных последователей на порождающий полином 1.

Недостатком этих устройств является низкая помехоустойчивость в рамках корректирующей способности кода.

Известно декодирующее устройство, содержащее первый регистр сдвига, состоящий из К-разрядов, второй и третий регистры сдвига, каждый из которых состоит из К-групп по К-разрядов в каждой, четыре сумматора по модулю два, два инвертора, дизъюнктор и генератор сдвигающих импульсов, выход которого соединен с синхронизирующими входами всех разрядов всех трех регистров сдвига, шина входного сигнала соединена со входом первого сдвигающего регистра и с первым входом первого сумматора, второй вход которого соединен с выходом старшего разряда полярной ячейки второго регистра сдвига и с пер ым входом второго сумматора по модулю два, второй вход которого соединен с выходом стариего разряда первой группы второго регистра, выход первого сумматора по модулю два соединен со входом первого разряда первой группы второго регистра сдвига, выход второго сумматора по модулю два соединен с первым разрядом второй группы второго регистра сдвига,

10 вторая и последующие ячейки второго регистра сдвига соединены последовательно, выход первого регистра соединен с первым входом третьего сумматора по модулю два, вход третьего

15 регистра соединен с выходом третьего регистра и с первьи л входом четвертого сумматора по модулю два, второй вход которого соединен с выходом старшего разряда первой группы тре20тьего регистра сдвига, выход четвертого сумматора по модулю два соединен с первым разрядом второй группы третьего регистра сдвига, вторая и последующие группы третьего регист25ра сдвига соединены последовательно, выходы всех разрядов второго регистра соединенных с информационными входами соответствующих разрядов третьего регистра, выходы первых разрядов 30 второй и последующих групп третьего

регистра соединены с соответствуйщими К-I-Bходами диэъюнктора, йьдходпервого разряда первой ячейки третьего регистра соединен через первый инвертор с первым входом дизъюнктора выход которого соединен через второй инвертор со вторым входом третьего сумматора по модулю два 2J,

Недостатком известного устройства является низкая помехоустойчивост обусловленная тем, что при передаче информации по зашумленным каналам связи вследствие воздействия импульсов помехи возникают искажения в полезном сигнале в виде дроблений, исj aжeний краев , появления импульсов на месте пауз , происходит -регистрация сигнала в декодирующем устройстве без учета временных параметров импульсов, ухудшаются характеристики помехоустойчивости.

Целью изобретения является повышение помехоустойчивости передачи информации .i

Поставленная цель достигается teM что в устройство содержащее первый регистр сдвига, состоящий из К-разрядов, второй и третий регистры сдвига, каждый из которых состоит из К-групп по К-разрядов в каждый, четыре сумматора по модулю два, два инвертора, дизъюнктор и генератор сдвигающих импульсов, выход которого соединен с синхронизирующими входами всех разрядов всех трех регистров сдвига,шина входного сигнала соединена со входом первого регистра сдвига и с первым входом первого сумматора, второй вход которого соединен с выходом старшего разряда последней ячейки второго регистра сдвига и с первым входом второго сумматора по модулю два, второй вход которого соединен с выходом старшего разряда первой группы второго регистра, выход первого сумматора по модулю два соединен со входом первого разряда первой группы второго регистра сдвига, выход второго сумматора по модул два соединен с первым разрядом второй группы второго регистра сдвига, вторая и последующие ячейки второго регистра сдвига соединены последовательно, выход первого регистра соединен с первым входом третьего сумматора по модулю два, вход третьего регистра соединен с выходом третьего регистра и с первым входом четвертого сумматора по модулю два, второй вход которого соединен с выходом старшего разряда первой группы третьего регистра сдвига, выход четвертого сумматора по модулю два соединён с первым разрядом второй групп третьего регистра сдвига, вторая и последующие группы третьего регистр сдвига соединены последовательно, выходы всех разрядов второго регистра

соединены с информационными входами соответствующих разрядов третьего регистра, выходы первых разрядов второй и последующих групп третьего регистра соединены с соответствующими К-1-входами дизъюнктора,выход первого разряда первой ячейки третьего регистра соединен через первый инвертор . с первым входом дизъюнктора, выход которого соединен через второй инвертор со вторым входом третьего сумматора по модулю два, введены дополнительно две группы по К-1-инверторов , К-1-дизъюнкторов, К-1-сумматоров по модулю два, К-конъюнкторов, мажоритарный элемент и делитель частоты, причем входы первой группы дополнительных инверторов соединены с выходами в торого и последующих раз расдвига, выходы первой группы дополнительных инверторов соединены с первы ми входами соответствующих дополнительным дизъюнкторов, выходы вторых и последующих разрядов второй и последующих групп третьего регистра сдвига соединены с соответствующими К-1-входами дизъюнкторов, выходы дополнительных дизъюнкторов через инверторы второй дополнительной группы соединены с певыми входами дополнительных сумматоров по модулю два, вторые входо которых соединены соответственно с выходами первой К-1-разрядов первого регистра сдвига, выход третьего сумматора и выходы всех К-1-дополнительны сумматоров соединены с первыми входами соответствующих конъюнкторов, вторые входы которых соединены с выходом делителя частбты, вход которого соединен с выходом генератора сдвгающих импульсов, выходы конъюнкторов соединены с соответствующими входами мажоритарного элемента, выхо которого подключен к выходной щине.

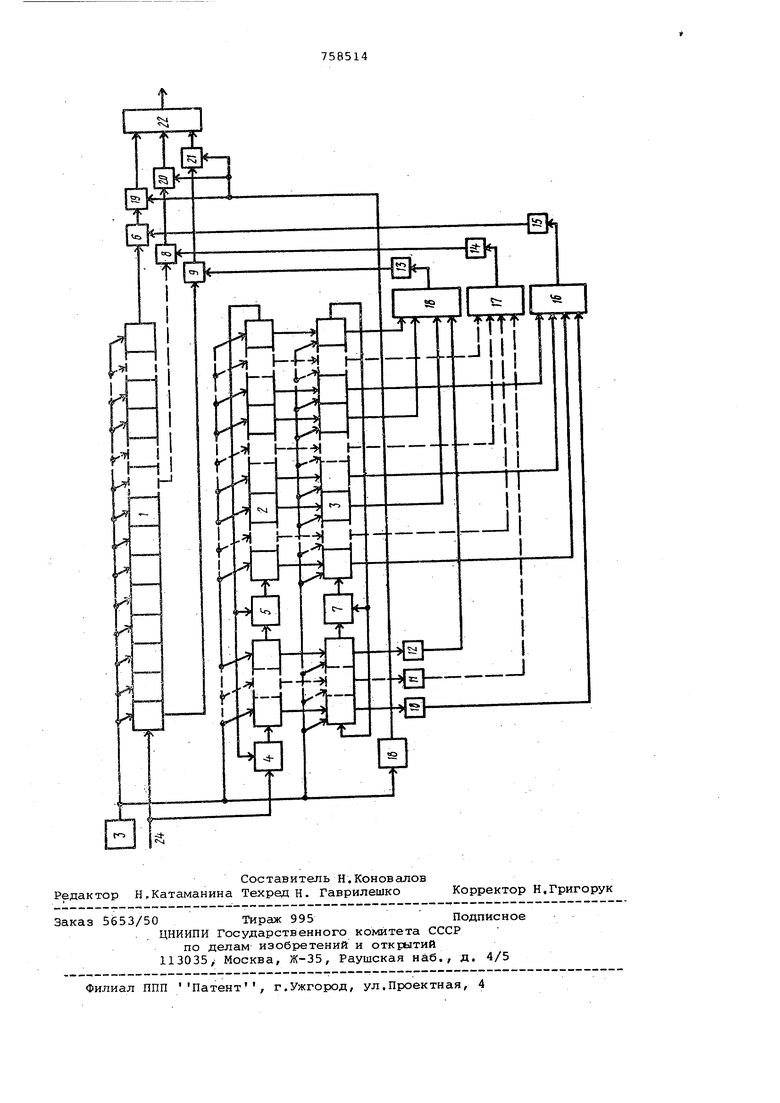

На чертеже представлена блок-схема предлагаемого устройства.

Декодирующее устройство циклического кода содержит регистр 1 сдвига, состоящий из К-разрядов, регистр 2 и 3 сдвига, каждый из которых состоит из К-групп по К-разрядов в каждой, сумматоры по модулю два 4-9, инверторы 10-15, дизъюккторы. 16-18 конъюнкторов 19-21, мажоритарный элемент 22 и генератор сдвигающих импульсов 23, выход которого соединен со всеми синхронизирующими входами всех разрядов регистров 1-3, шина входного сигнала 24 соединена со входом регистра 1 и с первым входом сумматора по модулю два 4, второй вход которого соединен с выходом последнего разряда последней группы регистра 2 и с первым входом сумматора по модулю два 5, второй вход которого соединен с выходом последнего разряда первой группы регистра 2, выход сумматора по модулю два 4 соединен со входом первого разряда пер вой группы регистра 2, выход сумматора по модулю ДВ5 5 соединен с первым разрядом второй группы регистра 2, вторая и последующие группы регистра 2 соединены последовательно, выход регистра 3 соединен с выходом регистра 3 и с nepBbUvi входом сумматора по модулю два 7, второй вход которого соединен с выходом поледнего разряда первой ячейки регист ра 3 , выход сумматора по модулю два 7 соединен с первым разрядом второй группы регистра 3, вторая и последу ющие группы регистра 3 соединены последовательно, выходы всех разрядов регистра 2 соединены с информационны ми входами соответствующих разрядов регистра 3, выход первого разряда первой группы регистра 3 соединен че рез инвертор 10, а выходы первых раз рядов второй и последующих групп регистра 3 соединены непосредственно с соответствующими входами дизъюнктора 16, выход последнего разряда первой группы регистра 3 соединен через инвертор 12, а выходы последних разрядов второй и последующих групп регис ра 3 соединены непосредственно с соответствующими входами дизъюнктора 18 , выход промежуточного разряда пер вой группы регистра 3 соединен через инвертор 11, а выходы промежуточных разрядов второй и последующих групп регистра 3 соединены непосредственно с соответствующими входами дизъюнкто ра 17, выходы дизъюнкторов 16-18 че рез инверторы 13-15 соединены с первыми входами сумматороав по модулю два б, 8 и 9, вторые входы которых соединены с соответствующими разряда ми регистра 1/ выходы сумматоров по модулю два б, В и 9 соединены с пер выми входами конъюнкторов 19, 20 и 21, входы которых соединены с выходом делителя частоты 18, вход которого соединен с генератором сдви гающих импульсов 23, выходы конъюнк торов 19,20, и 21 соединены с соответствующими входами мажоритарного элемента 22, выход которого подклю Чен к выходной шине. Декодирующее устройство цикличес кого кода работает следующим образом. Частота сдвигающих импульсов с г нератора сдвигс1ющих импульсов 22 в К-раз превышает входную частоту импульсной последовательности, поэтому каждому разряду кодовой ко лбинации отводится К-разрядов регистра сдвига 1 и К-групп на кгокдый символ синдрома в регистрах сдвига 2 и 3. Каждая ячейка имеет К групп. Входная последовательность с сохранением в.ременных параметров импульсов и пауз поступает в регистры 1 и 2. Сформировавшиеся в регистре сдвига 2 К-остатков от деления на порождающий полином, за счет обработки всех первых разрядов каждого разряда кода, вторых и до К-тых, параллельно во времени переписываются в регистр сдвига 3, где производится определение мест искажений путем логического сдвига остаткоь от-деления. Содержимое первых разрядов каждойгруппы поступает на дизъюнктор 16 промежуточных и последних разрядов дизъюнкторы 17, 18 сигналы с которых осуществляют коррекцию искажений входной последовательности, поступающей из регистра сдвига 1 в сумматоры по модулю два 6, 8 и 9. Информация из которых считывается сигналом с делителя частоты 18, делящего частоту импульсов на К в мажоритарньй элемент, который определяет по большинству О или соответствие сигналы данной позиции. Таким образом, декодирующее устройство непосредственно корректирует искажения, возникшие в сигнале, без нормирования элементов кода по длительности. Благодаря тому, что сигуал запоминается с сохранением временных параметров импульса,декодирующее устройство оперирует непосредственно с искажениями CHrHaJiOB, что дает возможность получить более высокие характеристики помехоустойчивости. Формула изобретения Декодирующее устройство циклического кода, содержащее первый регистр сдвига, состоящий из К-разрядов, второй и третий регистры сдвига, каждый из которых состоит из К-групп по К-разрядов в каждой, четыре сумматора по модулю два, два инвертора, дизъюнктор и генератор сдвигающих импульсов, выход которого соединен с синхронизирующими входами всех разрядов всех .трех регистров сдвига, шина входного сигнала соединена со входом первого регистра сдвига и с первым входом первого сумматора, второй вход которого соединен с выходом старшего разряда последней ячейки второго регистра сдвига и с первым входом второго сумматора по модулю два, второй вход которого соединен с выходом старшего разряда первой группы второго регистра, выход первого сумматора по модулю два соединен со входом первого разряда первой группы второго регистра сдвига, выход второго сумматора по модулю два соединен с первым разрядом второй группы второго регистра сдвига, вторая и последующие ячейки второго

регистра сдвига соединены последовательно, выход первого регистра соединен с первым входом, третьего сумматора по модулю два,вход тре1;ьего регистра соединен с выходом третьего регистра и с первым входом четвертого сумматора по модулю два, второй вход которого соединен с выходом старшего разряда первой группы третьего регистраСдвига, выход четвертого сумматора по модулю два соединен с первым разрядом второй группы третьего регистра сдвига, вторая и последующие группы ретьего регистра сдвига соединены последовательно, выходы всех разрядов второго регистра соединены с информационными, входами соответствующих разрядов третьего регистра, выходы первых разрядов второй и последующих групп третьего регистра соединены с соответствующими K-i-входами дизъюнктора,выход первого разряда первой ячейки третьего регистра соединен через первый инвертор с первым входом дизъюнктора, выход которого соединен через второй инвертор со вторым входом третьего сумматора модулю два, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены дополнительно две группы по К-1-инвер-роров, К-1-дизъюнкторов, К-1-сумматоров по модулю два, К-конъюнкторов, мажоритарный элемент и делитель частоты, причем ; входы первой группы дополнительных инверторов соединены с

выходами второго и последующих разрядов первой группы третьего регистра сдвига, выходы первой группы дополнительных инверторов соединены с первыми входами соответствующих дополнительным дизъюнкторов, выходы вторых и последующихразрядов второй и последующих групп третьего регистра сдвига соединены с соответствующими К-1-входами соответствующих дополнительных дизъюнктороз, выходы дополнительных дизъюнкторов через инверторы второй дополнительной группы соединены с первыми входами дополнительных сумматоров по модулю два, вторые входы которых соединены соответственно с выходами первой К-1-разрядов первого регистра сдвига, выход третьего сумматора и выходы всех К-1-дополнительных сумматоров соединены с первыми входами соответствующих конъюнкторов, вторые входы которых соединены с выходом делителя частоты, вход которого соединен с выходом генератора сдвигающих импульсов, выходы конъюнкторов соединены с соответствующими входами мажоритарного элемента, выход которого подключен к выходной шине.

Источники информации, принятые во внимание при экспертизе

1.Патерсон У., Уэлдон Э. Коды, исправляющие ошибки. М: Мир, 1976, с.265-273.

2.Берлекэмп Э. Алгебраическая теория кодирования, М;,Мир, 1971, с.132

(прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство декодирования импульсной последовательности | 1977 |

|

SU680169A2 |

| Декодирующее устройство | 1978 |

|

SU702539A1 |

| ГЕНЕРАТОР НЕЛИНЕЙНЫХ ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2014 |

|

RU2549524C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

| Устройство декодирования импульсной последовательности | 1976 |

|

SU559388A1 |

| Декодирующее устройство | 1984 |

|

SU1251340A2 |

| Декодирующее устройство @ -разрядного кода | 1985 |

|

SU1444963A1 |

| Устройство для управления регулируемым мостовым инвертором | 1988 |

|

SU1548830A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЕ-КОД СО СТУПЕНЧАТЫМ ПИЛООБРАЗНЫМ НАПРЯЖЕНИЕМ | 2018 |

|

RU2692426C1 |

Авторы

Даты

1980-08-23—Публикация

1978-05-03—Подача