10

15

1U44963

Изобретение относится к вычис- 1 лительной технике, а именно к уст- ройствам преобразования информации, и Может быть испльзовано при декодировании импульсных сигналов.

Цель изобретения - повышение помехоустойчивости кода.

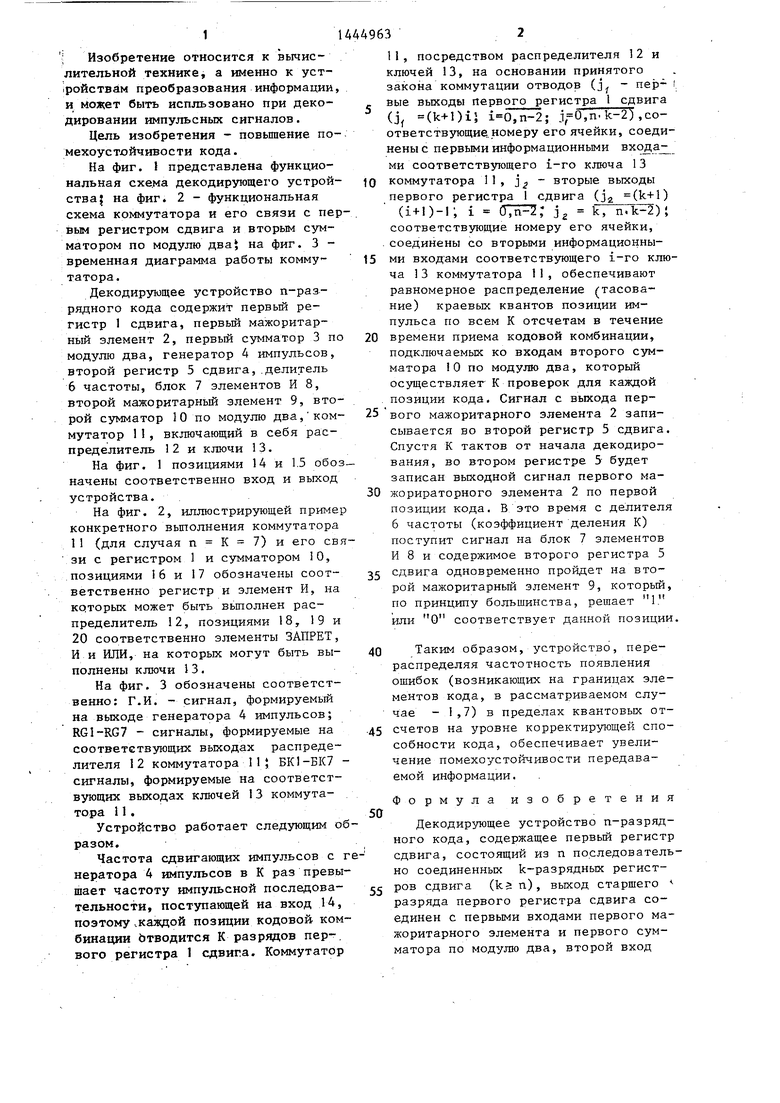

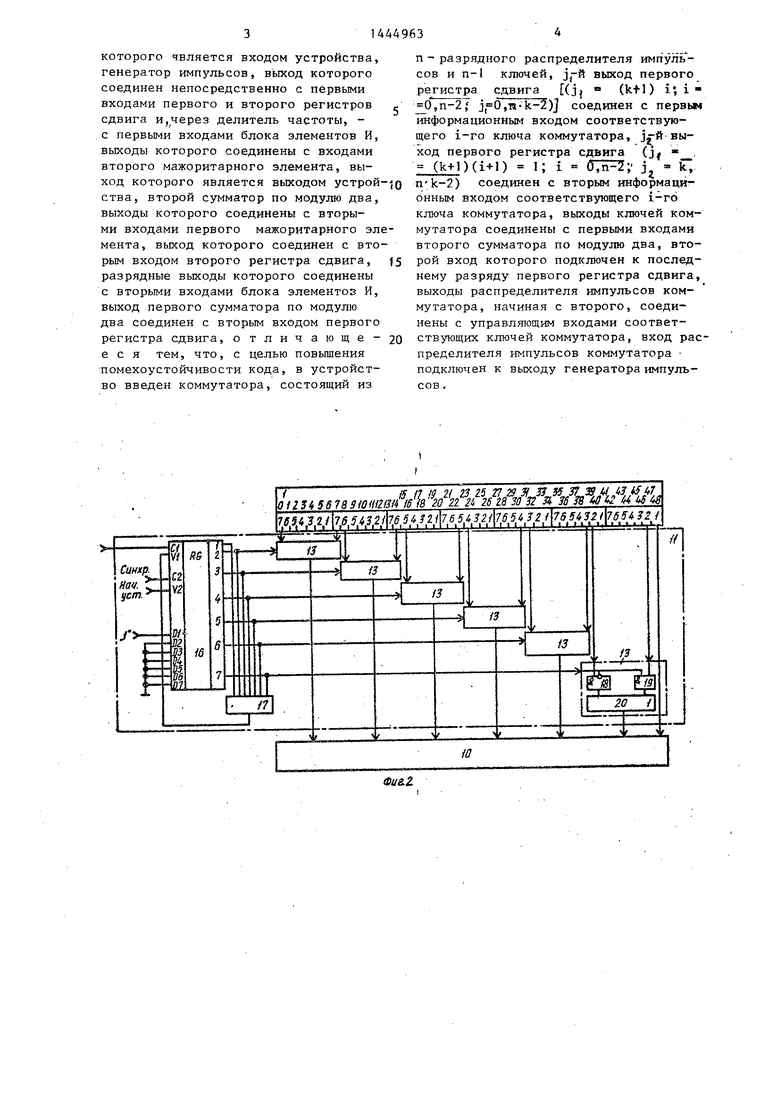

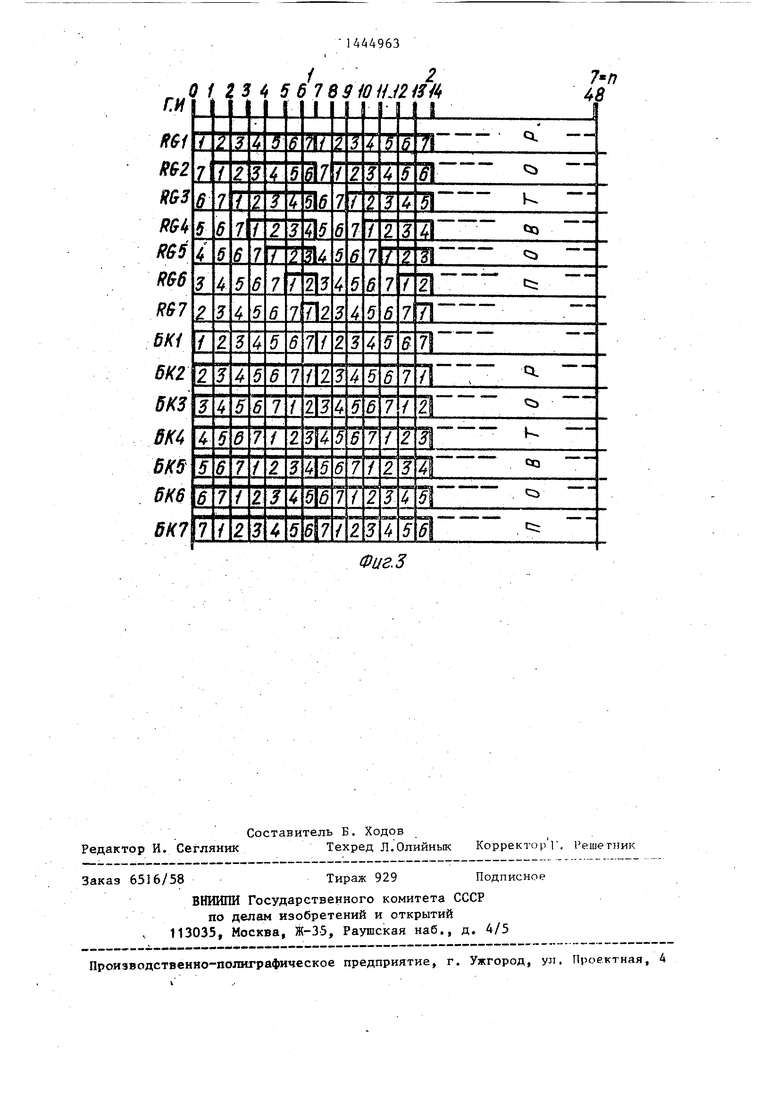

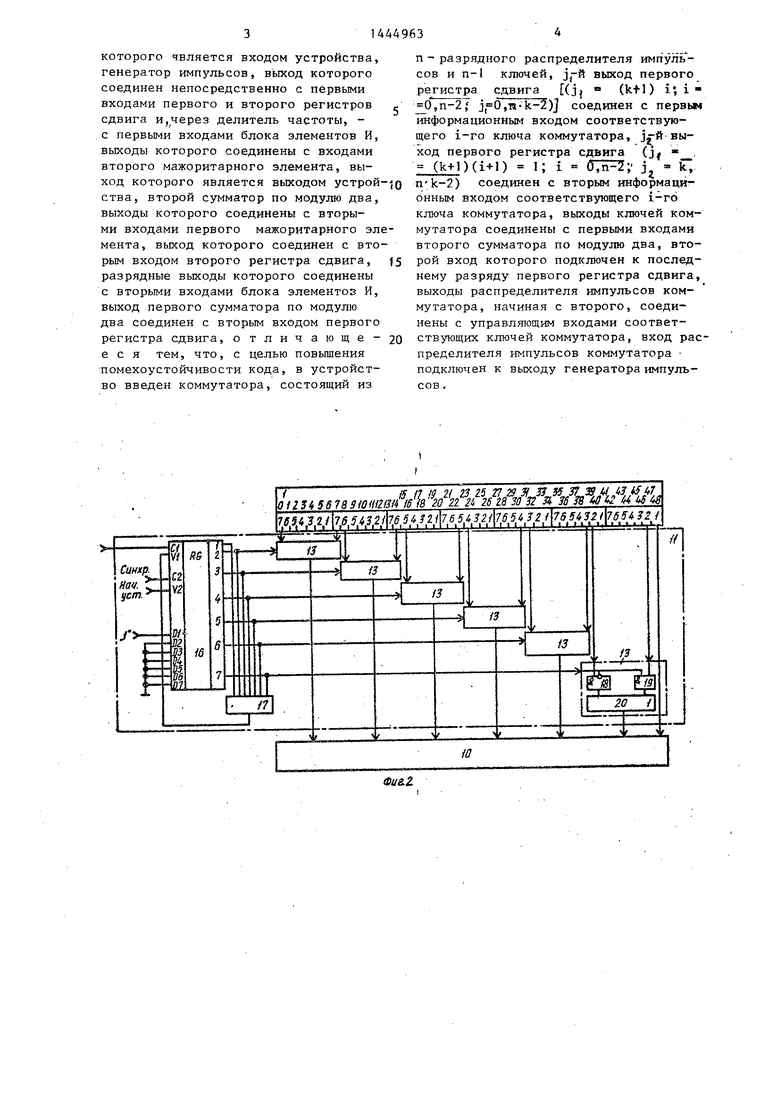

На фиг. I представлена функциональная схема декодирующего устройства фиг. 2 - функциональная схема коммутатора и его связи с первым регистром сдвига и вторьм сумматором по модулю два на фиг. 3 - временная диаграмма работы коммутатора.

Декодирующее устройство п-раз- рядного кода содержит первый регистр 1 сдвига, первый мажоритарный элемент 2, первый сумматор 3 по модулю два, генератор 4 импульсов, второй регистр 5 сдвига,.делитель 6 частоты, блок 7 элементов И 8, второй мажоритарный элемент 9, второй сумматор 10 по модулю два, коммутатор 11, включающий в себя распределитель 12 и ключи 13.

На фиг. 1 позициями 14 и 1.5 обозначены соответственно вход и выход устройства.

На фиг. 2, иллюстрирующей пример конкретного выполнения коммутатора 11 (для случая п К 7) и его свя- зи с регистром 1 и сумматором 10, позициями 16 и 17 обозначены соответственно регистр и элемент И, на которых может быть вьшолнен распределитель 12, позициями 18, 19 и 20 соответственно элементы ЗАПРЕТ, И и ИЛИ, на которых могут быть выполнены ключи 13.

На фиг. 3 обозначены соответственно: Г.И. - сигнал, формируемый на выходе генератора 4 импульсов; RGI-RG7 - сигналы, формируемые на соответствующих выходах распределителя 12 коммутатора 115 - сигналы, формируемые на соответствующих выходах ключей 13 коммутатора 11 .

Устройство работает следующим образом.

Частота сдвигающих импульсов с генератора 4 импульсов в К раз превышает частоту импульсной последовательности, поступающей на вход 14, поэтому каждой позиции кодовой комбинации Ьтводится К разрядов пер-. вого регистра 1 сдвига. Коммутатор

з о

20 в

25 в

30 ж

35

40

45

50

55

ч

0

1

11, посредством распределителя 12 и ключей 13, на основании принятого закона коммутации отводов (j - пер- ( вые выходы первого регистра 1 сдвига (JJ (k+l)ij ,n-2; ,n. k-2) ,со- ответствующие..номеру его ячейки, соединены с первыми информационными входа ми соответствующего i-ro ключа 13 коммутатора 11, j - вторые выходы первого регистра 1 сдвига (j (k+l)

(i+i)-i; i J k, n.k-2);

соответствующие номеру его ячейки, соединены со вторыми информационными входами соответствующего i-ro ключа 13 коммутатора 11, обеспечивают равномерное распределение (тасование) краевых квантов позиции импульса по всем К отсчетам в течение

0 времени приема кодовой комбинации, подключаемых ко входам второго сумматора 10 по модулю два, который осуществляем К проверок для каждой позиции кода. Сигнал с выхода пер5 вого мажоритарного элемента 2 записывается во второй регистр 5 сдвига. Спустя К тактов от начала декодирования, во втором регистре 5 будет записан выходной сигнал первого ма0 жорираторного элемента 2 по первой позиции кода. В это время с делителя 6 частоты (коэффициент деления К) поступит сигнал на блок 7 элементов И 8 и содержимое второго регистра 5 сдвига одновременно пройдет на второй мажоритарный элемент 9, который, по принципу большинства, решает 1. или О соответствует данной позиции.

5

Таким образом, устройство, перераспределяя частотность появления ошибок (возникающих на границах элементов кода, в рассматриваемом случае - 1,7) в пределах квантовых отсчетов на уровне корректирующей способности кода, обеспечивает увеличение помехоустойчивости передаваемой информации.

Формула изобретения

Декодирующее устройство п-разряд- ного кода, содержащее первый регистр сдвига, состоящий из п последовательно соединенных k-разряднык регистров сдвига (ka п), выход старшего разряда первого регистра сдвига соединен с первыми входами первого мажоритарного элемента и первого сумматора по модулю два, второй вход

которого чвляется входом устройства, генератор импульсов, выход которого соединен непосредственно с первыми входами первого и второго регистров сдвига и,через делитель частоты, - с первыми входами блока элементов И, выходы которого соединены с входами второго мажоритарного элемента, выход которого является выходом устройства, второй сумматор по модулю два, выходы которого соединены с вторыми входами первого мажоритарного элемента, выход которого соединен с вторым входом второго регистра сдвига, разрядные выходы которого соединены с вторыми входами блока элементов И, выход первого сумматора по модулю два соединен с вторым входом первого регистра сдвига, отличающееся тем, что, с целью повьшения помехоустойчивости кода, в устройство введен коммутатора, состоящий из

Q

0

п - разрядного распределителя имп уль - сов и п-1 ключей, j-й выход первого сдвига (j, (kfl) i; i- ),n-2, ,n-k-2)j соединен с первые информационным входом соответствующего i-ro ключа коммутатора, jr-й выход первого регистра сдвига (j, « (k-HXi-bl) l; i 07гР2; j Г, n k-2) соединен с вторым информационным входом соответствующего i-г6 ключа коммутатора, выходы ключей коммутатора соединены с первыми входами второго сумматора по модулю два, второй вход которого подключен к последнему разряду первого регистра сдвига, выходы распределителя импульсов коммутатора, начиная с второго, соединены с управляющим входами соответствующих ключей коммутатора, вход распределителя импульсов коммутатора подключен к выходу генератора импульсов .

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1978 |

|

SU702539A1 |

| Декодирующее устройство | 1984 |

|

SU1251340A2 |

| Устройство для декодирования модулярного кода | 1987 |

|

SU1411980A1 |

| Устройство декодирования импульсной последовательности | 1977 |

|

SU680169A2 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ДЛЯ ЦИКЛИЧЕСКИХ | 1970 |

|

SU261460A1 |

| Устройство декодирования импульсной последовательности | 1979 |

|

SU860308A2 |

| Декодирующее устройство циклического кода | 1978 |

|

SU758514A1 |

| Декодер мажоритарных блоковых кодов | 1986 |

|

SU1349011A1 |

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

| Устройство для исправления ошибок в информации, закодированной циклическим кодом | 1974 |

|

SU512589A1 |

Изобретение относится к вычислительной технике, а именно к устройствам преобразования информации. и может быть использовано при декодировании импульсных сигналов.Изоб- ретние позволяет при декодировании ин(5)ормации равномерно распределять краевые кванты позиций импульса по всем К отсчетам в течение времени приема кодовой комбинации, что обеспечивает повьшение помехоустойчи- вости преобразуемого кода. Декодирующее устройство п-разрядного кода содержит два регистра 1 и 5 сдвига, два сумматора 3 и 10 по модулю два, два мажоритарных элемента 2 и 9, генератор 4 импульсов, делитель 6. частоты, блок 7 элементов И Q, коммутатор 1I, содержащий распределитель 12 импульсов и ключи 13, 3 ип. I сл

1

.ЛЛ.г-5.ЛЛ,У,,зз.J..lM,7

U2S4 7а /дш/Г/ 7ажг2 Л д jgjgl;g4 y«J4

.ЛЛ.г-5.ЛЛ,У,,зз.J..lM,7

/ 7ажг2 Л д jgjgl;g4 y«J4

/ 2 О 1 Z3 5 67B9W1L 21S

7-/7

ФцаЗ

| Устройство декодирования импульсной последовательности | 1977 |

|

SU680169A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство декодирования импульсной последовательности | 1976 |

|

SU559388A1 |

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1988-12-15—Публикация

1985-12-19—Подача