Изобретение относится к электротехнике и может быть использовано для управления тиристорно-импульсными преобразователями постоянного тока.

Известны устройства для цифрового управления тиристорно-импульсными преобразователями постоянного тока, содержащие задающий генератор, подключенный к тактовому счетчику, блок управления, суммирующе-вычитающим выходом подключенный к реверсивному счетчику, дешифратор с 2n выходами (где n число триггеров в двоичных счетчиках), которые подключены к 2-n логическим выходам реверсивного счетчика и к 2n логическим выходам тактового счетчика через логические элементы И.

Однако такие устройства содержат завышенное число элементов, характеризуются низкой надежностью, большими габаритами и высокой стоимостью.

Наиболее близким по технической сущности к предложенному является устройство для цифрового управления m-фазным тиристорно-импульсным преобразователем, содержащее тактовые и реверсивные счетчики с n-триггерами, задающий генератор, блок управления, m-дешифраторов, каждый из которых включает в себя 2n логических входа, подключенных к логическим выходам тактового счетчика, 2n логических входа, подключенных к логическим выходам реверсивного счетчика, которые соединены через элементы И с 2n выходами дешифратора.

Однако для таких устройств требуется много элементов, что снижает их надежность, повышает габариты и стоимость.

Целью изобретения является упрощение устройства и расширение области его применения.

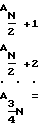

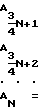

Это достигается тем, что в предложенном устройстве для цифрового управления m-фазным преобразователем, где m четное число фаз, включающем в себя тактовые и реверсивные счетчики с n-триггерами, предназначенные для воздействия на элементы управления, m-дешифраторов, каждый из которых содержит 2n логических входа (n разрядность счетчика), подключенных к логическим выходам тактовых счетчиков, и 2n логических входа, подключенных к 2n логическим выходам реверсивного счетчика, элементы И, выходы (1+  ) каждого дешифратора подключены через элементы И к логическим выходам реверсивного счетчика, другие 2n логических входа первого дешифратора через элементы И подключены к логическим выходам тактового счетчика и соединены через другие элементы И с (1+

) каждого дешифратора подключены через элементы И к логическим выходам реверсивного счетчика, другие 2n логических входа первого дешифратора через элементы И подключены к логическим выходам тактового счетчика и соединены через другие элементы И с (1+  ) выходами того же дешифратора, а m дешифратор своими 2n другими логическими входами через элементы И подключен к

) выходами того же дешифратора, а m дешифратор своими 2n другими логическими входами через элементы И подключен к  ·

·  +1+2

+1+2 -ным своим выходам.

-ным своим выходам.

На фиг. 1 представлена схема предлагаемого устройства второй фазы четырехфазной системы при n 4 (n разрядность счетчика); на фиг. 2 диаграммы передачи каналов управления.

Устройство содержит логические входы 1-8, которые подключены к логическим выходам триггеров 9-12 тактового счетчика 13, другие логические входы 14-21 подключены к логическим выходам триггеров 22-25 реверсивного счетчика 26. Выходные шины 27-30 подключены к элементу ИЛИ 31 и через логические элементы И 32-34, 35 соединены с входами 1-8 со стороны тактового счетчика и с выходами 14-21 со стороны реверсивного счетчика. Элементы управления на чертеже не показаны.

Диаграммы на фиг. 2 показывают зону регулирования 36, первого канала управления 37, второго канала 38, третьего канала 39, четвертого канала 40, закон изменения коэффициента заполнения γ в диапазоне 0 ≅γ≅1,0 первой фазы 41, второй фазы 42, третьей фазы 43 и четвертой фазы 44 (m 4) со смещением во времени начала работы каждой фазы одна относительно другой на 0,25 Т.

Устройство работает следующим образом.

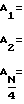

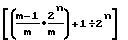

Таблицу состояний триггеров разбивают на части, равные числу фаз m, в данном случае на четыре. Матрицу каждого из m дешифраторов со стороны реверсивного счетчика 26 набирают одинаково на четыре состояния в соответствии с таблицей, а матрицы каждого дешифратора со стороны тактового счетчика набирают на различные состояния. Так дешифратора I матрица набирается на 1-е, 2-е, 3-е, 4-е состояния триггеров тактового счетчика; дешифратора II на 5-е, 6-е, 7-е, 8-е состояния; дешифратора III на 9-е, 10-е, 11-е, 12-е и дешифратора IV на 13-е, 14-е, 15-е, 16-е состояния. В общем случае матрица дешифратора I набирается на 0÷2n/4 состояния, дешифратора II на 2n/4 + 1÷2n/2 состояния, дешифратора III на 2n/2+1÷3/4˙2n состояния, дешифратора IV 3/4 ˙2n+ 1÷2n состояния.

Состояния Дешифраторы триггеров I II III IV

0 0 0 0 0

1 1 0 0 0

2 1 1 0 0

3 1 1 0 0

4 0 0 1 0

5 1 0 1 0

6 0 1 1 0

7 1 1 1 0

8 0 0 0 1

9 1 0 0 1 10 0 1 0 1 11 1 1 0 1 12 0 0 1 1 13 1 0 1 1 14 0 1 1 1 15 1 1 1 1 16 0 0 0 0

При этом в отличие от классической схемы дешифратора функционирование каждого дешифратора можно описать следующим образом:

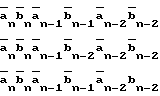

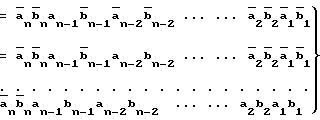

дешифратор первой фазы

дешифратор второй фазы

дешифратор третьей фазы

дешифратор четвертой фазы

где a,

где a,  , b,

, b,  прямые и инверсные выходы триггеров соответственно тактового и реверсивного счетчиков.

прямые и инверсные выходы триггеров соответственно тактового и реверсивного счетчиков.

В устройстве, показанном на фиг. 1, дешифратор выполнен в качестве дешифратора второй фазы и по отношению к первой фазе обеспечивает регулирование в диапазоне 0,25 Т≅ t и ≅ 0,5 Т.

Матрица дешифратора второй фазы набрана следующим образом. Элемент И 32 первой выходной шины 27 со стороны реверсивного счетчика 26 набран на первое состояние триггеров 22-25 (1-0-0), а со стороны тактового счетчика 13 на пятое состояние триггеров (1-0-1-0) 9-12. Элемент И 33 со стороны реверсивного счетчика 26 набран на второе состояние триггеров 22-25 (0-1-0-0), а со стороны тактового счетчика 13 набран на шестое состояние триггеров (0-1-1-0). Элемент И 34 выходной шины 29 со стороны реверсивного счетчика 26 набран на третье состояние триггеров, а со стороны тактового счетчика 13 на седьмое состояние (1-1-1-0). Элемент 35 И последней шины 30 со стороны реверсивного счетчика 26 набран на четвертое состояние триггеров 22, 23, 24, 25 (0-0-1-0), а со стороны тактового счетчика 13 на восьмое состояние триггеров 9-12 (0-0-0-1).

Матрицы дешифраторов первой, третьей и четвертой фаз (не показаны) набраны по аналогичному принципу, т.е. со стороны реверсивного счетчика 26 набраны элементы И на одни и те же состояния триггеров реверсивного счетчика 26, а со стороны тактового счетчика 13 каждый дешифратор набран на свои состояния триггеров тактового счетчика, которые сдвинуты во времени 0,25 Т (в соответствии с таблицей).

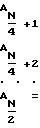

Таким образом, матрица дешифратора III со стороны реверсивного счетчика 26 набрана на состояния 1-4 триггеров, а со стороны тактового счетчика 12 на 9-12 состояния. Матрица дешифратора IV со стороны реверсивного счетчика 26 набрана также на состояния 1-4 триггеров, а со стороны тактового счетчика 13 на состояния 13-16 триггеров. Такой набор матриц дешифраторов позволяет обеспечить регулирование длительности включенного состояния тиристоров каждой фазы в пределах 0 ≅ t и ≅Т со смещением во времени на  Т.

Т.

Однако количество элементов для этого требуется значительно меньше, причем эффективность такого построения дешифраторов увеличивается при увеличении количества фаз преобразователя.

Таким образом изобретение позволяет повысить надежность КПД устройства, снизить габариты, стоимость, потребляемую мощность.

УСТРОЙСТВО ДЛЯ ЦИФРОВОГО УПРАВЛЕНИЯ M-ФАЗНЫМ ТИРИСТОРНО-ИМПУЛЬСНЫМ ПРЕОБРАЗОВАТЕЛЕМ, где m четное число фаз, включающее в себя тактовые и реверсивные счетчики с n триггерами, предназначенные для воздействия на элементы управления, m дешифраторов, каждый из которых содержит 2n логических входа (n разрядность счетчика), подключенных к логическим выходам тактовых счетчиков, и 2n логических входа, подключенных к 2n логическим выходам реверсивного счетчика, элементы И, отличающееся тем, что, с целью упрощения и расширения области его применения, выходы  каждого дешифратора подключены через элементы И к логическим выходам реверсивного счетчика, другие 2n логических входа первого дешифратора через элементы И подключены к логическим выходам тактового счетчика и соединены через другие элементы И с

каждого дешифратора подключены через элементы И к логическим выходам реверсивного счетчика, другие 2n логических входа первого дешифратора через элементы И подключены к логическим выходам тактового счетчика и соединены через другие элементы И с  выходами того же дешифратора, а m дешифратор своими 2n другими логическими входами через элементы И подключен к

выходами того же дешифратора, а m дешифратор своими 2n другими логическими входами через элементы И подключен к  -м своим выходам.

-м своим выходам.

| Чиликин Г.М., Лось В.А | |||

| Схемы управления тиристорно-импульсными преобразователями с дискретным сдвигом управляющих импульсов | |||

| Труды Днепропетровского института инженеров железнодорожного транспорта | |||

| Способ обделки поверхностей приборов отопления с целью увеличения теплоотдачи | 1919 |

|

SU135A1 |

Авторы

Даты

1995-06-09—Публикация

1977-06-30—Подача