(54) УСТРОЙСТВО ДЛЯ ПРЕРЬЮАМШ liPOnpAMM

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прерывания программ | 1985 |

|

SU1254486A1 |

| Микропрограммное устройство для обработки прерываний | 1983 |

|

SU1126956A1 |

| Устройство для прерывания резервированной вычислительной системы | 1984 |

|

SU1218385A1 |

| Устройство для обработки прерываний | 1983 |

|

SU1104518A1 |

| Устройство приоритетного прерывания для микро-ЭВМ | 1982 |

|

SU1113803A1 |

| Устройство для прерывания программ | 1977 |

|

SU739534A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1291983A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство прерывания | 1982 |

|

SU1084795A1 |

| Приоритетное устройство | 1984 |

|

SU1260956A1 |

Изобретение относится к области вычислитепьной техники, в чЕастаЕооти Е устройствам для прерьгеания программ. Известны устройства для пр ывашя программ с автоматической выработкой кодов прерывания ,но не обеспечивающие достаточно ивароких функцйбйальяых возможностей обработки возникаюшщс ферьгоаний. Наиболее близхшм по технической сущяости к предложенному является устройство для прерывания программ, которое содержит триггеры прерьгоаний, в одалуЬтрановки 1 которых со единены с вьгходамй ёментов И, первые входы которых соедия сы с выходами соответствующих триггеров управления, а вторые входы - со второе группой входов устройства и через инверторы - с входами установки 1 триггеров ynpaBnejfnra, блок приоритета, прерываний первая группа входов которого соединён на с выходами триггеров прерываний, а вторая группа входов является первой группо и входов устро йс ТВ а, шифратор, выходы которого соединены с входами регистракода прерываний, выходы которого соединен с группой выходов устройства И. В этом устройстве прерываний все причины прерываний одинаково принимаются к обслуживанию, независимо от-причины, вызвавшей пр ываадю текущей программы, что приводвпР к сужению функциональных возможйостей ycTpoSc-raaj кроме того, прием заявок на прерывание всегда произ;воднтся ho Сигналам, йоступаюЩйм йз ц РГралЕЬнюго устройства управ ления ЭВМ, что,в свою очередь,приводит к уменьшению скорости рёакшт устройства. Цепь изофетения - увеличение быстродействия устройства. Это достигается т&л, что в устройство для прерьгеания программ введены триггеры приема кодов прерываний, первый и второй триггеры блокировки, вторая, третья и четвертая группы эпементов И, первый и второй элементы И, первый и второй элементы ИЛИ, первая, вторая и третья группы t элементов ИЛИ, причем первая группа выходов блока приоритета прерываний соединена с первыми входами элементов и второй группы, вторые входы которых соединены с нупевьпм выходом первого триггера блокировки и с первым входом первого элемента И, а выходы элементов И второй группы соединены со входами установки I триггеров приема кодов прерываний и входаMJI элементов ИЛИ третьей группы. Выходы триггеров приема кодов прерываний . соединены с первой группой входов шифратора и со входами элементов ИЛИ первой группы, выходы которых соединен с первыми входами первого и второго .элемента ИЛИ, со входами установки б триггеров приема кодов прерываний, с входом установки I первого триггера блокировки и с первым выходом устройства. Выход элементов ИЛИ третьей груп пы соединен с третьим выводом устройства. Вторая группа выходов блока приоритета прерываний соединена со второй группой входов шифратора, со входами элементов ИЛИ второй группы И с первым входами элементов И третьей и четвёртой группы, вторые входы которых соединены со вторым входом первого элемента И, с первым входом второго элетле15та И с входом установки О первого триггера блокировки, со вторым входом первого элемента ИЛИ и с третьим входом уст„ ройства для прерывания программ. Выход элементов ИЛИ второй группы соединен с третьим входом первого элемента И, четвертый вход которого подключен к нулевому выходу второго триггера 6noKJ B ки и к третьим входам элементов И второй группы, выход первого эл лента И соединен со входом установки I второго триггера блокировки и со вторым входом. второго элемента ИЛИ. ВхОд тановки О второго триггера блокировки подсоединен к выходу второго элемента И, а второй вход второго элемента И под ключен к единичному выходу второго, триггера блокировки. Выход второго элемента ИЛИ подключен ко второму выходу устройства для.прерывания программ. Вы ход первого элемента ИЛИ подключен к управляющему входу регистра кода прерьгааний, вХоДь синхронизации триггеров соединены с четвертым входом устройств длй прерывания nporpah-fM.

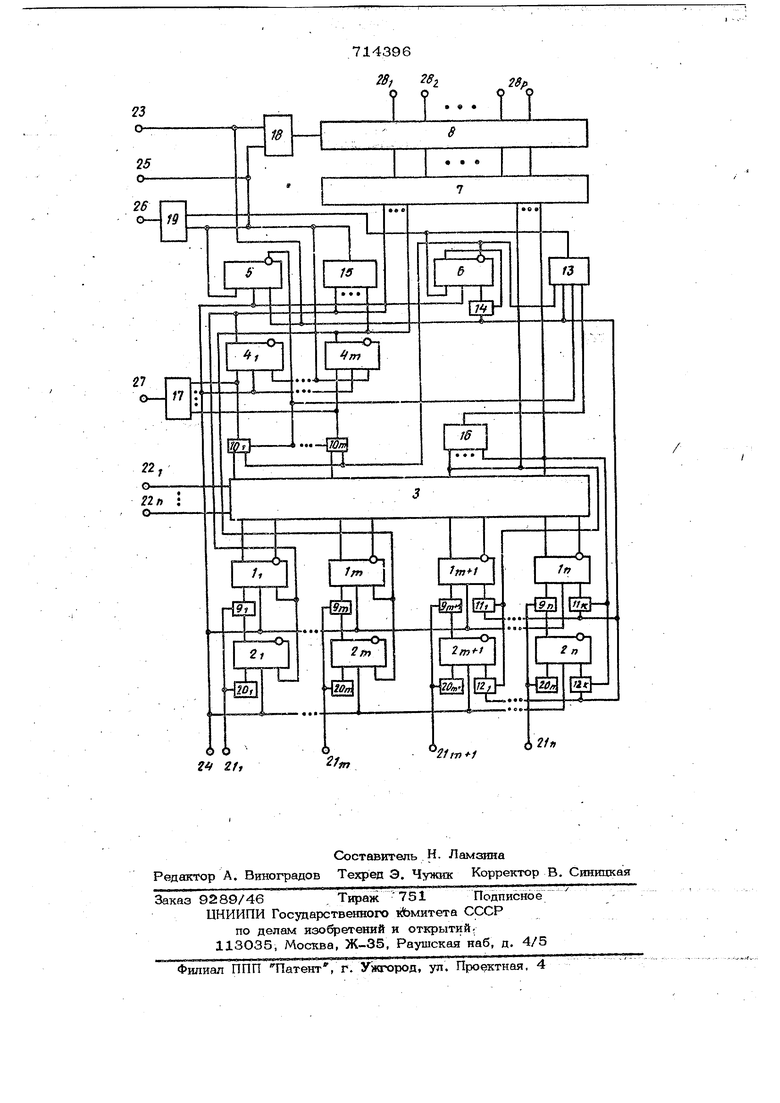

714396 Впок-схема предлагаемого устройства ля прерывания программ приведена на ертеже. Устройство содержит триггеры прерывания 1 - т первая группа, Ifyj4j п группа); триггеры управления 2 | - 2f fn первая группа, 2 - вторая группа), блок 3 приоритета; триггеры 4 - 4 приема кода прерывания, первый триггер 5 блокировки, второй триггер 6 блокировки, шифратор 7, регистр 8 кода прерываний, соответственно, первая, вторая, третья и четвертая группы элементов И 9-12, соответственно, первый и второй элементы И 13 и 14, соответственно, первая, вторая и третья группы элементов ЙЛЙ1 15-14первь1Йивторой элем ейты 18 и 19; группа инверторов 2 Oj 20 m вторые входы устройства 21 - 21г,от источников запрюсрв на прёрьгоание;; первые входы устройства 22 - 22 (от регистра масок), третий вход устройства 23 (опросный); четвертый вход устройства 24 (синхронизации), первый выход устройства 25 (на запуск устройства управления ЭВМ), второй вябд устройства 26 (на установку начального artpeca йанопрограммы Запоминание состояния), третий выход устройства 27 (на останов устройства управления ЭВМ); четвертые выходы устройства 28. - 28р (код прерывания). Прерьтание текущей программы осуществляется следующим образом. После поступления запроса на прерывание он запоминается и, если данная причина прерывания не замаскирована и нет прерываний С более высоким приоритетом, происходит прерывание программ, запоминается текущее состояние процессора посредством специальной служебной нанопрограммы Запоминание состояния и,в зависимости от кода прерывания,производится передача управления соответствующей обслужзтакюей программы. Устройство обеспечивает два уровня прерывания. В зависимости от причины прерывание осуществляется либо после окончания расшифровки текущей микрокоманды Т.е.; после поступления сигнала Конец, либо сразу после приема сигнала прерьгоания, не ожидай окончания расщифровки текущей микрокоманды. В исходном состоянии, при отсутствии запроса прерывания, все триггеры 2 находятся в единичном состоянии, а триггеры 1 в нулевом. Поступивший запрос неотлож571ного прерывания, например по вхбду;- 21 устанавливает триггер i в состояние 1 . Сигнал с единичного и нулевого выхода этого триггера 1 поступает на соответствующие входы блока приоритета 3 и при наличии разрешения на осталь ных входах (т. е. маска соответствующей причины прерывания не установлена, нет прерываний с более высоким приоритетом и устройство управления не находится в процессе ЗапЬминания текупГего состояния) сигнал прерывания через элемент И 1О|т, и ИЛИ 17 поступает на вызюд 27 и производит останов устройства управления ЭВМ (на чертеже не показано). Одновременно сигнал, снимаемый с выхода элемента И 10| поступает на единичный вход TpHrfepa 4. Триггер 4 fj устанавливается в единичное состояг Нйё, и сигнал с efo прямого выхода поступает на вход шифратора 7. Одновремй но этот сигнал :п6 цепи обратной связи поступает на входы установки нуля rpinrгеров 1 m и 2 fy, устанавливая их в йулевое состояние. Нулевой сигнад с ёдинич ного выхода триггера 2 блокирует дальнейший прием сигнала прерывания до тех пор, пока не снимается сигнал Ча ; входе 21f . Кроме того, сигнал, снимавмый с единичного в.ыхода триггера 4 ff через группу элементов ИЛИ 15 и 19 поступает на выход 26, обеспечивая ус- . тановку начального адреса нанопрограммы Запоминание состояния, и на выход 25, обеспечивая запуск устройства управления и сброс триггера 4 j в нулевое состояние. Таким образом, после сброса триггера 4,, на выходе группы элементов ИЛИ 15 получается голпутльс длительностью в один такт, который через элемент ИЛИ 16 осуществляет прием кода прерывания, сформированного на выходе шифратора 7, в регистр 8 кода прерывания. Этот импульс запоминается в триггере 5 блокировки, который на время работы нанопрограмм.ы Запоминание состояния устанавливается в единичное состояние. Сигнал с нулевого выхода триггера 5 поступает на вход элемента И 13, блокируя тем самым при« на обслуживание сигналов прерываний с меньшими приоритетами (т, к. к этому времени триггер Ip-j уже находится в состоянии О и имеется раэрешение на входах блока приоритета). Кроме того, этот же сигнал поступает на входы группы элементов И 10, блокируя прием на обслуживание сигналов прерыва66ний с большими приоритетами. Это де- . лается с целью сохранения информации о текущем состоянии ЭВМ. В конце нанопрограммы Запоминание состояния триггер 5 сбрасывается в нулевое состояние сигналом Конец,.поступающим на вход ч 23. Этот сигнал вырабатывается устройством управления ЭВМ в конце расшифровки каждой микрокоманды и в конце служебной нанопрограммы Запоминание сое-, -то5Пйш.: При постуш1е1ши на вход устройства сигнала, требующего прерывания программы после расшифровки текущей микрокоманды, например по входу прием этого сигнала триггером l, прерывания осуществляется аналогиявю вышеизложенному. Сигнал, снимаемый с единичного выхода триггера 1 щ 4 j если нет более приоритетных прерываний и не установлена, маска ;этой причины прерывания на входе 22, черет блок приоритета 3 поступает на вход ши1)ратора 7, на входы группы элементов И 11 и 12 и на вход группы элементов ИЛИ 16. С выхода группы элементов ИЛИ 16 сигнал прерывания после поступления сигнала Конец на вход 23 чфез элемент И 13 и элемента ИЛИ 19 устанавливает начальный адрес нанопрограммы Запоминание состояния , и устройство управления вместо расшифровки следующей команды переходит .к запоминанию текущего состояния.. Этим сигналом Конец триггеры lfr)4 1 .2 m-n сбрасываются в нулевое состо5шие, и через элеКТёнт ИЛИ 16 происходит прием кода прерывания в регистр в. Сигнал, снимаемый с выхода элемента И 11, кроме установют нач1зльнрго адреса нанопрограммы Затюминанио состояния перебрасывает триггер блокировки 6 в состояние . Нулевой сигнал с нулевого выхода триггера 6 на время работы этой, нанопрограммы блокирует входы группы элементов И 10 и 13, запрещая прием новых заявок на прерывание. В конце нанопрограммы Запоминание состояния триггер 6 сбрасывается в нулевое состояние сигналом Конец, поступающим на вход 23. Таким образом, предлагаемое устройство обеспечивает два уровля прорывания программ: неотложное прертлвшпкг, т. е. прерывание сразу поело поступлония заявки до окончания мтсрокомаилы, и прерьгеание поело окончания расшкфровки текущей микрокомяпды. Как слщуот из описания устр011ства, длитоль юсть сигналов прорывания с дробоого.1 бпп

дребезга фронтов может быть сколь угодШ) большой, однако дребезг фронтов его не должен попадать под синхросигнал, поступающий на синхровход устройства.

Предложенное устройство прерывания программ обладает более широкими функШГойаяьмыи )вой1 ожгюстями ,по сравнению с наиболее совёршейными известными аналогичными устройствами, & именно обеспе-чивает возможность прерывания программдьумя уровнями, благодари чему обеспечивается повышение скорости реакции на ряд запросов й ярерывание Сотнесйшые к запросем на пр ываниене ожяяакяаих сигнала Конед).

Формула ийобретейпя

ycTpoifctBO для прерывания нрограям, содержащее триггеры 1ф ывайиЙ, первую груапу элементов И, триггеры управ- йешя, шшерторы, блок фйорвггёУаЧферьдааний, шифратор, perkspp вода прерывй НИИ, вхойы которогр соеяянема с ЬызюдаМ2 шифратора, вводов бяйкй приоритета йпр ыЕванйй соедш а ; 1 й1 ре$юв йр ыванай а . вторая в;ю&дов яваявтся первой зфушюй входов устройства, вйодн yctaновки 1 зригге| в тф ывенкй сйёднйеjBEbi свыяодш s«fe «eKTOB И первой пы, шюды которых ооегшнеШ с визаздамя сйо 8етстбз1 янйх триггеров управиейия, а вторые взводы - со ©торой группой входов устройства и -через яяверторы - с входами установки 1 , t|5Hi repcjB управления, выяэды регистра кода прерыванзйЕй соедвнени с группой вьь заэдов устройства, отяичагоше е « я Тем, 4to, с дейью увепй%4нйя бь1стродейс вий устройства, в введены тригг ы приема кодов rtpie fifeaний, первый и второй трйгг ы йтоткировки, вторая третья и четвертая группы элементов И, первь5Й и второй эпемейты И, первый я второй элементы ИЛИ, первая, вторая и третья группы эйементов ИЛИ, причем группа выходов блока приоритета прерываний соецинетга с веръыш входами элементов и второй гру йы, вторые входы которых соединены с : нулевым выходом первого триггера бпоiKHpOBioi и с пёрвьш входом первО х элемента И, а выходы элементов И второй Ьруппы соединены со входами установки ,1 триггеров приема кодов Прерьгааний и входами элементов ИЛИ третьей группы, выходы триггеров приема кОдов прерываний соединены с первой группой вяодов шл% атора и со входами элементов ИЛИ первой группы, выходы которых соединены с первыми взоэдами первого и вторрзто элемента ИЛИ, со входами установки О триггеров приема кодов прерываний, с входом установки 1 первого триггера блокировки и с первым выходом устройства выход элементов ИЛИ третьей группы соединен с третьим выходом устройства, вторая группа вьщо-ч дов блока тфиоритета прерываний соединена с6 второй группой входов шнфраторй)Со входами элементов ИЛИ второй группы и с первыми входами элементов И третьей н четвертой грутшы, вторые вхды которых соединены со вторым входом irqpBoro элемента И, с первым входой второго, элетлента И с входом установки О первого триггера блокировки, со вторым входом первого элемента ИЛИ и с третьим входом устройства для прерывания программ, выход элементов ИЛИ rpynsbt с третьим входом нового элемен та И, че ертый вхОд которого подключен к нулевому выходу . второго триггера блокировки и к третьим В&одам элементов И второй группы, выход nefifeoro элемента И соединен со входом устаяовки 1 второго триггера бпоайроВБза со вторым входом второго элемент ИЛИ, вяод установки О второго триггера бкировки подсоединен к вьйаоду второго элемента И, а второй вход второго элемента И подключен к единичному выходу второго триггера блокировки, выход второго элемента ИЛИ подключен ко второiviy выходу устройства, выход первого элшлента ИЛИ подключен к злправляюшему входу регистра кода прерываний.

Источники информации, принятые во вшшание при экспертизе

2Sj Щ28f

Авторы

Даты

1980-02-05—Публикация

1977-10-10—Подача