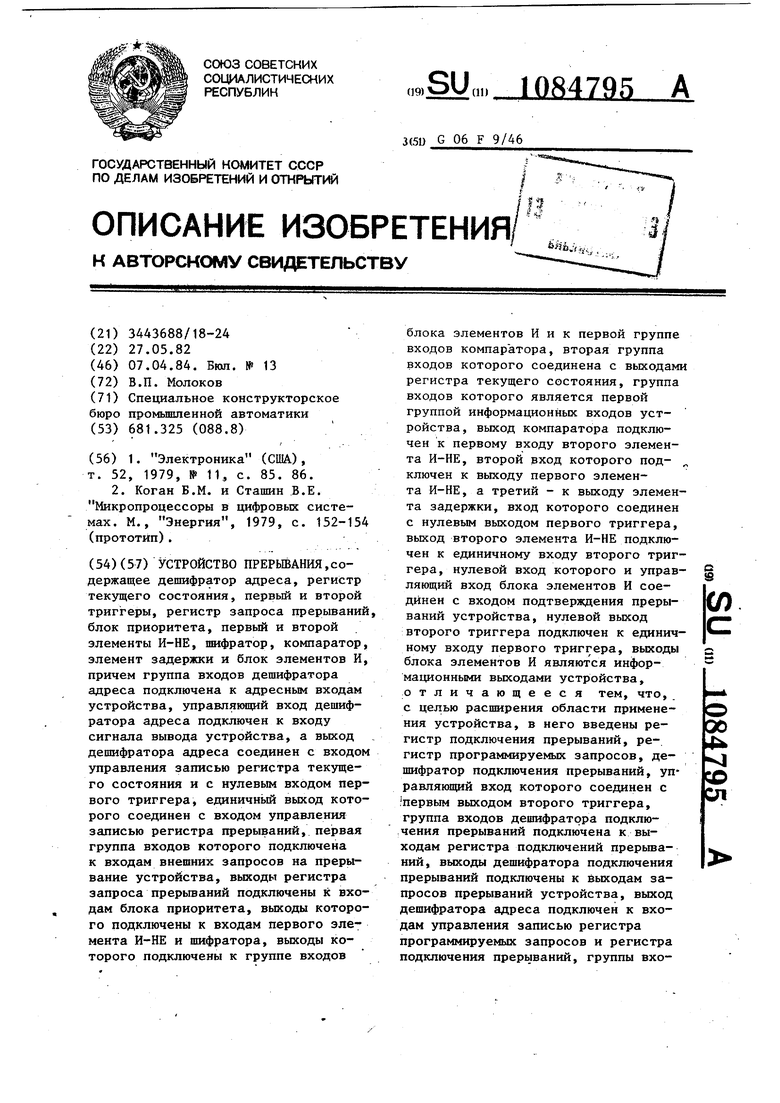

дов которых подключены соответствен- , но к второй и третьей группам информационных входов устройства,

выходы регистра программируемых запросов подключены к второй группе входов регистра запросов прерываний.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения группы процессоров с группой внешних устройств | 1988 |

|

SU1599865A1 |

| Устройство для обслуживания запросов | 1982 |

|

SU1109753A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для формирования сигналов прерывания | 1986 |

|

SU1341640A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для прерывания программ | 1985 |

|

SU1341636A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

УСТРОЙСТВО ПРЕРЫВАНИЯ,содержащее дешифратор адреса, регистр текущего состояния, первый и второй триггеры, регистр запроса прерываний, блок приоритета, первый и второй элементы И-НЕ, шифратор, компаратор, элемент задержки и блок элементов И, причем группа входов дешифратора адреса подключена к адресным входам устройства, управляющий вход дешифратора адреса подключен к входу сигнала вывода устройства, а выход дешифратора адреса соединен с входом управления записью регистра текущего состояния и с нулевым входом первого триггера, единичньй выход которого соединен с входом управления записью регистра прерываний, первая группа входов которого подключена к входам внешних запросов на прерывание устройства, выходы регистра запроса прерываний подключены к входам блока приоритета, выходы которого подключены к входам первого элемента И-НЕ и шифратора, выходы которого подключены к группе входов блока элементов И и к первой группе входов компаратора, вторая группа входов которого соединена с выходами регистра текущего состояния, группа входов которого является первой группой информационных входов устройства, выход компаратора подключен к первому входу второго элемента И-НЕ, второй вход которого под- „ ключей к выходу первого элемента И-НЕ, а третий - к выходу элемента задержки, вход которого соединен с нулевым выходом первого триггера, выход второго элемента И-НЕ подключен к единичному входу второго тригi гера, нулевой вход которого и управляющий вход блока элементов И соеСЛ динен с входом подтверждения прерываний устройства, нулевой выход второго триггера подключен к единичному входу первого триггера, выходы блока элементов И являются информационными выходами устройства, отличающееся тем, что, с целью расширения области примене00 ния устройства, в него введены регистр подключения прерываний, ре t;D ел гистр программируемых запросов, дешифратор подключения прерываний, управляющий вход которого соединен с .первым выходом второго триггера, группа входов дешифратора подключения прерываний подключена к выходам регистра подключений прерьгоаний, выходы дешифратора подключения прерываний подключены к вькодам запросов прерываний устройства, выход дешифратора адреса подключен к входам управления записью регистра программируемых запросов и регистра подключения прерываний, группы вхо

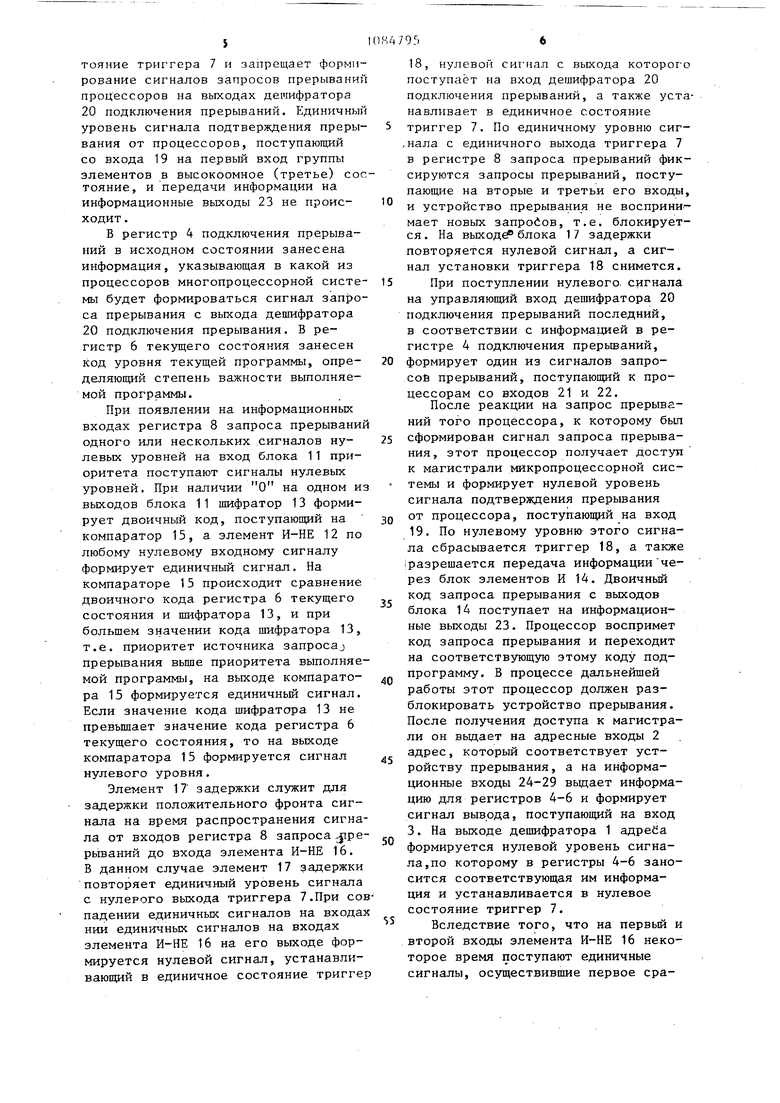

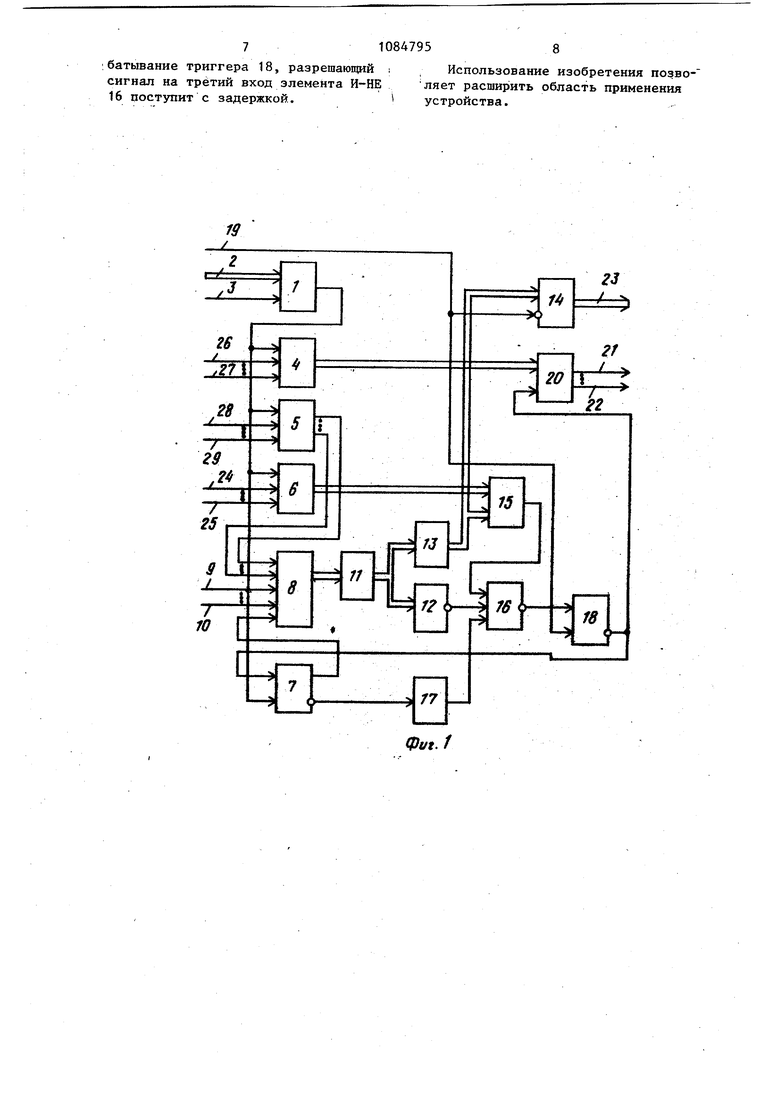

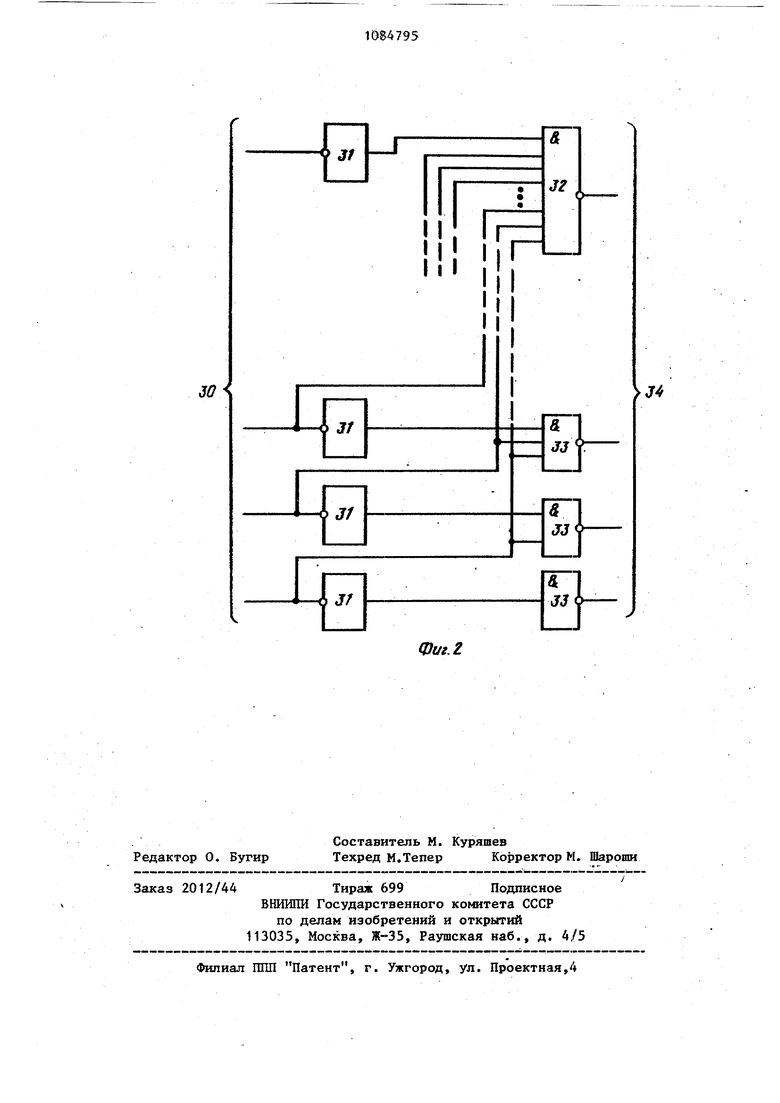

Изобретение относится к вычисли:тельной технике и может быть использовано в мультимикропроцессорны системах. Известно устройство вьщачи кода запроса прерывания на магистраль микропроцессорной системы, входящее в состав устройства для аппаратной реализации программных прерьюаний, содержащее порт вывода, на информационных входах которого закоммутиро вай код запросов прерывания, его информационные выходы подключены к шине данных магистрали, а его управляющий вход подключен к шине. подтверждения прерывания процессора При реакции процессора на запрос прерьшания процессор вырабатывает сигнал подтверждения прерывания, по которому порт вывода вьщает на шины данных код запроса прерывания,закоммутированный на его информационных входах ll. Недостатком устройства являются ограниченные возможности, обусловленные невозможностью его применения при наличии нескольких запросов прерывания без введения дополнитель ных технических средств. Наиболее близким к изобретению по технической сущности является субпроцессор для обработки прерываний, содержащий блоки приоритетных прерываний, порт ввода-вывода,инверторы, входы кода прерьшания блоков приоритетных прерьюаний и информационные выходы порта вводавывода подключены к шинам данных, входы разрешения записи текущего состояния блоков приоритетного прерывания ивходы выбора устройства порта ввода-вьюода подключены к выходам дешифратора портов ввода-вывода, выходы блока вектора прерывания блоков приоритетных прерываний подключены к информацион ным входам порта ввода-вьюода,выходы запроса прерывания блоков приоритетных прерываний подключены к входу первого инвертора, выход которого соединен с входом стробирования порта-вывода, вьжод прерывания которого соединен с входом второго инвертора, выход которого подключен к шине запроса прерывания, связанной с процессором. Известный субпроцессор обработки прерьгоаний подключается к интервейсу микропроцессорной системы как внешнее устройство. При поступлении на входы блоков приоритетных прерьюаний сигналов запросов прерываний от периферийных устройств субпроцессор формирует сигнал запроса прерывания, поступающий в микропроцессор, восприняв который микропроцессор выполняет команду ввода вектора прерывания из субпроцессора, по которой с выходов порта ввода-вывода на шины данных вьщается код вектора прерывания zj . Недостатком известного устройства являемся то, что оно позволяет организовать прерывание только в одном микропроцессоре. Цель изобретения - расширение области применения устройства. Поставленная цель достигается тем, что в устройство прерывания содержащее дешифратор адреса, регистр текущего состояньгя, первый и второй триггеры, регистр запроса прерьюаний, блок приоритета,первый и второй элементы И-НЕ, шифратор, компаратор, элемент задержки и блок элементов И, причем группа входов дешифратора адреса подключена к адресным входам устройства,управляющий вход дешифратора адреса подключен к входу сигнала вывода устройства, а выход дешифратора адреса соединен с входом управления записью регис.тра текущего состояния и с нулевым входом первого триггера,. единичный выход которого соединен с входом управления записью регистра прерываний, первая группа входов которого подключена к входам внашних запросов на прерывание устройства, выходы регистра запроса прерываний подключены к входам блока приоритета выходы которого подключены к входам первого элемента И-НЕ, и шифратора, выходы которого подключены к группе входов блока элементов И и к первой группе входов компаратора, вторая группа входов которого соединена с выходами регистра текущего состояния, группа входов которого является первой группой информационных входов устройства, выход компаратора подключен к первому входу второго элемента И-НЕ второй вход которого подключен к выходу первого элемента И-НЕ, а третий - к выходу элемента задержки, вход которого соединен с йулевым выходом первого триггера, выход второго элемента И-НЕ подключен к единичному входу, второго триггера, через нулевой вход которого и управляющий вход блока элементов И соединены с входом подтверждения прерываний устройства, нулевой выход второго триггера подключен к единичному входу первого триггера, выходы блока элементов И являются информационными выходами устройства, введен регистр подключения прерываний,регистр программируемых запросов,дешифратор подключения прерываний, управлякяций вход которого соединен с первым выходом второго триггера,груп па входов дешифратора подключения прерываний подключена к выходам регистра подклю 1ения прерываний, выход дешифратора подключения прерываний подключень к выходам запросов прерываний устройства, выход дешифратора адреса подключен к входам управления записью регистра программируемых запросов и регистра подключения прерываний, группы входов которых подключены соответственно к второй и третьей группам информационных входо устройства, выходы регистрй програм. мируемых запросов подключены к втора группе входов регистра запросов прер ваний. На фиг.1 дана структурная схема устройства прерывания; на фиг.2 - то же, блока приоритета. Устройство содержит дешифратор 1 адреса, адресные входы 2 устройства 954 вход 3 сигнала вывода устройства,регистр 4 подключения прерываний, регистр 5 программируемых запросов, регистр 6 текущего состояния,триггер 7, регистр 8 запросов прерываний, входы 9 и 10 внешних запросов на прерывание, блок 11 приоритета, элемент И-НЕ 12. шифратор. 13, блок элементов И 14. компаратор 15, элемент И-НЕ 16,элемент 17 задержки, триггер 18, вход 19 подтверждения прерываний устройства, дешифратор 20 подключения прерываний, выходы 21 и 22 запросов Прерываний устройства, информационные выходы 23 устройства,информационные входы 24-29 устройства. Блок приоритета содержит входы 30, элементы НЕ 31, элементы И-НЕ 32 и 33 выходы 34. Устройство работает следующим образом. При единичном уровне сигнала на управляющих входах регистров 4-6 и 8 их состояние не изменяется, при нулевом уровне сигнала на управляющих входах регистров 4-6 и 8 информация с их информационных входов передается на их выходы. В исходном состоянии входные сигналы - сигнал вывода, поступающий с входа 3, сигнал подтверждения прерывания от процессоров с входа 19, сигналы запросов прерываний от -периферийных устройств с входов 9 и 10, а также выходные сигналы регистра 5 программируемых прерываний имеют уровень логической единицы и не изменяют состояния устройства.Триггеры 7 и 18 обращены в нулевое состояние. Сигнал нулевого уровня с единичного выхода триггера 7 разрешает прохождение сигналов запросов прерываний от периферийных устройств через регистр 8 запроса прерываний, и при отсутствии сигналов нулевого уровня на каком-либо входе блока 11 приоритета сигналы на его выходе будут иметь единичные уровни, в соответствии с чем на выходе первого элемента И-НЕ 12 формируется сигнал нулевого уровня, запрещающий формирование на выходе второго элемента И-НЕ 16 нулевого уровня сигнала установки триггера 18 в единичное состояние . Сигнал единичного уровня со входа 19 не изменяет состояние триггера 18, а единичный сигнал на нулевом выходе триггера 18 не изменяет состояние триггера 7 и запрещает форми рование сигналов запросов прерывани процессоров на выходах дешифратора 20 подключения прерываний. Единичны уровень сигнала подтверждения преры вания от процессоров, поступающий со входа 19 на первый вход группы элементов в высокоомное (третье) со тояние, и передачи информации на информационные выходы 23 не происходит. В регистр 4 подключения прерываний в исходном состоянии занесена информация, указывающая в какой из процессоров многопроцессорной систе мы будет формироваться сигнал запро са прерывания с выхода дешифратора 20 подключения прерывания. В регистр 6 текущего состояния занесен код уровня текущей программы, определяющий степень важности выполняемой программы. При появлении на информационных входах регистра 8 запроса прерывани одного или нескольких сигналов нулевых уровней на вход блока 11 приоритета поступают сигналы нулевых уровней. При наличии О на одном и выходов блока 11 шифратор 13 формирует двоичный код, поступающий на компаратор 15, а элемент И-НЕ 12 по любому нулевому входному сигналу формирует единичный сигнал. На компараторе 15 происходит сравнение двоичного кода регистра 6 текущего состояния и шифратора 13, и при большем значении кода шифратора 13, т.е. приоритет источника запросаj прерывания вьш1е приоритета выполняе мой программы, на выходе компаратоpa 15 формируется единичный сигнал. Если значение кода шифратора 13 не превьшхает значение кода регистра 6 текущего состояния, то на выходе компаратора 15 формируется сигнал нулевого уровня. Элемент 17 задержки служит для задержки положительного фронта сигнала на время распространения сигна ла от входов регистра 8 запроса ,jipe рьгааний до входа элемента И-НЕ 16. В данном случае элемент 17 задержки повторяет единичный уровень сигнала с нулевого выхода триггера 7.При со падении единичных сигналов на входа НИИ единичных сигналов на входах элемента И-НЕ 16 на его выходе формируется нулевой сигнал, устанавливающий в единичное состояние тригге 18,нулевой сигиал с выхода которого поступает на вход дешифратора 20 подключения прерываний, а также устанавливает в единичное состояние триггер 7. По единичному уровню сиг,нала с единичного выхода триггера 7 в регистре 8 запроса прерываний фиксируются запросы прерываний, поступающие на вторые и третьи его входы, и устройство прерывания не воспринимает новых запросов, т.е. блокируется . На выход блока 17 задержки повторяется нулевой сигнал, а сигнал установки триггера 18 снимется. При поступлении нулевого, сигнала на управляющий вход депшфратора 20 подключения прерываний последний, в соответствии с информацией в регистре 4 подключения прерьшаний, формирует один из сигналов запросов прерываний, поступающий к процессорам со входов 21 и 22. После реакции на запрос прерываний того процессора, к которому был сформирован сигнал запроса прерывания, этот процессор получает доступ к магистрали микропроцессорной системы и формирует нулевой уровень сигнала подтверждения прерывания от процессора, поступающий на вход 19.По нулевому уровню этого сигнала сбрасывается триггер 18, а также разрешается передача информациичерез блок элементов И 14. Двоичный код запроса прерывания с выходов блока 1А поступает на информационные выходы 23. Процессор воспримет код запроса прерывания и переходит на соответствующую этому коду подпрограмму, В процессе дальнейшей работы этот процессор должен разблокировать устройство прерывания. После получения доступа к магистрали он выдает на адресные входы 2 адрес, который соответствует устройству прерьюания, а на информационные входы 24-29 вьщает информацию для регистров 4-6 и формирует сигнал вывода, поступающий на вход 3. На выходе дешифратора 1 адрейа формируется нулевой уровень сигнала, по которому в регистры 4-6 заносится соответствующая им информация и устанавливается в нулевое состояние триггер 7. Вследствие того, что на первый и второй входы элемента И-НЕ 16 некоторое время поступают единичные сигналы, осуществившие первое ера710847958

батывание триггера 18, разрешающий i Использование изобретения позвосигнал на третий вход элемента И-НЕ ляет расширить область применения 16 поступит с задержкой. устройства.

I I

30

J

r

Jjdh-- J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электроника (США), т | |||

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Устройство для выпрямления опрокинувшихся на бок и затонувших у берега судов | 1922 |

|

SU85A1 |

| Пюпитр для работы на пишущих машинах | 1922 |

|

SU86A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Коган Б.М | |||

| и Сташин В.Е | |||

| Микропроцессоры в цифровых системах | |||

| М., Энергия, 1979, с | |||

| Способ образования азокрасителей на волокнах | 1918 |

|

SU152A1 |

Авторы

Даты

1984-04-07—Публикация

1982-05-27—Подача