ka памяти соединены соответственно с первым входом третьего элемента ИЛИ и через элемент задержки с суммируЙцим входом счетчика адресных зон, выход третьего элемента ИЛИ соединен с входом сброса второго триггера, с входом сброса счетчика адресных зон и с вторым входом второго элемента ИЛИ, вторые входы н выходы элементов И второй группы соединены соответственно с выходами дешифратора, с выходами четвертого элемента ИЛИ и с поразрядными входами сброса регистра блокировки прерываний, тактовый вход которого и второй вход третьего элемента ИЛИ

6956

соединены с входом сброса устройства, вькоды регистра блокировки прерываний являются индикационными выходами устройства, единичныевходы регистра блокировки прерываний соединены с ответными входами устройства, тактовьй вход второго триггера соединен с выходом четвертого элемента ИЛИ, выход второго элемента ШЕИ соединен с входом сброса счетчика адресов, счетный вход которого и тактовьй вход буферного регистра соединены с выходом второго элемента И, единичный и нулевой входы первого триггера соединены соответственно с первым и вторым входами режима устройства .

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для обработки прерываний | 1984 |

|

SU1188739A2 |

| Микропрограммное устройство для обработки прерываний | 1984 |

|

SU1277107A1 |

| Устройство для обмена информацией | 1986 |

|

SU1336017A1 |

| Приоритетное устройство | 1985 |

|

SU1411744A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Устройство для сопряжения ЭВМ с датчиками состояния телефонных линий связи | 1984 |

|

SU1265786A1 |

| Устройство для обработки запросов | 1982 |

|

SU1119013A1 |

| Устройство для обмена информацией | 1984 |

|

SU1180905A1 |

МИКР011РОГР.АММНОЕ УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ПРЕРЫВАНИЙ, содержащее первьй элемент И, первую элементов И, два триггера, первый элемент ИЛИ, регистр маски и регистр блокировки прерываний, причем входы прерываний устройства соединены с первыми входами элементов И первой группы, отличающееся тем, что, с целью расширения функциональных возможностей за счет введения относительного и заданного видов приоритета, расширения класса решаю1цик задач формированием микропрограьгм обработки прерьшаний абонентов с различным внутренним представлением данных и команд, в него введены вторая группа элементов И, блок элементов И, второй, третий, четвертый элементы ИЛИ, второй элемент И, счетчики адресов и адресных зон, дешифратор, блок памяти, элемент задержки, буферный регистр, причем второй вход каждого элемента И первой группы соединен с вькодом одноименного разряда регистра блокировки прерываний, третий вход каждого элемента И первой группы соединен с выходом одноименного разряда ре- гистрт-а маски, группа входов которого является группой кодовых входов устройства, выход кажцого элемента И первой группы соединен с первым входом одноименного элемента И второй группы и с соответствующим входом первого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ и с счетным входом счетчика адресных зон, группа выходов- которого соединена с группой входов адреса зогш блока памяти и с группой входов дешифратора, первая и вторая, (/) группы выходов блока памяти соединены с первой и второй группами входов буферного регистра, первая и вторая группы выходов которого соединены соответственно с группой выходов устройства и с группой входов блока элементов И, группа вькодов и вход которого соединены соответственно с группой входов счетчика адресных зон и с прямым выходом первого триггера, инверсный выход кото-/ рого соединен с вторым входом первого элемента И, третий и четвертый входы которого соединены соответственно с первым тактовым входом устройства и с инверсным вькодом второго триггера, прямой вькод которого соединен с первым входом второго элемента И, второй вход которого соединен с вторым тактов-ым входом устройства, вход логической единицы которого соединен с В-входами второго триггера и регистра блокировки прерьшаний, первьш и второй выходы бло

Изобретение относится к вычислительной технике и может быть исполь зовано в цифровых вычислительных машинах, работающих в однопроцессор ном, мультипроцессорном и мультипрограммном режимах. Известно устройство прерывания, содержащее регистр прерывания, груп пы элементов И, группы элементов НЕ регистр маски, группы элементов ИЛИ регистр взаимодействия запросов tj Недостатками известного устройства являются сравнительно большой объем оборудования и узкие функциональные возможности. Наиболее близким к предлагаемому является устройство для обработки прерывания, содержащее регистр мас;КИ, группы элементов И, шифратор, ;блок элементов И, элемент ШЖ, эле|мент И и два триггера управления, причем информационные входы регистра маски являются первой группой информационных входов устройства, р рядные выходы регистра прерывания соединены соответственно с первыми входами элементов И группы, выход .шифратора является выходом устройства, разрядные выходы регистра мас ки соединены соответственно с вторы входами элементом И группы, инфор 5aциoнньй вход регистра прерывания соединен с выходом блока элементов группа входов блока элементов И явл ется второй группой информационных входов устройства, выходы элементов И группы соединены соответственно с входом элемента ИЛИ и с группой входов шифратора, выход элемента ИЛИ соединен с первым входом элемента И, второй вход элемента И соединен с тактовым входом устройства, нулевой вход первого триггера управления и нулевой вход второго триггера управления соединены с управляющим входом блока элементов И, выход второго триггера управления соединен с управляющим входом шифратора, выход каждого элемента И группы, кроме последнего, Соединен с третьим входом последующего элемента И группыГ. Недостатки данного устройства сравнительная узость функциональных возможностей и класса решаемых задач. Цель изобретения - расширение функциональных возможностей за счет введения относительного и заданного видов приоритета, расширег-гие класса решаемых задач формированием микропрограмм обработки прерьюаний абонентов с различным внутренним представлением данньЕс и команд. Поставленная цель достигается тем, что в микропрограммное устройство для обработки прерываний, содержащее первьм элемент И, первую группу элементов И, два триггера, первый элемент ИЛИ, регистр маски и регистр

блокировки прерываний, причем входы прерьшаний устройства соединены с первыми входами элементов И первой группы, введены вторая группа элементов И, блок элементов И, второй, третий, четвертый элементы ИЛИ, второй элемент И, счетчики адресов и адресных зон, дешифратор, блок памяти, элемент задержки, буферный регистр, причем второй вход каждого элемента И первой группы соединен с выходом одноименного разряда регистра блокировки прерываний, третий вход каждого элемента И первой группы соединен с выходом одноименного разряда регистра маски, группа входов которого является группой кодовых выходов устройства, выход каждого элемента И первой группы соединен с первым входом одноименного элемента И второй группы и с соответствующим входом первого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, йыход которого соединен с первым входом второго элемента ИЛИ и с счетным входом счетчика адресных зон, группа выходов которого соединена с группой входов адреса зоны блока памяти и с группой входов дешифратора, первая и вторая группы выходов блока памяти соединены с первой и второй группами входов буферного регистра, первая и вторая группы выходов которого соединены соответственно с группой выходов устройства и с группой входов блока элементов И, группа выходов и вход которого соединены соответственно с группой вхдов счетчика адаесных зон и с прямым вьтходом первого триггера инверсный выход которого :соединен с вторым входом первого элемента И, третий и четвертый входы которого соединены соответственно с первым тактовым входом устройства и с инверсным выходом второго триггера, прямой выход которого соединен с.первым входом второго элемента И, второй вход которого соединен с вторым тактовым входом устройства, вход логической единицы которого соединен сД-входами второго триггера и регистра блокировки прерываний, первый и второй выходы блока памяти, соединены соответственно с первьм входом третьего элемента ИЛИ и через элемент задержки с суммирующим входом счетчика

адресных зон, выход третьего элемента ИЛИ соединен с входом сброса второго триггера, с входом сброса счетчика адресных зон и с вторым входом второго элемента ИЛИ, вторые входы и выходы элементов И второй группы соединены соответственно с выходами дешифратора, с выходами четвертого э 1емента ИЛИ и с поразрядными входами сброса регистра блокировки прерываний, тактовьй вход которого и второй вход третьего элемента ИЛИ соединен с входом сброса устройства, выходы регистра блокировки прерываний являются индикационными выходами устройства, единичные входы регистра блокировки прерываний соединены с ответными входами устройства, тактовый вход второго триггера соединен с выходом четвертого элемента ИЛИ, выход второго элемента ИЛИ соединен с входо.м сброса счетчика адресов, счетный вход которого и тактовый вход буферного регистра соединены с выходом второго элемента И, единичньш и нулевой входы первого триггера соединены соответственно с первым и вторым входами режима устройства.

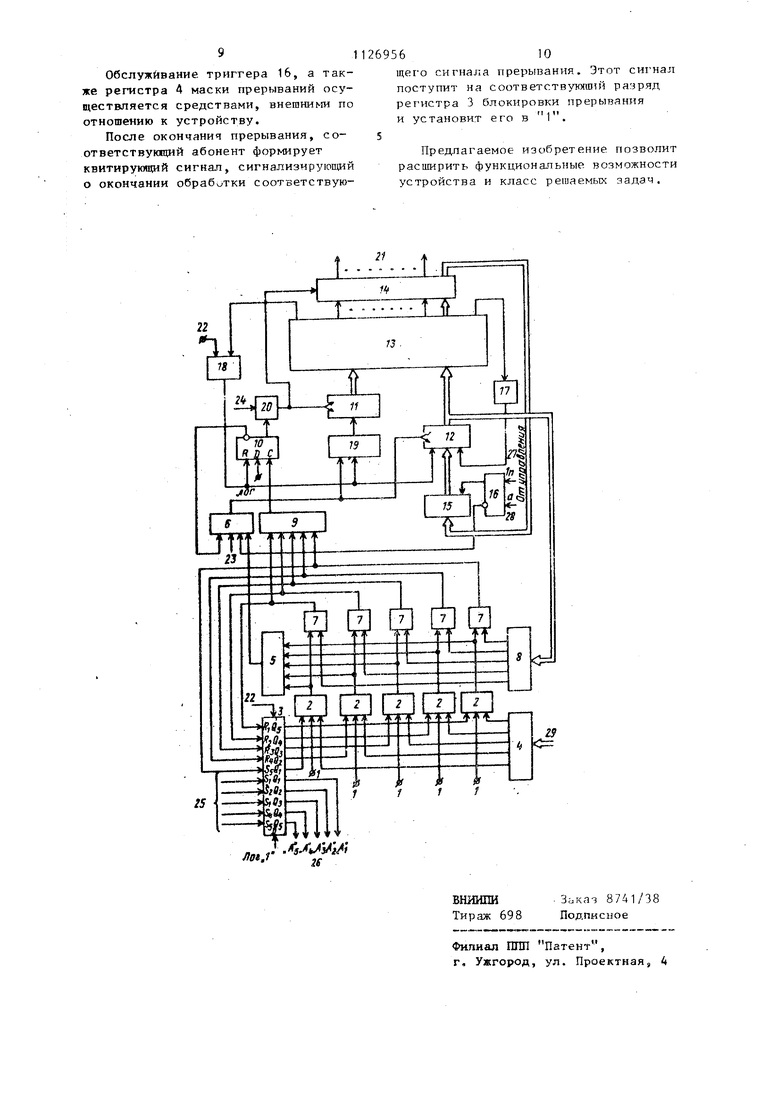

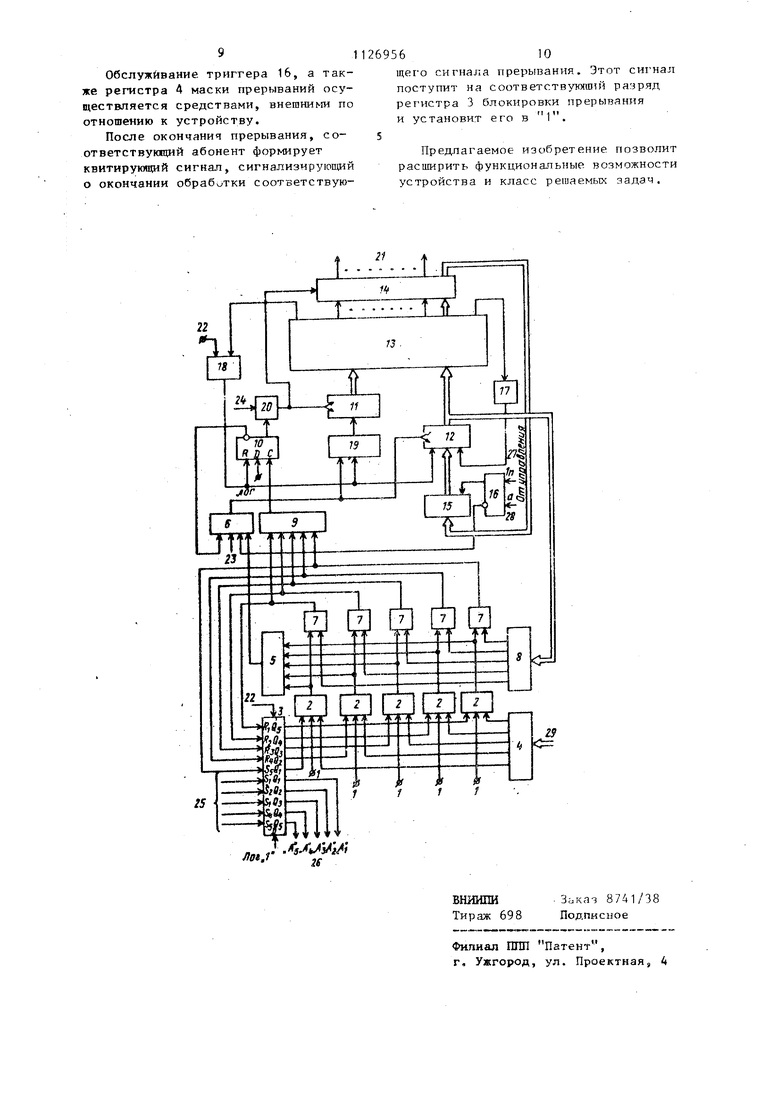

На чертеже представлена функциональная схема устройства для обработки прерывания.

Устройство содержит входы 1 сигналов прерывания, элементы И 2 первой группы, регистр 3 блокировки прерываний, регистр А маски, элемент ИЛИ 5, элемент И 6, элементы И 7 второй группы, дешифратор 8, элемент ИЛИ 9, триггер 10, счетчик 11 адресов, счетчик 12 адресных зон, блок 13 памяти, буферный регистр 14, блок 15 элементов И, триггер 16, элемент 17 задержки, элементы ИЛИ 18 и 19, элемент И 20, группу выходов 21, вход 22 сброса, первый 23 и второй 24 тактовые входы, ответные входы 25, индикационные выходы 26 входы 27 и 28 режима, группу кодовых входов 29.

Устройство работает следующим образом,

Незамаскированные сигналы прерьгеания с входов 1 через элементы И 2 первой группы поступают на элемент ИЛИ 5.

Управление элементами И 2 первой группы осуществляется соответствующим разрядом регистра 4, Количество разрядов регистра 4 определяется количеством входов 1 сигналов прерьгааний, требующих маскирования, т.е. запрещения на определенный момент времени. Вторыми входами элементов И 2 управляет регистр 3. . В первоначальный момент на его выхо дах устанавливаются единицы. Замаскированным считается- вход элемента И 2, на вход которого от регистра 4 поступает запрещающий потенциал, Элемент ИЛИ 5, на входе которого имеется хотя бы один сигнал ваний, разрещает работу элемента И 6, на второй вход которого поступает тактовая частота с входа 23. При наличии разрешающего потенци ла на третьем входе, элемент И 6 вьщает серию импульсньк сигналов, которая поступает на счетный вход счетчика 12, Количество импульсных сигналов в этой серии зависит от но мера обрабатьшаемого разряда прерыв ния и исходного состояния счетчика 12, Исходное состояние счетчика 12 адресных сигналов в первоначальный момент равно нулю, а в последующие зависит от вида приоритета, т.е. от состояния триггера 16. Количество импульсов в указанной серии формируется элементом И 6, счетчиком 12, депшфратором 8, одним из элементов И 7, элементом ИЛИ 9, триггерами 10 и 16. Так как на момент обработки сигналов прерывания триггеры 10 и 16 Находятся В состояниях, разрешающих (по соответствующим входам) работу элеме11та И 6, то сигнал прерывания прошедший с одного из входов 1 через элементы И 2 и ИЛИ 5 разрещит (в начале работы сигналом с входа 22, а в последующих циклах сигналом от блока 1З)прохождение импульсов на счетный вход счетчика 12 (счетчик 12 в этом режиме работы обн-улен Счетчик 12 прдсчитьтает эти импульсы и кодом, образуемым на его вькодах, через дешифратор 8 начинае поиск обрабатьшаемого разряда, последовательно опрашивая элементы И 7. При совпадении сигналов на вхо де элемента И 7, последний вырабаты вает сигнал, который через элемент ИЛИ 9 установит триггер 10 в состоя аие единицы. Своим нулевь м выходом триггер 10 запретит работу элемента И 6. 566 Таким образом, элемент И 6 вырабатывает серию импульсов, соответствующую номеру обрабатьшаемого сигнала (абонента) прерывания, а счетчик 12 зафиксирует соответствующий этому сигналу код базового адреса и будет его удерживать до полной обработки программы, обрабатывающей этот сигнал. Рассмотрим работу устройства прерывания при абсолютном приоритете обработки прерываний. Обработка сигналов прерывания начинается с нулевого значения счетчика 12. При поступлении импульсных сигналов на счетный вход счетчика 12 последний через дещифратор 8 поочередно подготавливает (начиная с нулевого) работу элементов И 7 второй группы. При совпадении сигнала прерывания с элементов И 2 первой группы и соответствунхцего сигнала с дешифратора В, элемент ИЛИ 9 установит триггер 10 в единичное состояние. Триггер 10 сигналом с инверсного выхода запрет по третьему входу элемент И 6, который прекратит поступление импульсных сигналов на счетный вход счетчика 12, а, следовательно, прекратит обнуление счетчика 11, которое проводилось каждым импульсным сигналом с элемента И 6 через элемент ИЛИ 19. Одновременно выделившийся сигнал на выходе соответствующего элемента И 7, установит передним фронтом в нулевое .состояние соответствующий разряд регистра 3. Этот разряд запрет соответствующий элемент И 2, номер которого зафиксирован в счетчике 12. Регистр 3 приводится в исходное состояние (разрешающее работу всех элементов И 2) сигналом с входа 22. В дальнейшем разблокировка соответствующего разряда регистра 3 проводится по единичному входу соответствующего разряда сигналом с соответствующего абонента. Таким образом, перепад (фронт) разряда регистра 3 блокировки прерывания, установленного в нулевое состояние (или его инверсное плечо) укажет сигнал прерывания, который в данный момент обрабатьшается в блоке прерьшания, а потенхц ал с данного разряда укажет нахождение абонента, формирующего сигнал прерьгоания в состоянии прерывания. Сигнала ми с регистра 3 запрещается обработка соответствующих сигналов прерывания, это означает, что прерывание в режиме прерывания запрещено, т.е. глубина прерывания от одного абонента равна единице. После срабатывания триггер 10 сигналом с его единичного выхода разрешается (подготавливается) рабо та элемента И 20. Элемент И 20 формирует на своем выходе серию импуль сов, передним фронтом которых счетчик 11 принимает значения от нулевого. Каждому такому значению счетчика 11 (которое является младшей частью общего адреса блока 13, а старшей частью этого адреса - значение Счетчика 12) соответствует микрокомандное слово зафиксированно в блоке 13. Последовательность микрокоманднь слов, которую можно рассматривать поразрядно или пословно, составляет микропрограмму, которая реализует запоминание слова состояния абонента или всю программу обработки прерьшания (включая восстановление слова состояния абонента) на начало прерывания. Данная микропрограь-1ма выполняетс до тех пор, пока в одном из ее разрядов, предназначенном для управления триггером 10, не будет считан сигнал, который произведет через элемент ШТИ 18 сброс триггера 10 в нулевое состояние. При этом тригг 10 разрешит работу элемента И 6, ко торый сбросит счетчик 11 в ноль. Так как микропрограмму можно рас сматривать как последовательность микрокоманд, длительность которых может быть различной, то изменение длительностимикрокоманд в устройст ве дискретно с точностью до периода входной частоты с входа 24. Для того, чтобы устранить перерьшы потенциалов микрокоманд, крторые снимаются с блока 13 по соседни адресам, на время выборки информации в устройство введен регистр 14, информация в который заносится с блока 13 по заднему фронту сигналов с элемента И 20. Таким образом, длительность пери да импульсов с входа 24 должна выби 68 раться из расчета времени выборки информации из-блока 13. Для управления работой устройства в блок 13 введена группа разрядов, управляющая видом приоритета. Приоритет обработки прерываний может бьпь абсолютным, относительным и заданным. Абсолютным считается вид приоритета, при Котором приоритетность отдается самому старшему (левому) разряду (входу) прерывания и он обрабатывается .всегда при его возникновении по окончании обработки текущего сигнала прерывания. Работа устройства при абсапютном приоритете была описана вьппе. Относительным считается вид приоритета, при котором следующим по порядку обрабатывается ближайнскй справа разряд относительно обработанного в текутций момент. Относительньп приоритет выполняется так же как и абсолютньй с той лишь разницей, что в устройстве не программируется 1, осуществляющая сброс счетчиков 12 и 11. Тогда следующим по порядку обрабатывается запрос на прерывание, сигнал которого присутствует и находится справа по приоритету относительно текущего. Заданным считается вид приоритета, 1Гри котором сама программа обрабатываемого запроса указывает номер запроса, который должен быть обработан вслед за ней. Задатчиком вида приоритета является триггер 16. Если триггер 16 находится в состоянии 1, то он своим сигналом с единичного выхода разрешает работу блока 15, через который в счетчик 12 впись Бается код зоны (каждая зона соответствует определенному абоненту) , микропрограмма которой должна быть отработана по окончанию отработки текущей. При этом триггер 16 запрещает работу элемента И 6. Этот код вписывается в счетчик 12 сигналом, поступаюпшм с блока 13 через элемент 17 Эсэдержки. Велриина задержки сигнала в линии 17 задержки определяется временем прохождения информации через блок 15 и требуемым временем опрежения информации для записи ее на счетчик 12.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство прерывания | 1974 |

|

SU525094A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления обслуживанием запросов | 1979 |

|

SU855663A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-30—Публикация

1983-06-08—Подача