Изобретение относится к вычислительной технике и может быть использовано в многоканальных резервированных микропроцессорных вычислительных системах для обработки прерываний.

Цель изобретения - повьш1ение достоверности работы устройства.

Повышение достоверности достигается за счет обеспечения синхронногс перехода системы в режим обработки прерывания при поступлении сигнала запроса хотя бы в одном канале, а также блокировки сигналов запросов прерьшаний, поступающих от каналов (процессоров) системы, KOTopbie постоянно (в режиме зависания) или стохастически формируют ошибочный сигнал запроса прерывания.

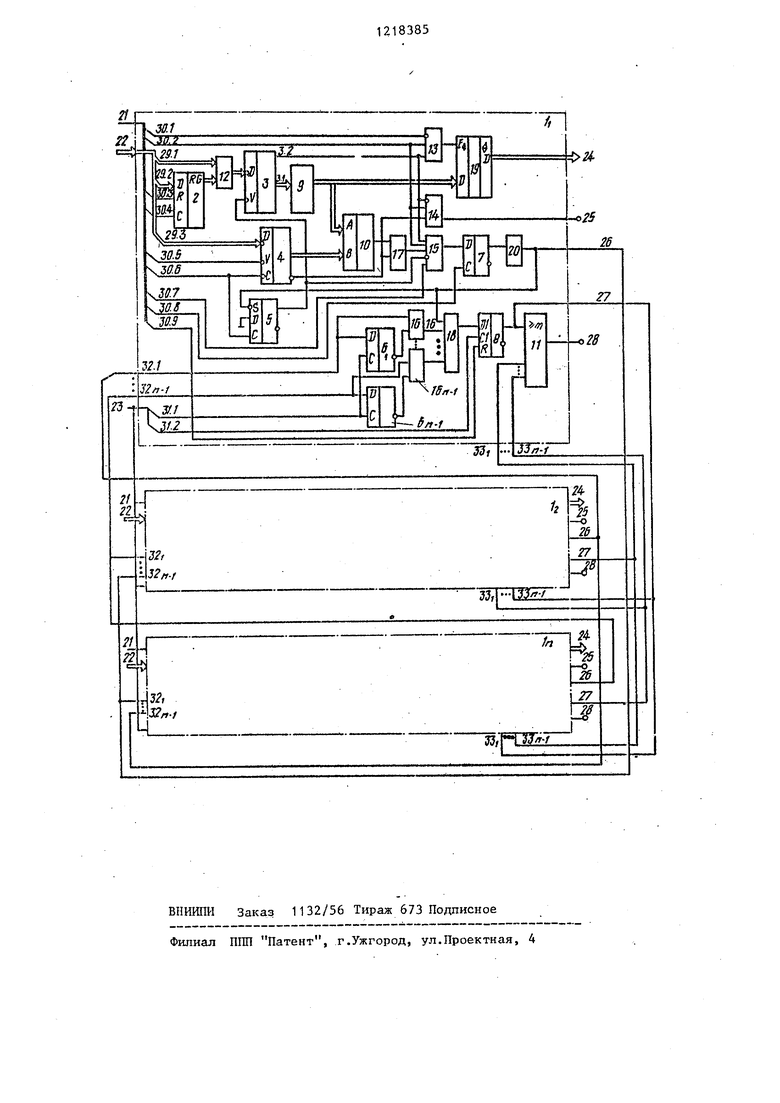

tla чертеже приведена функциональная схема устройства.

Устройство содержит идентичные каналы Ц - 1, , каждьй из которых содержит регистр 2 маски, регистр 3 запросов, регистр 4 текущего состояния, триггер 5 запрета прерываний, группу триггеров запрета прерываний, первый 7 и второй 8 триггеры прерывания. шифратор 9 приоритета, схему 10 сравнения, мажоритар- ньй элемент 11, блок 12 элементов И, первьй 13, третий 14 и второй 15 элементы И, группу элементов И 16ь-1, первьш 17 и второй 18 элементы lLjIИ ; блок 19 магистральных элементов, формирователь 20 импульсов. На чертеже указаны также групповые управляющие 21 и информационные 22 входы устройства, групповой синхронизирующий вход 23 устройства, групповые выходы 24 вектора прерыва ПИЯ устройства, выходы 25 разрешения прерьшания устройства, выходы 26 прерывания каналов, выходы 27 подтверждения прерывания каналов, вьпсо- цы 28 прерывания устройства,входы пе вой 29.1,второй 29.2 и третьей 29.3 групп разрядов группового информащ - онного входа 22 устройства,входы первого - девятого 30.1 - 30.9 разрядов группового управляющего входа 21 устройства, входы первого 31.1 и второго 31,2 разрядов группового синхронизирующего входа 23 устройств группы входов 32,-32 прерывания каналов, группы входов .| подтверждения прерывания каналов. Устройство работает следующим образом.

В исходном состоянии все элементы памяти устройства установлены в нулевое состояние (входы начальной установки на чертеже условно не показаны).

Для приведения устройства в рабочее состояние на входы 30.2 и 30.5 групповых управляющих входов 21 устройства подаются единичные сигналы. Кроме того, с входов 29.3 групповых информационных входов устройства в регистры 4 запросов всех каналов 1( ) записывается код текущего состояния (в начале - нулевой код) программы, выполняемой системой, по синхроимпульсу с входа 30.6. По этому же синхроимпульсу осуществляется установка в нулевое состояние триггера 5 запрета прерывания. При этом нулевой сигнал с выхода триггера 5 разрешает запись запросов на прерывания в регистр 3.

Регистр 2 масок устанавливается в нулевое состояние по сигналу с входа 30.3. По этому же сигналу осуществляется установка в исходное состояние микропроцессора, например, марки INTEL 8080 или К580ИК1 много- канальной мажоритарно-резервированной системы.

После выполнения указанных операций устройство готово к работе.

На групповые входы 22 устройства поступают информационные сигналы, промажоритированные по всем п каналам резервированной системы. Запись кода маски прерываний в регистр 2 осуществляется с входа 29.2. по сигналу с входа 30.4, который соответствует сигналу Вьщача микропроцессорной системы на базе процессора К580ИК1.

Код маски с выходов регистра 2 поступает на входы блока 12 элементов И, через которые осуществляется фильтрация сигналов запросов на прерывания, поступающих с входов 29.1 запросов. При этом любой незамаскированный сигнал запроса поступает на D-входы регистра 3 запросов.

Если в регистре 3 сигналы запросов отсутствуют, то шифратор 9 закрывает блок 19 магистральных элементов, запрещает выработку сигнала подтверж- дения прерывания через элемент ИЛИ 17 и разрешает выработку сигнала разрешения прерьшания на выходе элемента И 14.

При поступлении сигналов запросов прерывания с выходов блока 12 элементов И происходит их запоминание в регистре 3, Однако запрос после этого с входов 29.1 не снимается,та как регистр 3 выполнен на триггерах типа защелка и запоминание информации в регистре 3 произойдет только после установки триггера 5 в единицу

Информация с выхода 3.1 регистра 3 поступает на входы шифратора 9 запросов, которьш формирует код прерывания старшего приоритета. Сигнало с выхода 3.2 регистра 3, формиру емым при наличии хотя бы одного запроса в регистре, открывается элемент И 13 выходной сигнал которого открывает блок 19 магистральных элементов и разрешает передачу через него на выход 24 канала кода вектора прерывания. Кроме того, разрешается срабатывание элемента И 15 и запрещается вьщача сигнала разрешения с выхода элемента И 14 на выход 25 устройства.

Выходной код шифратора 9 поступаг ет также на входы А схемы 10, где осуществляется его сравнение с кодом текущей программы, записанным в регистр 4. Если код с выхода А шифратора.9 больше кода с выхода В регистра 4, то с выхода схемы 10 выдается сигнал, который через элемент ИЛИ 17 и открытый элемент И 15 поступает на D-вход триггера 7. Если же код на входе А схемы 10 меньше или равен коду на входе В, ТО на выходе схемы 10 сигнал отсутствует. Тогда сигнал подтверждения прерывания может быть выработан только в том случае, если в четвертый разряд регистра 4 по входу 30.5 будет записан нуль,так как инверсный выход этого разряда через элемент ИЛИ 17 функционально эквивалентен выходу схемы 10.

f

При наличии сигнала на выходе схемы 10 с поступлением разрешающего сигнала с входа 30.7 и синхроимпульса с вход;а 30.8 ос тцест- вляется запись единицы в триггер 7. Сигнал с единичного выхода триггера 7 через элемент 20 поступает на вход триггера 5, который устанавливается в единицу. При этом разрешается прием новых сигналов запросов в регистр 3 и подготавливается триг:гер 7 к сбросу в нулевое состояние. Поэтому с приходом очередного импуль

0

5

|са с входа 30.8 происходит установка триггера 7 в нулевое состояние. Таким образом, длительность существования сигнала на вььчоде триггера 7 определяется периодом следования импульсов с входа 30.8.

Формирователь 20 формирует единичный импульс на выходе 26 после установки триггера 7 в единичное состояние.

Для того, чтобы исключить возможность двойного прерывания по одному,и тому же запросу, а также прерывания по запросам младших прио5 ритетов относительно обрабатываемого, необходимо после обработки сигнала прерывания, формируемого с выходов 28 каналов, код программы обработки запроса записать в регистр 4 состояния аналогично описанному.

Если в этом нет необходимости, то в регистр 4 записывается нулевой код по сигналу с входа 30.6. В результате этого снова устанавливается в-нуль триггер 5 и осуществляется подготовка устройства к приему очередного запроса на прерывание. После формирования сигналов прерывания на выходах 26 каналов они поступают на соответствующие входы .. каждого из остальных, каналов.

В каждом канале сигналы прерываний от остальных каналов поступают на D-входы соответствующих триггеров 6 -6;tT и на первые входы соответствующих элементов И I6j. . При отсутствии отказов каналов сигналы с входов 32., поступают вне синхроимпульса, предназначенного для выявления ложной вьщачи сигнала прерывания, с входа 31.1. Поэтому триггеры ,. сигналами с нулевых выходов открывают элементы И . . Таким

образом, выходной сигнал канала с выхода формирователя 20 цли остальных каналов с выходов элементов И через элемент ШШ 18 поступают на D-вход триггера 8. По

0 сигналу синхроимпульса опроса прерывания с входа 31.2 происходит установка триггера 8 в единичное состояние. Сигнал с единичного выхода триггера 8 через выход 27

5 канала поступает на соответствующие входы группы входов . каждого из остальных каналов и далее на входы мажоритарного элемента 11.

0

5

0

Мажоритарный элемент 11 срабатывает при наличии в большинстве каналов сигналов прерывания и вьщает на выход 28 устройства сигнал прерыван в соответствующий канал системы,

В случае возникновения отказа, связанного с зависанием каналов, сигнал прерывания от такого канала обнаруживается в момент подачи синхроимпульса с входа 31.1, по которому соответствующий триггер из группы триггеров 6.-6 р,, устанавливается в единицу и блокирует, прохождение этого сигнала через соответствующий элемент И группы элементов И 1б.)-1б .

Тем самым обеспечивается защита устройства от сигналов прерываний, поступающих из отказавших каналов, которые могли бы вызвать ;рассинхронизацию каналов мажоритарно-резервированной системы.

Работа устройства прекращается с прекращением подачи управляюЕ1ИХ сиг налов с входов 21 .

Ф о р м у л а и 3 о б р е т е н и я

Устройство для прерывания резервированной вычислительной системы, содержащее первьш канал, включающи регистр маски, регистр запросов, ре гистр текущего состояния, триггер запрета прерываний, первый триггер прерывания, шифратор приоритета, схему сравнения, блок элементов И, первый, второй и третий элементы И, первьш элемент ИЛИ, блок магистральных элементов и формирователь им- пульсов, причем первые группы управляющих и информационных входов устройства соединены с группами одноименных входов канала, первьи

. разрешающий вход, первые рходы приведения в рабочее состояние и установки в 0 вход записи кода маски, второй вход приведения в рабочее состояние, вход сброса,

второй разрешающий вход и второй вход установки в О, группы управляющих входов канала соединены с группой инверсных входов первого элемента И, первым прямым входом

. первого элемента И, входом сброса регистра маски, входом синхронизации регистра маски, входом разрешения регистра текущего состояния, входам синхронизации регистра те0

5

0

5

0

0

5

0

5

кущего состояния и триггера .запрета прерываний, первым входом второI го элемента И и входом синхронизации первого триггера прерывания соответственно, первая, вторая и третья подгруппы разрядов группы

информационных входов канала соединены соответственно с первой группой входов блока элементов И, группой информационных входов регистра маски и группой информационных входов регистра текущего состояния, группа выходов которого соединена с первой группой входов схемы сравнения, группа выходов регистра маски соединена с второй группой входов блока элементов И, выходы которого соединены с группой информационных входов регистра запросов, группа вькодов регистра запросов соединена с группой входов ашфратора приоритета, группа выходов которого соединена с второй группой входов схемы сравнения и с группой информационных .входов блока магистральных элементов, выход первого элемента И соединен с входом разрешения блока магистральных элементов, инверсный выход регистра текущего состояния соединен с первыми входами первого элемента ИЛИ и третьего элемента И, информационный вход триггера запрета прерываний соединен с шиной нулевого потенциала устройства, единичный вмкод триггера запрета прерываний соединен с входом разрешения регистра запросов и инверсным входом второго элемента И, выход схемы сравнения соединен с вторым входом первого элемента ИЛИ, выход которого соединен с вторым прямым входом второго элемента И, первьй вход приведения в рабочее состояние группы управляющих входов канала соединен с вторым прямым входом третьего элемента И и третьим прямым входом второго элемента И, выход регистра запросов соединен с вторым прямым входом первого элемента И, инверсным входом третьего элемента И и четвертым прямым .входомi второго элемента И, выход которого соединен с информационным входом первого триггера прерывания, единичный вькод первого триггера прерывания через формирователь импульсов

. соединен с инверсным единичным

входом триггера запрета прерываний отлича-ющееся тем, что, с целью повышения достоверности работы, в него ..дополнительно введены h -1 ( Н -число запросов) каналов и в каждый канал дополнительно введены группа триггеров запрета прерываний второй триггер преры-. вания, мажоритарный элемент, группа элементов И и. второй элемент ИЛИ, причем инверсный выход каждого из триггеров запрета прерываний группы соединен с первым входом соответствующего элемента И группы, а информационный вход - с вторым входом соответствующего элемента И группы и соответствующим входом группы входов прерывания канала, сихронизирующий вход {саждого из триггеров запрета прерьшаний группы соединен с входом первого разряда группы синхронизирующих входов устройства, вход второго разряда группы синхронизирующих входов устройства соединен с одноименным входом второго триггера прерывания, ин формационньш и нулевой установочный входы которого соединены соответственно с выходом второго элемента

ИЛИ и входом подтверждения прерывания группы управляющих входов кана па,выходы элементов И группы соедин е- ны с соответствующими входами аторого элемента ИЛИ, выход второго триггера прерывания соединен с первым входом мажоритарного элемента, остальные входы которого

соединены с соответствующими входами группы входов подтверждения прерывания канала, выход формирователя соединен о соответствующим входом второго элемента ИЛИ, группа выходов

блока магистральных элементов и выход третьего элемента И в каждом канале являются соответственно группой выходов вектора прерывания и выходом разрешения прерьшания устройства, выход мажоритарного элемента в каждом канале является выходом прерывания устройства, выход формирователя импульсов является выходом прерывания канала, выход второго

триггера прерывания является выходом подтверяф ения прерывания канала, выходы прерывания и подтверждения прерывания каждого канала соединены с соответствующими входами одноименных групп

входов каждого из остальных каналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прерывания резервированной вычислительной системы | 1991 |

|

SU1824636A1 |

| Устройство для контроля резервированной системы | 1984 |

|

SU1256028A1 |

| Устройство для формирования сигналов прерывания | 1986 |

|

SU1341640A1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Микропрограммное устройство для обработки прерываний | 1983 |

|

SU1126956A1 |

| Трехканальная резервированная вычислительная система | 1983 |

|

SU1156273A1 |

| Устройство для обмена информацией | 1986 |

|

SU1322299A1 |

| Устройство для обслуживания запросов | 1985 |

|

SU1283768A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

Изобретение относится к вычислительной технике и может быть использовано в многоканальных резервированных микропроцессорных вычислительных системах для обработки прерываний. Цель изобретения - повы шение достоверности работы устройства за счет дополнительного введения второго и третьего каналов и в каждый канал двух триггеров запрета прерываний, второго триггера прерывания, мажоритарного элемента, двух элементов И и второго элемента ИЛИ. Устройство содержит первый канал, включающий регистр маски, регистр запросов, регистр текущего состояния, триггер запрета прерьшаний, триггер прерывания, шифратор приоритета, схему сравнения, блок элементов И, три элемента И, элемент ИЛИ, блок магистральных элементов и формирователь. Повышение достоверности достигается за счет обеспечения синхронного перехода системы в режим обработки прерывания при поступлении сигнала запроса хотя бы в одном канале, а также блокировки сигналов запросов прерьшаний, поступающих от каналов (процессоров) системы, которые постоянно (в режиме зависания) или стохастически формируют ошибочный сигнал запроса прерывания. 1 ил. i ю 00 со 00 ел

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Каган Б.И.,Сташин Б.Е | |||

| Микропроцессоры в цифровых системах, М.: Энергия, 1979, с | |||

| Деревянный коленчатый рычаг | 1919 |

|

SU150A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-03-15—Публикация

1984-09-28—Подача