I .

Изобретение относится к области автоматики и вычислительной техники, а именно, к функциональным преобразователям цифрового кода в аналоговую величину.

Известен функвдональный преобразователь, содержащий приемный регистр, селектор полярности, селектор тока, схему управления задержки, схему сравнения, двоичный счетчик it источник постоянного тока 1. Однако этот преобразователь имеет низкую точность преобразования.

Наиболее близким тех11ическим решением к данному изобретению .является программноуправляемый функциональный преобразователь, который содержит приемный регистр, вход которого является первым входом преобразователя, а выход соединен с первым входом блока формирователей сигналов диапазонов преобразуемого кода, подсоединенного вторым входом ко второму входу преобразователя, и блок генераторов тока с подключенным к нему блоком преобразователей тока в напряжение, выход которого является выходом преобразователя 2. Однако этот преобразователь

имеет невысокую тошость и малое быстро- действие.

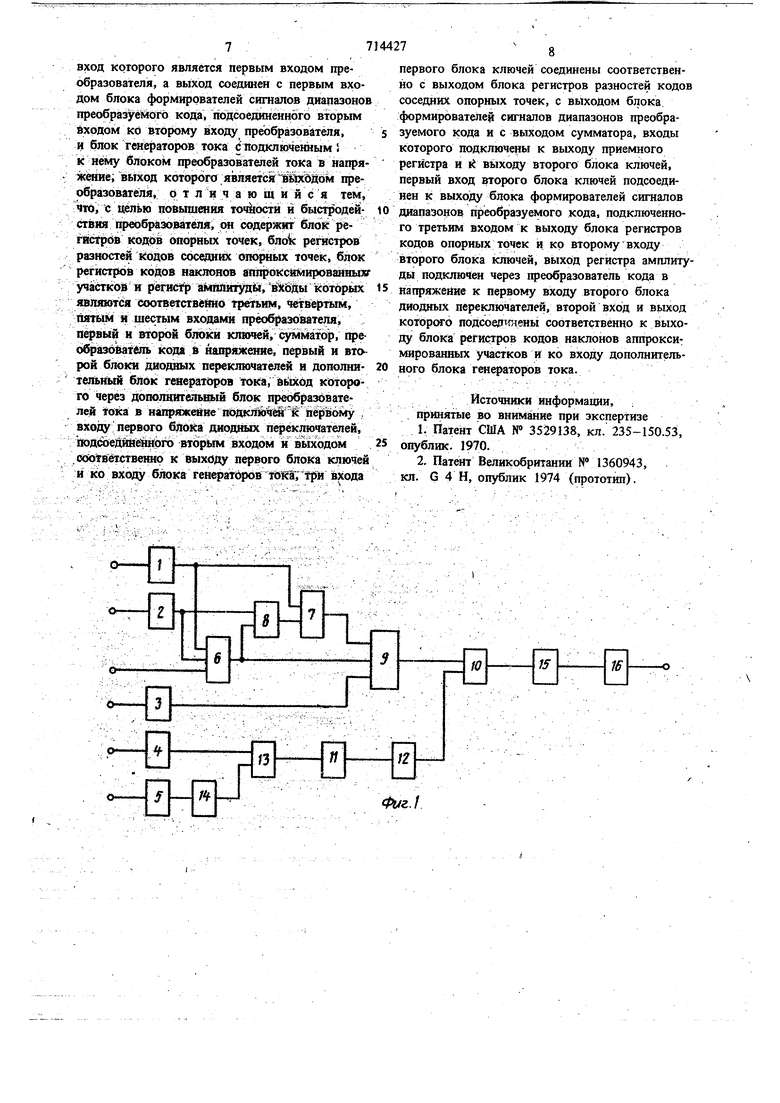

Целью данного изобретения является повышение точности и быстродействия преобразователя. Это достигается тем, что преобразователь содержит блок регистров кодов опорных точек, блок регистров разностей кодов соседних опорных точек, блок регистров кодов наклонов аппроксимированных участков и регистр амплтуды, входы которых являются соответственно третьим, четвертым, пяТым и шестым входами преобразователя, первый и второй блоки ключей, сумматор, преобразователь кода в напряжение, первый и второй блоки диодных переключателей и дополнительный блок генераторов тока, выход которого через дополнительный блок преобразователей тока в напряжение подключен к первому входу первого блока ДИОДЛЫХ1 переключателей, подсоединенного вторым входом и выходом соответственно к выходу первого блока ключей и ко входу блока генераторов тока, три входа первого блока ключей соединены соответственно с выходом блока регистров разностей кодов соседних опорных точек, с выходом блока формирователей сигналов диапазонов преобразуемого кода и с йьИходом сумматора, входы которого подключены к выходу приелтого регистра и к выходу второго блока ключей, первый вход второго блока ключей подсоединен к выходу блока формирователей сигналов диапазонов преобразуемого кода, подключенного третьим входом к выходу блока регистров кодов опорных точек и ко второму входу второго блока ключей, выход регистра амплитуды подключен через преобразователь кода в напряжение к первому входу второго блока диодных переключателей, второй вход и выход которого подсоединены соответственно к выходу блока регистров кодов наклонов аппроксимированных участков и ко входу дополнительного блока гёнерат6р1ов ±ока.

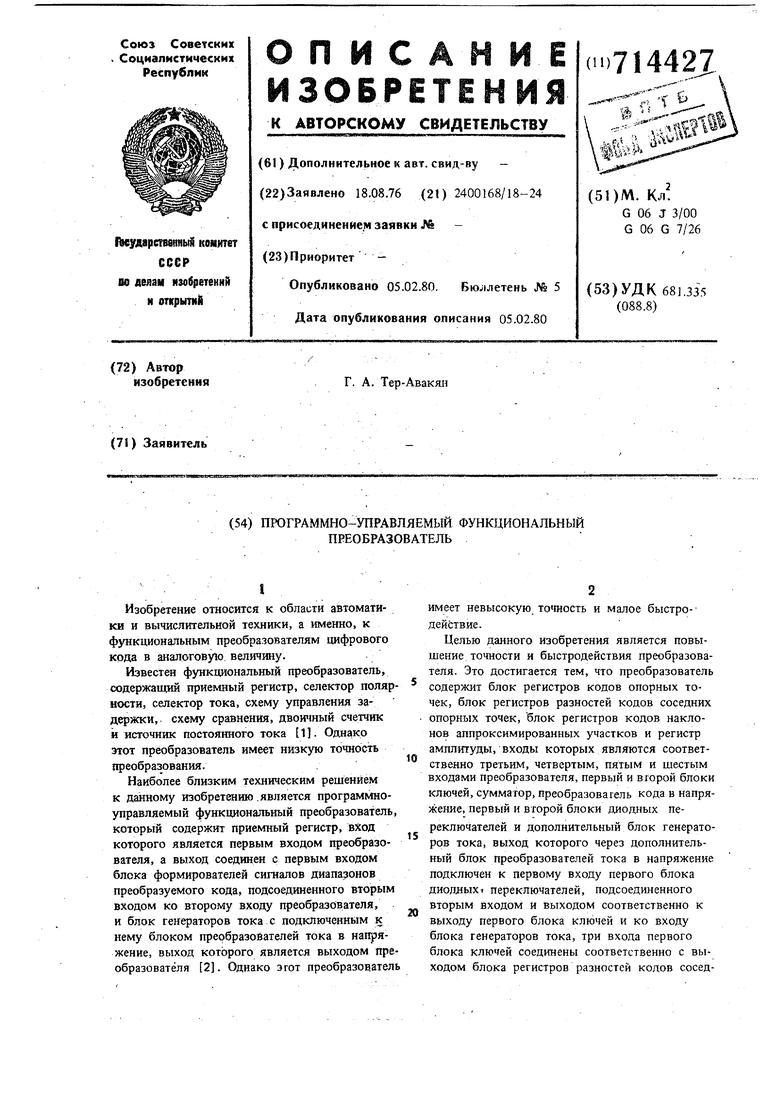

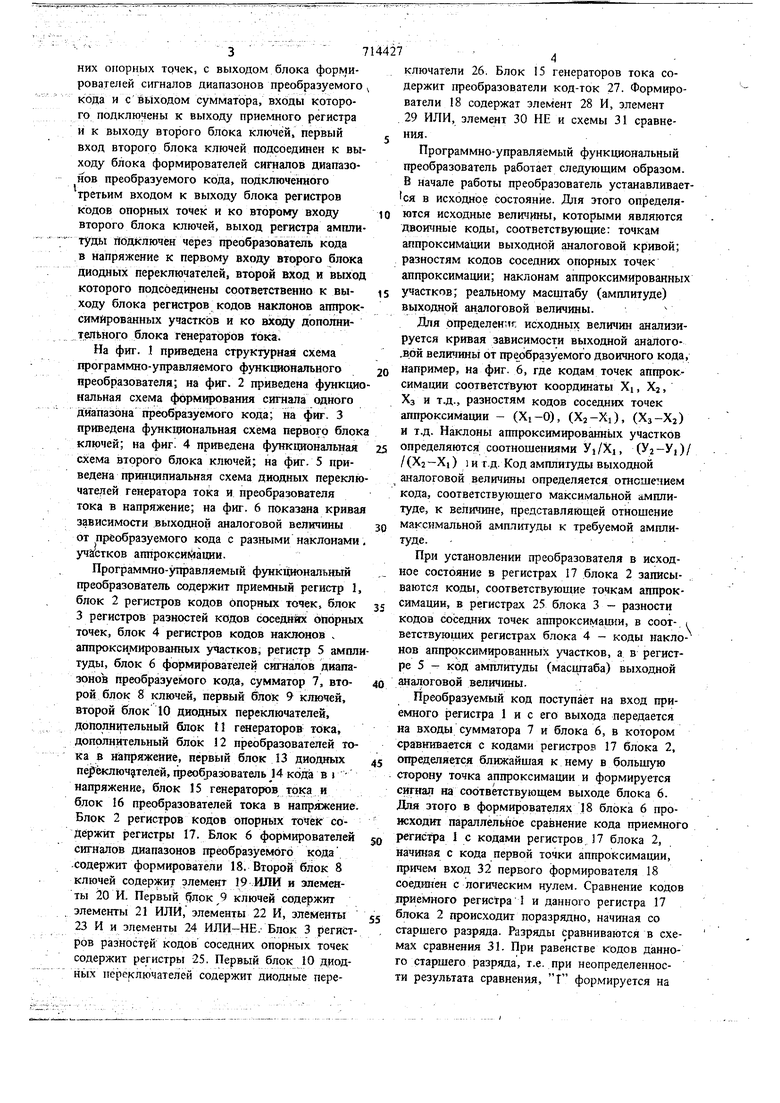

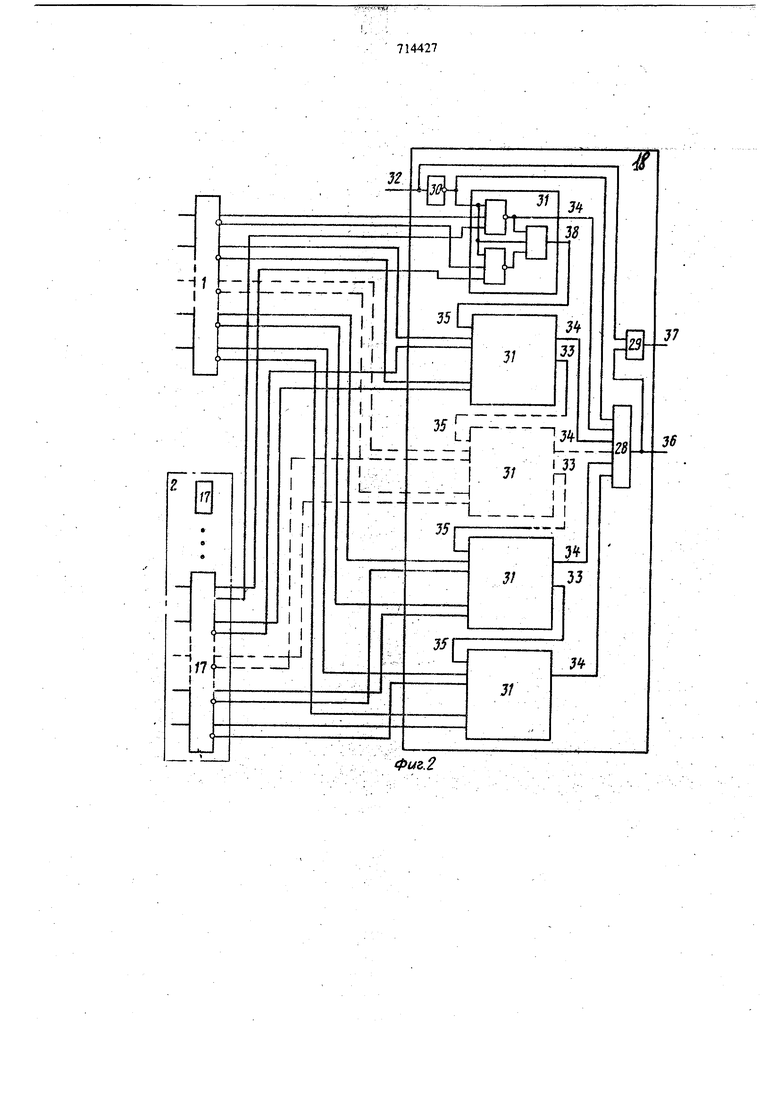

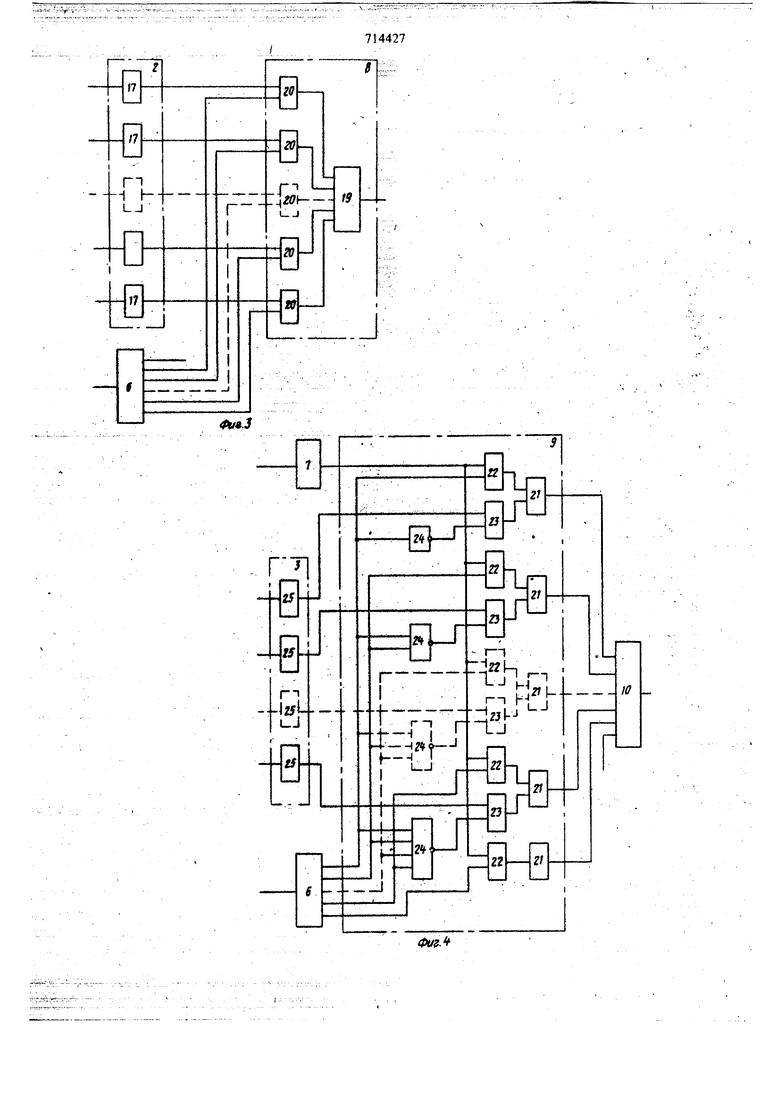

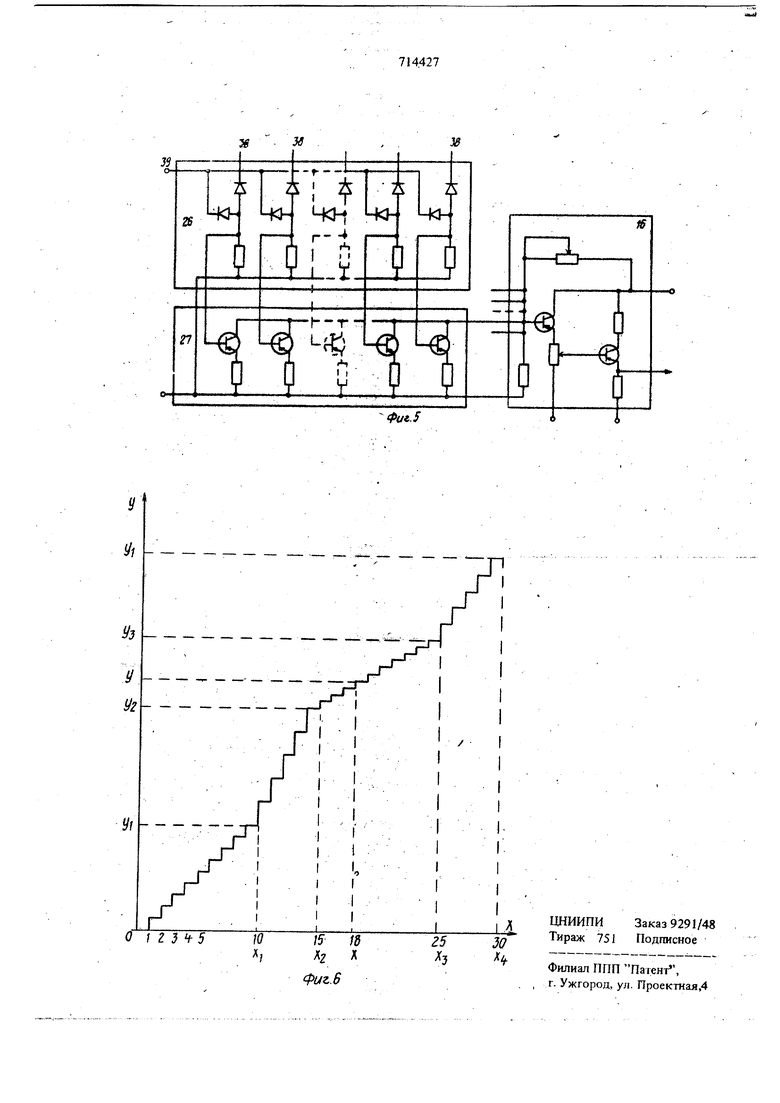

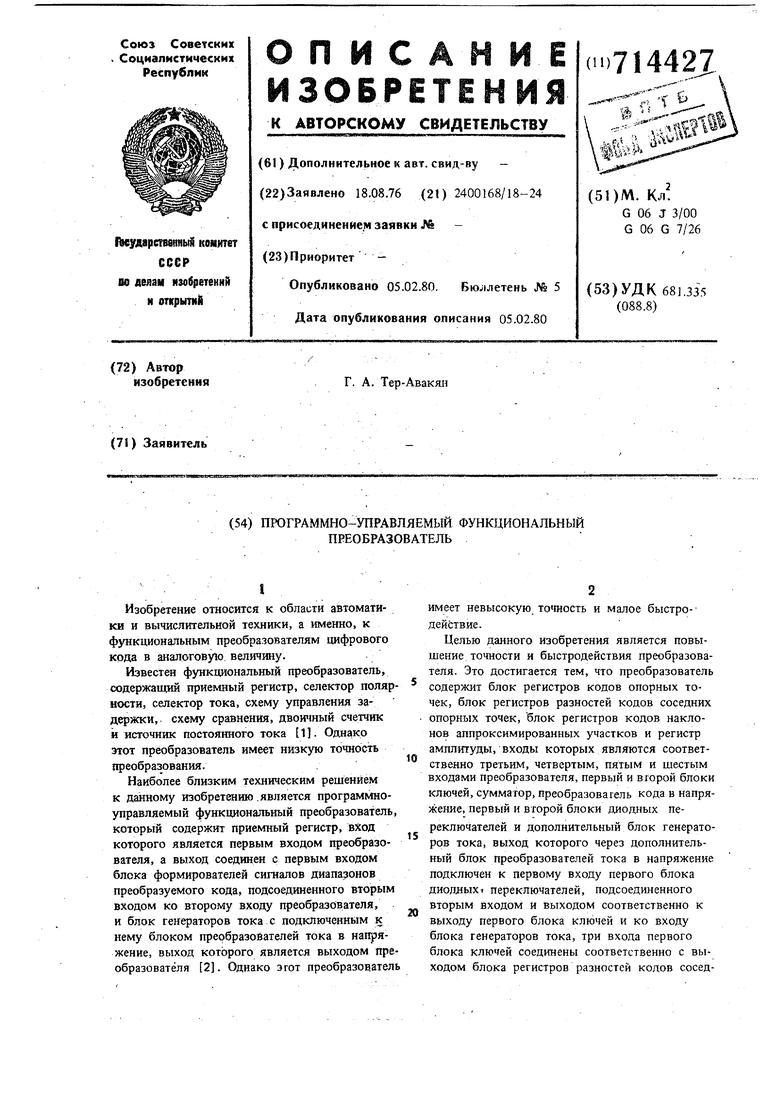

На фиг. 1 приведена структурная схема программно-управляемого функционального преобразователя; на фиг. 2 приведена функциональная схема формирования сигнала одного диапазона преобразуемого кода; на фиг- 3 приведена функциональная схема первого блок ключей; на фиг. 4 приведена функциональная схема второго блока ключей; на фиг. 5 приведена принципиальная схема диодных переключателей генератора тока и преобразователя тока в напряжение; на фиг. 6 показана кривая зависимости выходной аналоговой величины от преобразуемого кода с разными наклонами участков аппроксимации.

Программно-управляемый функциональный преобразователь содержит приемный регистр I, блок 2 регистров кодов опорных точек, блок 3 регистров разностей кодов соседних опорных точек, блок 4 регистров кодов наклонов . аппроксимированных участков, регистр 5 амплитуды, блок 6 формирователей сигналов диапазонов преобразуемого кода, сумматор 7, второй блок 8 ключей, первый блок 9 ключей, второй блок 10 диодных переключателей, дополнительный блок tl генераторов тока, дополнительный блок 12 преобразователей тока в напряжение, первый блок 13 диодных пе|1еключ9телей, преоб5)азователь 14 кода в г напряжение, блок 15 генераторов тока и блок 16 преобразователей тока в напряжение. Блок 2 регистров кодов опорных точек соДёржйт регистры 17. Блок 6 формирователей сигналов диапазонов преобразуемого кода -содержит формирователи 18. Второй блок 8 ключей содержит элемент 19 ИЛИ и элеыеаты 20 И. Первый блок 9 ключей содержит элементы 21 ИЛИ, элементы 22 И, элементы 23 И и элементы 24 ИЛИ-НЕ/ Блок 3 регистров разностгй кодов соседних опорных точек содержит регистры 25. Первый блок 10 диоднь|х переключателей содержит диодные переключатели 26. Блок 15 генераторов тока содержит гфеобразователи код-ток 27. Формирователи 18 содержат элемент 28 И, элемент 29 ИЛИ, элемент 30 НЕ и схемы 31 сравнения.

Программно-управляемый функциональный преобразователь работает следующим образом. В начале работы преобразователь устанавливается в исходаое состояние. Для этого определяются исходные величины, которыми являются двоичные коды, соответствующие: точкам аппроксимации выходной аналоговой кривой; разностям кодов соседних опорных точек аппроксимации; наклонам аппроксимированных участков; реальному масштабу (амплитуде) выходной аналоговой величины.

Для определение: исходных величин анализируется кривая зависимости выходной анаЛого.вой величинь от преобразуемого двоичного кода, например, на фнг. 6, где кодам точек аппроксимации соответствз от координаты Xi, Xj, Хз и т.д., разностям кодов соседних точек аппроксимации - (Xi -0), (Xj -Xi), (Хз -Х2) и т.д. Наклоны аппроксимированных участков определяются соотношениями Vi/Xj, (У2-У1)/ / (Х2 -Xi) 1 и т.д. Код амплитуды выходной аналоговой величины определяется отношетшем кода, соответствующего максимальной амплитуде, к величине, представляющей отношение максимальной амплитуды к требуемой амплитуде. -

При установлении преобразователя в исходное состояние в регистрах 17 блока 2 записываются коды, соответствующие точкам аппроксимации, в регистрах 25 блока 3 - разности кодов соседних точек аппроксимации, в соответствующих регистрах блока 4 - коды наклонов аппроксимированных участков, а в регистре 5 - код амплитуды (масцггаба) выходной аналоговой величины.

Преобразуемый код поступает на вход приемного регистра 1 и с его выхода передается на входы сумматора 7 и блока 6, в котором сравнивается с кодами регистров 17 блока 2, Определяется ближайшая к нему в большую сторону точка аппроксимации и формируется сигнал на соответствующем выходе блока 6. Для этого в формирователях 18 блока 6 происходит параллельАое сравнение кода приемного регистра I с кодами регистров 7 блока 2, начиная с кода первой точки аппроксимации, причем вход 32 первого формирователя 18 соединен с логическим нулем. Сравнение кодов лриемного регистра I и данного регистра 17 блока 2 происходит поразрядно, начиная со старшего разряда. Разряды сравниваются в схемах сравнения 31. При равенстве кодов данного старшего разряда, т.е. при неопределенности результата сравнения, Т формируется на

обоих выходах 33 и 34 схемы сравнения 31. С выхода 34 Т поступает на вход элемента И 28, а с выхода 33 - на разрешающий вход 35 последующей схемы 31 сравнения, в которой происходит сравнение кодов следующего разряда. Так продолжается до появления первого неравенства кодов очередного сра вниваемого разряда. Наличие Т в этом разряде приемного регистра Т и О в том же разряде регистра 17 свидетельствует о том, что код приемного регистра Т больще кода регистра 17 При этом образуется О на обоих выходах 33 и 34 схемы 31 сравнения этого разряда. Вследствие этого формируется О на обоих выходах 36 и 37 данного формирователя 18. С выхода 36 формирователя 18 О передается на соответствующий выход блока 6, свидетельствуя об отсутствии сигнала на этом выходе, а с выхода 37 поступает на вход 32 cneaytataft го формирователя 18 и разрешает в нем сравнение кода приемного регистра Т с кодом следующего регистра 17. Так продолжается дб появления неравенства, при котором имеется О в сравниваемом разряде приемного регистра Т и Т в том же разряде регистра 17, т.е. условия, что код приемного регисТ|ра Г меньше кода регистра 17. При этом возникает О на выходе 33 и Г на выходе 34 схем 31 сравнения как этого, так и всех последующих разрядов данного формирователя 18.

Таким образом, как прн равенстве кодов всех разрядов приемного регистра I и даяного регистра 17, так и когда код приемного ре- гистра Г меньще кода данного регистра 17, на выходах 34 всех схем 31 сравнения д нОго формирователя 18 формируются I, которые поступают на входы элемента 28 И и на его выходе создают Т, которая поступает выход 36, а также через элемент 29 ИЛИ на выход 37 данного формирователя 18. С выхода 37 Г поступает на вход 32 сЛедую щего формирователя 18, точнее - на Ьход элемента 29 ИЛИ, и обеспечивает Г на выходе 37 и О на входе элемента 28 И, вследствие чего на выходе 36 формирователя 18 формируется О. Аналогично, Т с выхода 37 каждого следующего формирователя 18 поступает на входы 32 последующих формирователей 18 и формирует О на его выходах 36 и 1 на выходах 37.

Таким образом, Т формируется на виходе только одного формирователя 18, а именно, того, который связан с регистром 17, содержащим код ближайшей в большую сторону относительно кода приемного регистра Т (или равной ему) точки аппроксимащ1н. Эта I поступает на соответствующий выход блока 6 формирователей сигналов диапазонов преобразуемого кода, на остальных выходах которого .

Сигнал с выхода блока 6 поступает на соответствующий вход блока 8 ключей (фиг. 3) и разрешает передачу кода предыдущей точки аппроксимации, который с выхода блока 8 поступает на вход сумматора 7 и в нем вычитается из преобразуемого кода, поступающего на другой вход сумматора 7 с выхода приемного регистра Г. Полученная разность с выхода сумматора 7 поступает на вход блока 9 ключей..

Сигнал с вьЬсода блока 6 поступает также на соответствующий вход блока 9 (фиг. 4),

чем обеспечивается разрешение вьвдачи на информащюнные входь 38 соответствующих диодных переключателей 26 (фиг 5) блока 10 разностей кодов предыдущих смежных точек аппроксимации (относительно преобразуемого

кода) с выходов регистров 25 блока 3 и разности преобразуемого кода и кода предьздущей смежной точки с выхода сумматора 7 (Xi, Xj-Xi, X-Xj на фиг. 6).

Передача кодов на остальные информационные входы блока 10 запрещается, вследствие чего на них поступают нули.

На управляющие входы 39 диодных переключателей 26 блока 10 с выходов блока 12 поступают соответствующие кодам регистров

блока 4 напряжения, определяющие наклоны участков аппроксимации выходной аналоговой кривой. Уровни сигналов, соответствующие коду Xi, в нервом диодном переключателе 26 блока 10 умножаются на соответствующий управляющему напряжению, (определяемому кодом регистра блока 4) к оэффициент и передаются на входы первого преобразователя кодток 27, в котором преобразуются в ток, соответствующий коду Xj, умноженному на указанный коэффи1щент. Этот ток с выхода первого преобразователя код-ток 27 поступает на соответствующий вход блока 16 и переводам рабочую точку (напряжение на выходе блока 16) в У. Таким же образом код Xj-Xj создает

на выходе второго преобразователя код-ток 27 блока 15 ток, который поступает на вход блока 16 и, сумм1фуясь с его током, переводит рабочую точку с У в УЗ. Аналогично, код Х-Х2 переводит рабочую точку с УЗ в У.

Масщтаб выходаой аналоговой кривой определяется кодом регистра 5, вследствие того, что напряжения на выходах блока 12, соответствующие кодам регистров блока 4, умножаются описанным вьпие образом на коэффициент,

определяемый кодом регистра 5.

Формутга изобретения

Программно-управляемый функциональный

преобразователь, содержащий приемный регистр.

вход которого является первым входом преобразователя, а выход соединен с первым входом блока формирователей сигналов диапазонов преобразуёйогЧ) кода, подсоеданенного вторым входом ко второму входу пр&образоватёля, и блок reHiepaTopoB тока бподклнменным к нему блоком преобразователей тока в напря жеяие; выход которого являетЬяШ1хЩ{)м преобразователя, о т л и чаю щ ни с я тем, Что, с целью повыша1ия точности и быс:фодействкя преобразо)аатёля, он содерЖ1гт Gndtt рбгйстрбв кодов опорных точек, бло1к регистров разностей кодов соседних опорных точек, блок регистров кодов наклонов аппр оКсйМировайныхг участков к регистр ампйигудЁг, ШЩы которых являются ч;оответств ;йно третьим, Четвфтым, пятым и шестым входами преобразователя, первый и второй блоки ключей, cyMMatfipi преобразЬШбль кода б напрюкение, первый и блою{ диодных переключателей и дополнительный блок генераторов тока, которого через допрлнительоый блок преббразОвателей тока: в напряжение яЬДклк|Ш к1 1ёрсййу ; Bxoj первого блока диодных переключателей, ск дюе №еннОго вторьгм входом и вь1ходом сск)Твётственно к выходу первого блока ключей и ко входу блока генераторов it KSVtf H входа

первого блока ключей соединены соответственно с выходом блока регистров разностей кодов соседних опорных точек, с выходом блока формирователей сигналов диапазонов преобразуемого кода и с выходом сумматора, входы которого подключены к выходу приемного регистра и и выходу второго блока ключей, первый вход второго блока ключей подсоединен к выходу блока формирователей сигналов

диапазонов преобразуемого кода, подключенного третьим входом к выходу блока регистров кодов опорных точек и ко второму входу второго блока ключей, выхОд регистра амплитуды подключен через преобразователь кода в напряжение к первому входу второго блока диодных переключателей, второй вход и вькод которото подсоертаены соответственно к выходу блока регистров кодов наклонов аппроксимированных участков и ко входу дополнительного блока генераторов тока.

Источники информации, ; фИнятые во вним;шие при экспертизе

1.Патент США № 3529138, кл. 235-150.53, опублшс. 1970.

2.Патент Великобритании N 1360943, кл. G 4 Н, опублик 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления показательной функции | 1981 |

|

SU981997A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1730722A2 |

| Функциональный преобразователь | 1983 |

|

SU1166147A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Цифро-аналоговый функциональный преобразователь | 1977 |

|

SU734748A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Преобразователь код-напряжение с широтноимпульсной модуляцией | 1978 |

|

SU790283A1 |

| Устройство для измерения параметров газовых сред | 1980 |

|

SU894527A1 |

| Аналого-цифровой преобразователь | 1991 |

|

SU1800617A1 |

| Преобразователь аналоговых величин в код | 1979 |

|

SU924855A2 |

Авторы

Даты

1980-02-05—Публикация

1976-08-18—Подача