опорных сигналов является вторым входом квантователя сигналов, вторые входы первого и второго интеграторов объединены и являются третьим входом квантователя сигналов, выход вычита еля является выходом квантователя сигналов. -.. 3. Устройство по п. 1, отличающееся тем, что блок управления выдачей информации содержит ключи, сумматоры, вычитатель и преобразователь кода, выход преобразователя кода соединен с первыми входами первого, второго, третьего и четвертого ключей, выхода первого и второго ключей соединены через соответствующие первый и второй су 1маторы с первь&4 И вторым входами третье16 го сумматора, выходы третьего и четвертого ключей соединены через соответствующие четвертый и пятый сум-, маторы с первым и вторым входами нестого сумматора, выходы третьего и шестого сумматоров соединены соответственно с первым и вторым входами вычитателя, первый вход преобразователя кода, объединенные вторые входы первого и второго ключей, объединенные -вторые входы третьего и четвертого ключей и второй вход преобразователя кода являются соответственно первым, вторым, третьим и четвертым входами блока управления вьщачей информации, выход вычитателя является выходом блока управления вьщачей информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования избыточных кодов | 1983 |

|

SU1105927A1 |

| Устройство для приема избыточной информации | 1981 |

|

SU1029205A1 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство для приема избыточных сигналов | 1983 |

|

SU1107145A1 |

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152017A2 |

| Устройство для приема избыточной информации | 1981 |

|

SU1001147A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1101873A1 |

| Некогерентный приемник | 1981 |

|

SU1003370A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

| Устройство для приема избыточной информации | 1988 |

|

SU1557578A2 |

1. УСТРОРЛСТВО ДЛЯ ПРИЕМА И ГРАДИЕНТНОГО ДЕКОДИРОВАНИЯ ИЗБЫТОЧНЫХ СИГНАЛОВ, содержащее квантователь сигналов, первый вход которого является входом устройства, второй вход подключен к первому выходу хронизатора, выход квантователя сигналов соединен с входом аналого-цифрового преобразователя, выходы которого соединены с соответствующими первыми входами первого блока памяти, выход первого блока памяти соединен с первыми входами первого порогового блока, блока управления выдачей информации и вычитателя, выход первого порогового блока соединен с первым входом декодера и вторым входом вычитателя, сумматор, выход которого соединен с входом второго порогового блока, выход декодера соединен с первьм входом второго блока памяти, первый, второй выходы и в-Горой вход которого подключены соответственно к второму, третьему входам и к выходу блока управления вьщачей информации, третий выход второго блока памяти является вькодЬм устройстваJ отличающееся тем, что, с целью упрощения устройства, вр11ход первого блока памяти и вьгход вычитателя соединены соответственно с первым и вторым входами сумматора, выход второго порогового блока соединен с первым входом регистра, выход регистра соединен с вторым входом декодера, вто7 рой, третий, четвертый, пятый, шестой, седьмой, восьмой, девятьй, десятьй, одиннадцатый и двенадцатый выходы хронизатора соединены соответственно с третьим входом квантователя сигналов, с вторым, третьим входами первого блока памяти, с объединенными вторым входом первого порогового блока и трет.ьйми входами СО вычитателя и сумматора, с третьим С входом декодера, с третьим, четвертым, пятым, шестым входами второго блока памяти, с четвертым входом блока управления выдачей информации и с вторым входом регистра. ЬвА 2. Устройство по п. 1, о т л и чающееся тем, что квантовасл чд тель сигналов содержит умножители, интеграторы, генератор опорных сигналов и вычитатель, первый и второй выходы генератора опорных сигналов Oi соединены с первыми входами соответственно первого И второго умножителей, выходы которых соединены с первьпуи входами соответственно первого и второго интеграторов, выходы первого и второго интеграторов соединены соответственно с первым и вторым входами вычитателя, вторые входы первого и второго умножителей объединены и являются первым входом квантователя сигналов, вход генератора .

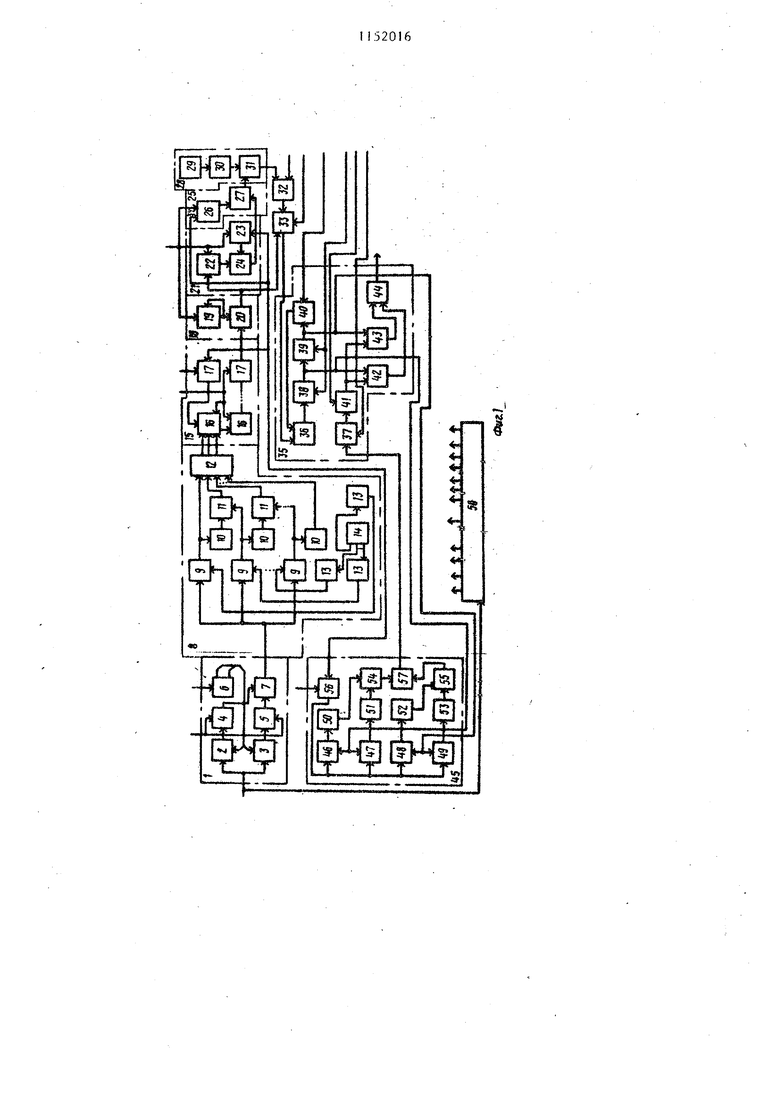

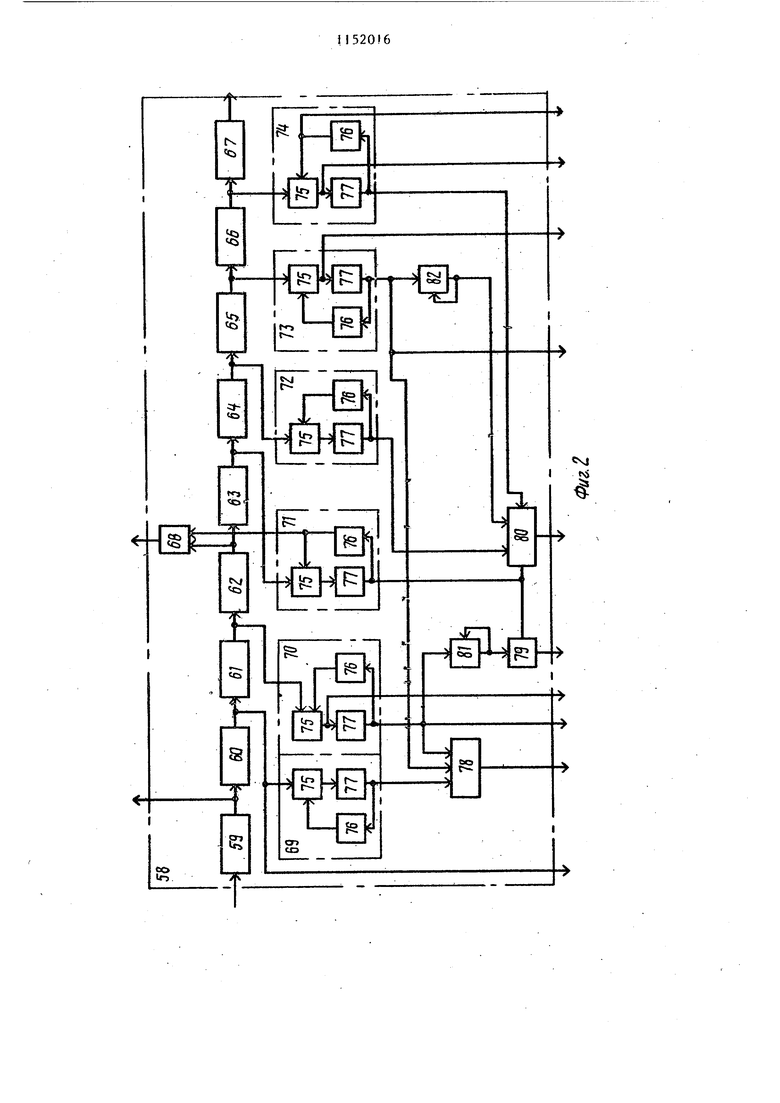

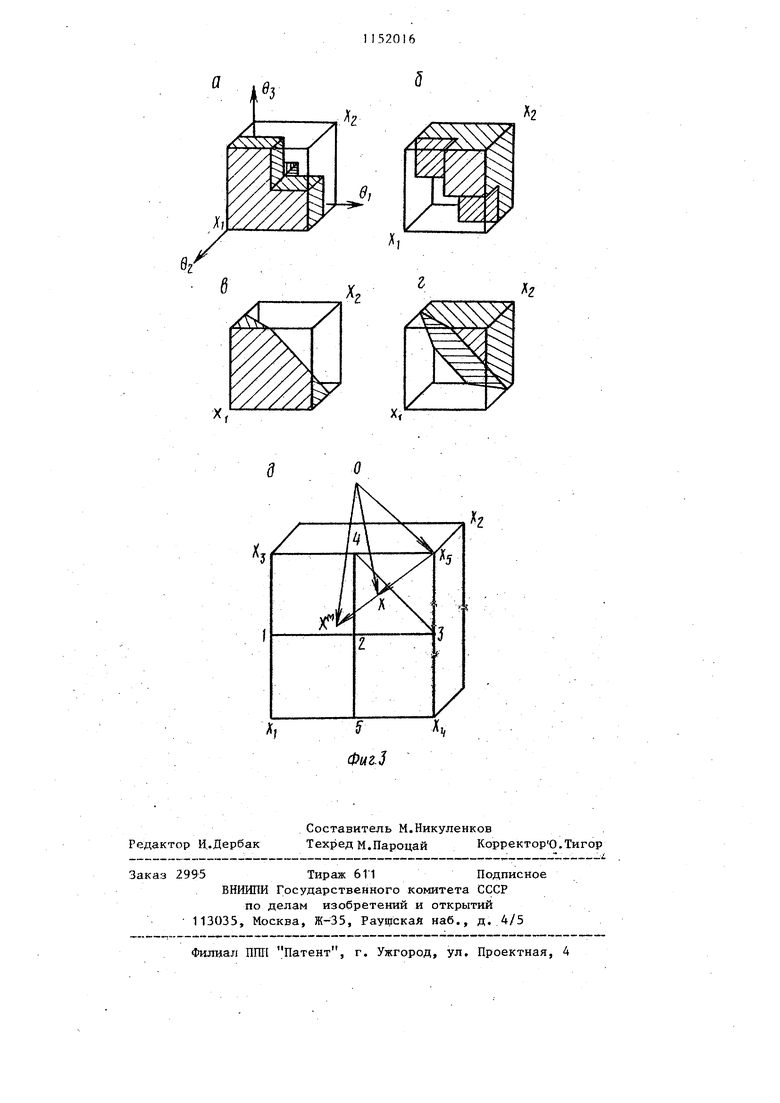

Изобретение относится к электросвязи и может быть использовано в Приемных устройствах систем передачи телеметрической информации, испо ЗУющих длинные и сверхдлинные помехоустойчивые коды. Известно устройство дЛя приема (избыточной информации, содержащее„ приемник, пороговый блок и декодер Щ Недостатком данного устройства является низкая помехоустойчивость, поскольку в нем не учитывается апос териорная информация об амплитуде символов аналогового сигнала на выходе приемника. Наиболее близким к изобретению по технической сущности является устройство для приема и градиентного декодирования Избыточных сигНа лов, содержащее квантователь сигналов первый вход которого являетс входом устройства, второй вход подключен к выходу хронизатора, выход квантователя сигналов соединен с входом аналого-цифрового преобразоватепя, выходы которого coeдиkeны с соответствующими входами первого блока памяти, выход первого блока памяти соединен с входами первого порогового блока, блока управления вьщачей информации и вычислителя. выход первого порогового блока Соединен с первым входом декодера и вторым входом вычитателя и через регистр - с первым входом суммйтора, выход вычитателя подключен через последовательно соединенные второй блок памяти и блок сдвига к второму входу сумматора, выход сумматора соединенчерез второй пороговый блок с вторым входом декодера, ход декодера соединен с первым входом третьего блока памяти, первый, второй выходы и второй вход которого подключены соответственно к второму, третьему входам и к выходу блока управления вьщачей информации, третий выход третьего блока памяти является вьгходом устройства. Известное устройство обеспечивает высокую помехоустойчивость приема избыточных сигналов, дает возможность осуществлять прием в целом сложных сигналов на основе избыточных кодов . Недостатками известного устройства являются его сложность, обусловленная наличием блока сдвига и второго блока памяти, а также в случае использования устройства в высокоскоростных системах передачи информации для работы блока сдвига требуется высокая тактовая частота, что снижает -надежность функционирования устройства. Цель изобретения - упрощение уст ройства за счет исключения второго блока памяти и блока сдвига. Указанная цель достигается тем, что в. устройстве для приема и градиентного декодирования избыточных сигналов, содержащем квантователь .сигналов, первый вход которого явля ется входом устройства, второй вход подключен к первому выходу хронизатора, выход квантователя сигналов соединен с входом аналого-цифрового преобразователя, выходы которого соединены с соответствующими первыми входами первого блока памяти, выход первого блока памяти соединен с первыми входами первого порогового блока блока-управления вьщачей информации и вычитателя, выход первого порогового блока соединен с первым входом декодера и вторым входом вычи татепя, сумматор, выход которого сое динен с входом второго порогового блока,, выход декодера соединен с пер вым входом второго блока памяти, первый, второй выходы и второй вход которого подключены соответственно к второму, третьему входам и к выходу блока управления выдачей информации, , тр.етий выход второго блока памя ;ти является выходом устройства, выход первого блока памяти и выход вычитателя соединены соответственно с первым и вторым входами сумматора, выход второго порогового блока соединен с первым входом регистра, выхо регистра соединен с вторым входом декодера, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатьш и двенадцатый выходы хронизатора соединены соответственно с третьим входом квантователя сигналов, с вторым, i третьим входами первого блока памя;ти, с объединенными вторым входом первого порогового блока и третьими входами вычитателя и сумматора, с третьим входом декодера, с третьим, четвертым, пятым, шестым входами второго блока памяти, счетвертым входом блока управления.вьщачей информации и с вторым входом регистра Кроме того, квантователь сигналов Содержит умножители, интеграторы, генератор опорных сигналов и вы164читатель, первый и второй ниходы генератора опорных сигналов соедине ны с первыми- входами соответственно первого и второго умножителей, выходы которых соединены с первыми входами соответственно первого и второго интеграторов, выходы первого и второго интеграторов соединены соответственно с первым и вторым входами вычитателя, вторые входы первого и второго умножителей объединены и являются первым входом квантователя сигналов, вход генератора опоряых сигналов является вторым входом квантователя сигналов, вторые входы первого и второго интеграторов объединены и являются третьим входом .квантователя сигналов, выход вычитаТтеля является выходом квантователя сигналов. При этом блок управления выдачей информации содержит ключи, сумматоры, вычитатель и преобразователь кода, выход преобразователя кода соединен с первыми входами первого, второго, тре.тьего и четвертого , выходы первого и второго кЛю- чей соединены через соответствующие первый и второй сумматоры с первым и вторым входами тр-етьего сумматора, вькоды третьего и четвертого ключей соединены через соответствующие четвертый и пятый сумматоры с пер- вторым входами шестого сумматора, вькоды третьего и щестого сумматоров соединены соответственно с первым и BTopbiM входами вычитателя, первый вход преобразователя кода, объединенные вторые входы первого и второго ключей, объединенные вторые входы третьего и четвертого ключей и второй вход преобразователя кода являются cooTBeTctseHно первым вторым, третьим и четвертым входами блока управления -выдачей информации, выход вычитателя является выходом блока управления выдачей информации. На фиг. 1 представлена структурная схема устройства для приема и обработки избыточных сигналов ; на фиг. 2 - структурная схема хронизатора; на фиг.. 3 - геометрическое изображение алгоритма работы предлагаемого устройства. Устройство для приема и градиентного декодирования избыточных сигналов (фиг. 1) содержит квантователь 1 сигналов, вьшолненньш на уиножителях 2 и 3, интеграторах А и 5, генераторе 6 опорных сигналов .и тателе 7, аналого-цифровой преобразователь 8 выполненный на пороговых элементах 9, элементах 10 НЕ, элементах 11, шифраторе 12, аттенюаторах 13 и источнике 14 пороговых напряжений, &ЛОК 15 памяти, выполненный на регистрах 16 и ключе 17, пороговый блок 18, выполненный на регистре 19 сдвига и ключе 20, вюти татель 21, вьтолненный на двоичнодесятичных преобразователях 22 и 23 кода и элементе 24 вычитания, сумма тор 25, выполненный на двоично-деся тичном преобразователе 26 кода и элементе 27 сложения, пороговый блок 28, выполненный, на источнике 29 порогового напряжения, аттенюато ре 30 и пороговом элементе 31, регистр 32 сдвига, декодер 33 и 34,: блок 35 памяти, вьяшлненньй на элементе 36 ИЛИ, триггере 37, регистра 38 и 39 сдвига, ключах 40-43 и элементе 44 ИЛИ, блок 45 управления выдачей информации, вьтолненный на ключах 46-49, сумматорах 50-55, двоично-десятичном преобразователе 56 кода и вычитателе 57, и хронизатор 58. Хронизатор 58 (фиг. 2) содержит формирователь 59 импульсов, элемент 60-67 задержки,.- элемент 68 ИЛИ, фор мирователи 69-74 тактовых импульсов казедый из которых вьшолнен на тригг ре 75, счетчике 76 и генераторе 77 тактовых импульсов, элементы 78 80 ИЛИ иделителу 81 и 82 частоты на три. Устройство работает следунлдим образом. Рассмотрим алгоритм функционирования предлагаемого устройства „ Пусть осуществляется формировани составного сигнала с избыточностью на основе комбинаций двоичного трех значного кода с тотнимальным кодовым расстоянием с5 - 3, для которого раз решеннь ми кодовьа ш комбинациями я.вляются Х 101 и Х2 010. Составной избыточный сигнал после прохожд ния канала связи, в котором на него воздействуют помехи, с помощью кван тователя 1 сигналов преобразуют в -аналоговый сигнап. На фиг. 3 в виде куба изображено множество сигнальных точек, соотвпт 16 ствующих аналоговым сигналам X на. выходе, квантователя 1 сигналов, Вершины куба соответствуют кодовым комбинациям. Каждое ребро куба определяет единичное хэммингово расстояние между теми вершинами (кодовыми комбинациями), которые данное ребро соединяет; На фиг. 3 а штриховкой выделена область сигнальных точек, которые отождествляются с разрешенной кодовой комбинацией X, при посимвольном приеме; на.фиг. Зй- то же, при приеме в делом. Соответственно для разрешенной кодовой комбинации Xj ,на фиг..36 штриховкой вьщелена область сигнальных точек, отождествляемых с данной комбинацией при посимвольном приеме иа фиг. Зг - то же, при приеме в целом,. Из сравнения фиг. 3 а с 3 в и фиг, 3 б с 3 г следует, чТб отличие посимвольного приема от приема в целом заключается в отличии границ областей отождествления. Совместим области отождествления при посимвольном приеме и при приеме в целом для комбинащ и Xj и рассмотРИМ переднюю грань (квадрат) Х(-Зз- куба. Множество сигнальных точек X -Xj-4-2-3-Зц на этой грани отозкдествляются с X при посимвольном приеме. Множество сигнгшьнык точек Х -Хз-4-3-Х на передней грани куба отождествляются с Х при приеме в целом. .Отличие приема в целом от посимвольного приема, в частности, состоит в наличии сигнальных точек, принадлежащих треугольнику 1-4-3. Характерной особенностью сигнальных точек данной области является то, что при посимвольном приеме они отождествляются с разрешенной комбинацией Xj, так как она принадлежит заштрихованной области на фиг. 36. В случае приема в целом сигнальные точки из треугольника 2-4-3 отождествляются с разрешенной кодовой комбинацией Х(. Геометрические модели достаточно точно иллюстрируют существо отличия алгоритма посимвольной обработки составных сигналов с избыточностью, формируемых на основе кодов произвольной значимости, от алгоритма приема в целом. В общем случае также существуют такие области сигнальных точек, кот рые при приеме в целом правильно отождествляются с разрешенными кодовыми комбинациями, а при посимвол ном приеме - ошибочно. Но в отношении этих областей можно отметить,что их сигнальные точки отождествляются -с ближайшей к истинной (с вероятностью правильного приема при обработке в целом) разрешенной кодовой комбинацией. Это утверзкдение находится в полном соответствии с моделью на фиг. 3 д. Принцип действия известйого устройства заключается в том, что сигнальные точки из треугольника 2-4-3 вб1засываются в область посимвольного приема для Х(. Осуществляетсяуй-азанное вбрасывание следуюпртм образом. Посимвольный приём предполагает осуществление трех основных операций. - , Первая операция называется анало говой демодуляцией. Она реализуется в квантователе 1 сигналов. Вторая операция - однопороговое квантование и реализуется с помощью аналого-цифрового преобразователя 8 На фиг. Зд с помощью указанных операций сигнальные точки квадрата Х|-1-2-5 отождествляются с двоичной кодовой комбинацией (в данном слу,чае разрешенной) X), Сигнальные точки квадрата Xj-4-2-1 соответстве Но с двоичной кодовой комбинацией а сигнальные точки квадратов Xj - 3-2-4 и Х. - 3-2-3 соответст. венно отождествляются с X j- и Х-}.. Третья операция называется декод рованием. С ее помощью двоичные код . вые комбинации по соответствующему критерию .отождествляются с разрешен ными двоичными кодовыми комбинациями. Данная операция реализуется с помощью декодера 33. Например, в ре зультате выполнения операции декоди рования в Соответствии с критерием 1аксимального правдоподобия с разрешенной комбинацией Х (фиг. Зд) отождествляются комбинации Xj и Х, Комбинация Ху отождествляется с раз решенной кодовой комбинацией Х. . Согласно градиентному декодирова нию в .ц -мерном пространстве вычисляют вектор Х5.Х, считая при этом, что сигнальная точка X попала в тре угольник 2-4-3. Для этого вычисляют разность между вектором ОХ И ОХ. (точка О - условное изображение начала координат п -мерного пространства) . Результат - вектор усиливают до тех пор, пока его .конец не попадет в область посимвольного приема для X, (фиг. За). В блоке 35 памяти осуществляется накопление составляющих сигна;ла Х,..Х, которьЕй с помощью блока сдвига усиливают в указанном направлении до заданной величины. Из выводов структурного анализа и из геометрических моделей (фиг Зд) следует, что для любой сигнальной точки X из треугольника 2-4-3.(за исключением линии - границы треугольника, для которой вероятность совпадения с сигнальной точкой близка к нулю (расстояние до линии 4-3 меньше расстояния до Х). Из этого следует, что при увеличении величины сигнала ХуХ в два раза конец вектор-а 2Х5Х будет попадать в область X -Xj-4 2-3-Хи посимвольного приема для Х. Решение при этом будет ошибочным только в том случае, если сигнальная точка X будет принадлежать линии 4-3, как и при приеме в целом. Из данного факта вытекает, что основное преимущество алгоритма функционирования известного устройства определяемое расширением области посимвольного приема до величины области приема в целом ив предлагаемом устройстве сохраняется. Отличие заключается в том, что вектор XfX всегда усиливают в два риза. Теоретически данная операция вытекает из метода теории оптимизации, ргспользующего вторые производные, и квадратичной целевой функции. В предлагаемом устройстве достаточно покоординатно, т.е. посимволы -но к радиусу-вектору ох сигнальной точки X прибавить вектор XX, который следует выбрать равным и по величине и по направлению . Получаемый в результате век1ор сигнальной точки X после посимвольной .об-, работки приводит к X .в остальном алгоритм функционирования предлагаемого устройства не отличается от алгоритма функциониования известного устройства, Т.е. ля устранения Неопределенности относительно того попала сигнальная

911

точка в треугольник 2-4-3 или нет после вьтолнения операции декодирования для X у и Xj определяют степени, близости (коэффи1щенты корреляции) между X и Xj (в результате-декодирования Х) и между X и Х (результат декодирования Xj). Выходной считают ту из разрешенных комбинаций, для которой степень близости больше, например в рассматриваемом случае расстояние от X до X. меньше, чем от X до Xj.

Таким образом, в предлагаемом .устройстве вместо большого количества операций по усилению вектора ХуХ, хранящегося во втором блоке памяти известного устройства, используют одну операцию - покоординатное сложение ОХ и ХуХ.

Квантователь 1 сигналов осуществляет преобразование входного элементарного канального сигнала в импульс постоянного тока определенной амплитуды так, что входной сложный сигнал с -его помощью преобразуется в совокупность из ц последовательных импульсов различной амплитуды, которая определяет аналоговый составной сигнал X .

На входе 1 квантователя 1 сигналов поступает управляющий сигнал от хронизатора 58, которьй запускает генератор 16 опорных сигналов. На входы умножителей 2 и 3. с входа устройства поступает канальный сигнал. В умножителях 2 и.З канальный сигнал перемножается с соответствующими опорными сигналами, вырабатываемьпуги генератором 6. Выходные сигналы умножителей 2 и 3 накапливаются в интеграторах 4 и 5, от хронизатора 58 на интеграторы 4 и 5 поступает управляющий сигнал, по которому с интеграторов 4 и 5 снимаются сигналы в виК& импульсов постоянного тока определенной амплитуды. Выходные сигналы интеграторов 4 и 5 вьгчитаются в вйчитателе 7, вследствие чего образуется развостный сигнал, представляемьй также им1тульсом постоянного тока олределенНой амплитуды.

Таким образом, выходной канальньш .сигнал преобразуется в выходной импульс постоянного тока соответствующей амплитуды, которая определяет степень искажения входного сигнала.

Импульсы постоянного тока подаются на входы пороговых элементов 9,

10

16

в которых их амплитуда сравнивается с амплитудами пороговых напряжений, поступающих на вторые входы пороговых элементов 9. В результате сравнения на выходах тех пороговых элеметов 9, для которых амплитуда входного импульса превышает амплитуду соответствующего порогового напряжения, появляются сигналы.

Рассмотрим несколько примеров прербразования. Пусть амплитуда входного импульса равна нулю. Тогда на выходах всех пороговых элементов 9 управляющие сигналы появляться не будут. Поэтому на выходе первого элемента 11 и на первом входе шифратора 12 будет присутствовать едини ньй сигнал, .а на выходах остальных элементов 11 И - нулевые сигналы Тогда на остальных входах шифратора 12 - нулевые сигналы. Совокупность входных сигналов шифратора 12 - двоичная кодовая комбинация еди ничного веса, в которой единичный символ находится на первой позиции. С помощью шифратора 12 эта комбинация преобразуется в выходную двоичную кодовую комбинацию, значность которой f Eog, тПСздесь т количество зон квантования). Если амплитуда входного импульса превышает только амплитуду первого порогового уровня, то единичный сигнал появится только на втором входе шифратора 12. Если амплитуда входного импульса превмиает амплитуду и первого и второго пороговых уровней, то единичный сигнал появится только на третьем входе шифратора 12. При превышении входным сигналом амплитуды самого большого (hn- 1) порогового импульса, единичньй сигнал появляется только на входе шифратора 12.

Блок 15 памяти предназначен для хранения двоичной кодовой комбинации формируемой в преобразователе 8, Она состоит из п. л) -разрядных двоичных кодовых комбинаций. В состав блока 15 входит открытый в исходном состоянии ключ 17, который закрывается по управляющему сигналу из хронизатора 58.. Двоичная кодовая комбинагщя из преобразователя 8 записывается в nej)вый регистр 16. Следующая двоичная комбинация, записываясь в первый регистр 16, выталкивает первую комбинацию во второй регистр 16. Третья кодовая комбинация передвигает вторую 11 и первую комбина1 ;ию соответственно во второй и третий регистры 16 и т В Соответствии с заправляющими сигналами из хронизатора 58 блок 15 может функционировать в двух режимах считывания: с регенерадаей и без регенерации, при котором в момент считывания ключ 17 закрывается. По окончаьши второго режима счи тывания блок 15 памяти готов к обработке следующих сигналов. Пороговый блок 18 преобразует входные двоичные -разрядные кодо вые комбинации в одну из двух выходных 9 -разрядньк кодовых комбинаций; нулевую или единичную. Он содержит ключ 20 и l -разрядный двоичный регистр 19 сдвига. Так ка вход последнего соединен с его же выходом, то регистр 19 представляе собой генератор двоичных сигналов 1, т.е. в его ячейки всегда запи саны 1, На двоичньй регистр 19 подаются импульсы -считывания синхр но с импульсами первого считывания из блока 15, Следовательно в соответствуюцще моменты времени на информационный вход ключа 20 будут йоступать двоичные символы , --- На управляющий вход ключа 20 с выхода блока 15 памяти старшими ра рядами вперед последовательно пост пают -9 -разрядные двоичные комбина ции. Старший разряд каждой такой комбинации управляет состоянием ключа 20, При этом указанное состояние сохраняется на время считывания остальных разрядов, следующих после старшего. Пусть, напритче .в первой -) -разрядной двоичной ком бинации старший разряд - единичный Тогда ключ 20 своего открытого в исходном состоянии положения не из меняет и пропускает на выход порог ,арго блока 18 -разрядную единичную двоичную кодовую комбинацию. Пусть- во второй, следующей за первой, двоичной- комбинации старщий разряд - нулевой, В этом случае ключ 20 закры1вается на время 9 так тов, после чего опять открывается; и т,д. Очевидно, что во втором при мере на выходеблока 18 будет присутствовать нулевая -разрядная ,двоичная кодовая комбинация. Таким образом, входные кодовые комбинации пороговый блок 18 преобразует 16i2 в зависимости от состояния lix старшего разряда или в единичную, или в нулевую выходные двоичные кодовые комбинации, . Вьгчитатель 21 предназначен для вычитания из величины, представленной в двоичном коде соответствзтощей выходной комбинации блока 15 памяти, величины, представленнойсоответст-. вующей двоичной кодовой комбинацией навыходе блока 18. Перед преобразованием двоичные коды с п.омощьк преоб- разователей 22 и 23 представляются, в двоично-десятичной системе счисления, в которой с помощью элемента 24 вычитания осуществляется вычисление разности указанных величин. Сумматор суммирует выходной вычитателя 21 с выходным сигналом блока 15. Для этого выходной сигнал блока 15 памяти с помощью преобразователя 26 представляется в двоично-десятичной системе счисления И подается на вход элемёнта 27 . сложегшя, , Пороговьш блок 28 преобразует входной сигнал в один из сигналов О .или /П - 1. Источник 29 и аттенюатор 30 формируют опорный импульс постоянного тока, амплитуда которого равна №/2. Если входной сигнал по амплитуде не меньше величины порогового напряжения, то на выходе блока 28 формируется сигнал .т - 1, В п-ротив- ном случае - сигнал 0. Декодер 33 отождествляет входные двоичнЕ-.1е кодовые комбинации с выход- HbiMii разрешенными кодовыми комбинациями . Блок 35 памяти предназначен для хранения двух разрешенных кодовых комбршаций, вьщачи их в блок 45 и / , считывания одной из них на вьпсод устройства. В соответствующие момен- ты времени на регистры 38 и 39 подаются импульсы записи. С их.: помощью первая выходная двоичная кодовая комбинация декодера 33 через элемент 36 ИЛИ записывается в регистр 38. Потом вторал выходная комбинация декодера 33 записывается в. регистр 38, сдвигая первую комбинацию в регистр 39..Далее по сигналу от хро- низатора 58 открывается к/тюч 40, а на регистры 38 и 39 подаются импульсы считьшаний. Coдepжи юe регистра 38 считывается на соответствуюпдай выход блока 35 -и одновременно пере13писывается в регистр 39. Содержимое этого регистра 3-9 выдается на выход блока 35 И через открытый в это вре мя ключ 40 переписывается /в регистр 38, После этого ключ 40 закрывается В определенньш момент времени на счетный вход триггера 37 подается сигнал. Если он единичный, то триггер 37 меняет свое состояние, если нулевой, то триггер 37 своего Состо ния не меняет. В это же время откры вается ключ 41. Если состояние триг гера 37 является нулевым, то открывается ключ 42, в противном &лучае ключ 43. После этого на регистры 38 и 39 подаются импульсы считывания и на выход устройства через ключ 42, или через ключ 43 и элемент 44 liFIH считывается одна из разрешен ных кодовых комбинаций. Триггер 37 устанавливается в исходное состояние. -Регистры 38 и 39 сбрасываются по сигналу Общий сброс, формируе. в хронизаторе 58. Блок 45 управления вьщачей информации предназначен для вычисления степени близости (коэффициента кбрреляции) между двоичной кодовой комбинацией блока 15 памяти и разрешенными кодовыми комбинациями блока 35 памяти, а также для формирования управляющего сигнала для блока 35. В момент времени, определяемый управляющими сигналами хрони затора, на один вход блока 45 по дается двоичная кодовая комбинация блока 15 памяти, на другие - разрешенные дзоичные кодовые комбинации от блока 35. С помощью цр.еобразователя 56 входная двоичная кодовая комбинация преобразуется в .двоично-десятич ную. Этот сигнал подается на входы ключей 46-49 одновременно с соответствующими символами разрешенных комбинаций. Последние коммутируют ключи 46-49. При этом двоично-десятичные символы .через соответствуклди .ключ 46 или 45, а также 48 или 49 поступают на соответствующие сумма торы 50-53. Выходные сигна ш сумматоров 50 и 52 - положительные, а выходные сигналы сумматоров 51 и 53 - отрицательные. На выходе сумма тора 54 после считывания всех симво лов указанных комбинаций формируется сигнал, соответствующий степени близости между составным сигналом 16.14 блока 15 и второй разрешенной крм бинацией. Соответственно выходной сигнал сумматора 55 определяет степень близости между составным сигналом и первой разрешенной комбинацией . Сигналы сумматоров 54 и 55 вычитаются в вычитателе 57. Положительный выходной сигнал вьгчитателя 57 .. служит для блока 35 в качестве.единичного управляющего состоянием . триггера 37 сигнала, а отрицательный сигнал - соответственно в качестве нулёвого управляющего сигнала. Обнуляются сумматоры 50-55 по сигналу Общий сброс из хронизатора 58. Регистр 32 сдвига предназначен для хранения выходной двоичной кодовой комбинации блока 28 на время, в течение которого в декодере 33 осуществляется преобразование выход-ной двоичной комбинации блока 18. Сигналы записи и считывания подаются с соответствукщего вькода хронизатора 58. В хронизаторе 58 с помощью формирователя. 59 импульсов осуществляется тактовая и блочная синхронизация. Формирователи тактовых импульсов содержат триггеры 75, разрешающие работу генераторов 77 импульсов определенной частоты следования. Сопряжение соответствующих входов блоков устройства и управляющих сигналов, формируемых- .в различные моменты времени, осзпцествляется с помощью элементов 68,.78-80 ИЛИ. .В качестве примера, поясняющего алгоритм функционирования предлагаемого устройства, рассмотрим его работу при следующих параметрах. Пусть на передающей стороне составной сигнал с избыточностью сформирован на основе двоичной кодовой комбинации У (0110101). Если бы в канале связи-не было помех, то на выходе преобразователи при количесфве зон Квантования, равньк 8, бьша сформирована следующая совокупность трехзначньш двоичных кодовых комбинаций: 000, 111, 111, 000, 111, 000, 111. Эта совокупность, определяет сигнал точную оценку избыточного сигнала. Характеристики кода следующие: длина кодовой комбинации п 7, количество информационных символов К 3, минимальное кодовое расстоя.Ние J 4 (следовательно, кратность двоичных ошибок, исправляемхлК декод ром 9, равна i 1), Используемый код состоит из следующих разрешенш. .кодовых комбинаций: 0000000, 001101 .0101110, 0110101, 1001101, 1010110, 1100011, 1111000. СложньпЧ избыточный сигнал, искакенный в канале связи помехами, с помощью квантователя 1 преобразуетс в совокупность импульсов с различной амплитудой. Величина амплитуды Каждого такого импульса с помощью преобразователя 8 преобразуется в 9 3-значную двоичную кодовую комбинацию. Совокупность из h таких комбинаций запоминается в блоке 15 памяти и соответствует сигнальной точке X (фиг, 3 д ). Пусть указанная совокупность, (сигнал Х) имеет вид: ,X (100, 010, 011, 000, 111, 000, 111). Посимвольная обработка составног сигнала X в блоке 18 после его записи и считывания с рвгеиерацией ,из блока 15 приводит к сигналу 1(-фиг. 3 д) Xf (111, 000, 000, 000 111, Out), 111). Двоичный составной сигнал Xg-подается в декодер 33, в котором отождествляется с ближайшей раз решенной кодовой комбинацией (фиг . Зд) Xj (7007707). Символы этой комбина11Ии на выходе декодера 33 представляются импульсами постоя Hoio тока с амплитудами, определяемыми величинами проекций сигнала Х - соответственно они равны 7В, ОВ, ОБ, 7В, 7В, ОВ, 7В. Сигнал Х з поминается в регистре 38 блока 35, Одновременно с комбинацией X поступает на вход вычитателя 21. На вЬкоде последнего образуется сигнал (фиг, Зд) ХХ5. X - Xj- (-3, 2, 3, О, О, О, 0), который в сумматоре 25 суммируют с. сигналом X. В резуль тате послучают сигнал Х 1, 4, 6, О, 7, О, 7, Его с помощью блока 8. преобразуют в двоичный сигнал Х, (О, 7, 7, О, 7, О, 7), который в данном примере оказывается ранньм 6 сигналу Х, т.е. Xj есть Х. Элe feйтарные сигналы, входящие в состав X,, накапливаясь, запоминаются в регистре 32 сдвига. В соответствующий момент времени сигнал считывается из регистра 32 в декодер 33, в котором отождествляется с ближайшей разрешенной двоичной кодовой комбинацией, но так как и является х. разрешенной комбинацией, то второй выходной разрешенной двоичной коде- вой комбинацией на выходе декодера 33 будет являться Х З, Она, как и первая, запоминается в блоке 35, После этого разрешенные комбинации Xj и Х( из блока 35 и комбинация X из блока 15 подаются в блок 45, где вычисляются степени близости X и Х| (соответствзпощий , коэффициент корреляции равен 17) и . между. X и Х (коэффициент корреляции равен 13), На основе анализа разности степеней близости из блока 35 на выход устройства считывают разрешенную двоичную кодовую комбинацию Х|, Подается сигнал Общий сброс и устройство готово к обр.а- ботке следующего составного избыточ ного сигнала, Полученньп результат тот же, что и получаемьй с помощью известного устройства, но достигается он алгоритмически значительно проще. Пред.лагаемое устройство для гра-. диентного декодирования в целом двоичных избыточных кодов обладает более высокими технико-экономическими пoкaзaтeля и по сравнению с известным, Техническое преимущество предлагаемого устройства заключается в том, что в нем отсутствуют два блока: блок памяти и блок сдвига, обусавливающие большое количество one- аций при формировании второй грубой ценки (сигнала Х) срставв ого изыточного сигнала. Последнее приодит к уменьшению времени выполнеия элементарных операций.

-рШЧЕ

ь

h

7 ч.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бородин Л.Ф | |||

| Введение в теорию помехоустойчивого кодирования | |||

| М., Советское радио, 1968, с | |||

| Приспособление для уменьшения дымовой тяги паровоза | 1920 |

|

SU270A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 801760, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-04-23—Публикация

1983-11-24—Подача